阵列存储在遥测图像采集系统中的应用

孟令军,彭晴晴,蔺志强

(中北大学 电子测试技术国家重点实验室,山西 太原 030051)

0 引言

随着图像采集器件性能的提高,图像的采集速率和信息量也在不断增加[1],同时,由于LVDS技术在图像数据传输中的广泛应用,图像数据的实时处理和下传已经成为图像采集系统中非常关键的部分[2]。以SRAM阵列的存储方式可以有效地缓解图像数据的传输速率,为CPU进行图像数据处理争取了大量时间,并保证了稳定下传。本文以微处理器为核心,用FPGA控制SRAM阵列进行存储和下传,CPU负责阵列存储区的管理和可靠稳定的记录数据,完成图像数据在阵列中的分布存储。

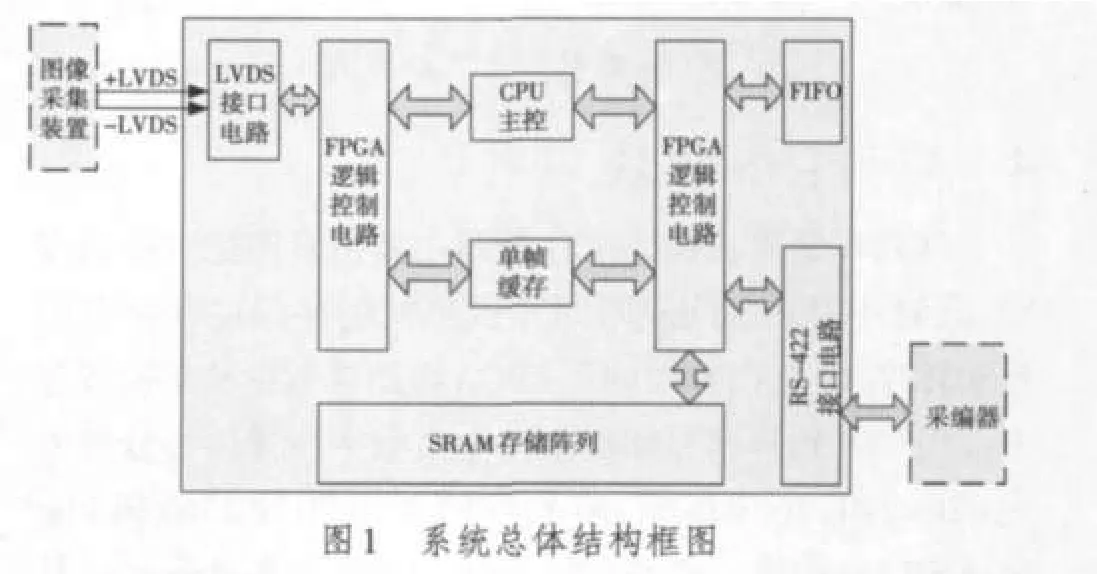

1 系统总体结构

图像数据采集系统主要负责实时接收图像采集装置的高速图像数据,同时将数据连续串行下发给采编器。本文以CPU处理器为核心,主要控制系统的总体工作流程,同时以FPGA或CPLD为辅助,完成系统各模块与处理器之间的通信,实现图像数据的分区存储和连续下发。基于嵌入式处理器的图像存储系统硬件电路采用CPU+FPGA器件进行时序控制,遥测图像数据首先通过LVDS接口芯片将串行数据解串为并行数据,存入单帧缓存中(由1片SRAM构成)。由于图像数据发送速率和接收速率之间存在差距,为了保证20幅图像数据的有效接收,主存储器使用20片SRAM构成存储阵列以实现20帧图像数据的有效存储。CPU是整个系统的中心控制器,负责控制图像数据的接收和转发编码。FPGA主要负责依据CPU的控制信号接收图像数据存至单帧缓存,转存至存储阵列和以PCM码形式转发至采编器。为了保证转发数据的无缝传输,在转发时使用FIFO进行缓存。本设计总体结构如图1所示,主要包括7个部分:LVDS接口电路、FPGA数据处理模块、单帧缓存读写模块、CPU控制模块、主存储阵列、FIFO缓存模块以及RS-422接口电路。

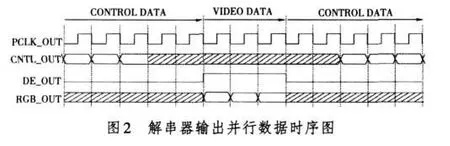

2 LVDS接口模块

LVDS技术以其低误码、低功耗和高传输速度等优点而广泛应用于图像数据的高速传输中,可以实现一对多或者一对一传输[3]。本文采用点对点的数据传输方式,使用专门的LVDS串化/解串芯片,相同的串化/解串时钟频率控制,保证数据的同步传输。LVDS解串器完成LVDS电平到TTL电平的转换,实现图像帧、行同步信号与图像数据的分离和输出,并输入到FPGA中进行处理。图像数据是在帧同步信号VSYN为高电平时有效,故将帧同步信号VSYN与数据使能信号DE_IN连接,在帧同步信号VSYN有效时,解串芯片输出DE_OUT,有效输出16位图像数据及控制信号。并行数据输出时序如图2所示。

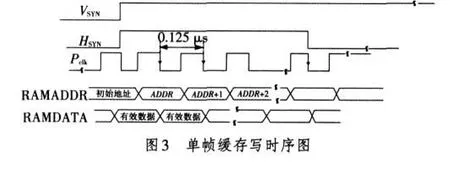

3 单帧缓存模块

由于图像数据传输速率远大于主存储设备的存储速度,并且在数据转存的同时还要对每帧图像数据进行编码,因此为了实现接收和转发数据流之间的速度匹配,需要在主存储器之前使用缓存,并且要在下一帧数据到来之前将数据转存,以保证图像数据的无缝缓存[4]。本文选用1片SRAM构成单帧缓存,在帧同步VSYN和行同步HSYN同时为高时,SRAM写地址跟据PCLK的上升沿递推,PCLK低电平时将数据写入SRAM中缓存,时序如图3所示。

4 阵列存储模块

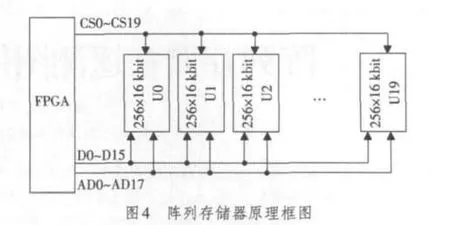

阵列存储模块作为主存储器主要负责图像数据的存储,同时还要在帧间隔时间完成单帧缓存到主存储器的自动转存,即在CPU控制下FPGA将图像数据从单帧缓存中读出写入到阵列存储器中。本文数字图像信号分辨力为320×240,16位模式;阵列存储器由20片256×16 kbit高速SRAM构成。阵列存储模块的原理如图4所示。其中共用16位数据线和18位地址线,采用独立片选线。

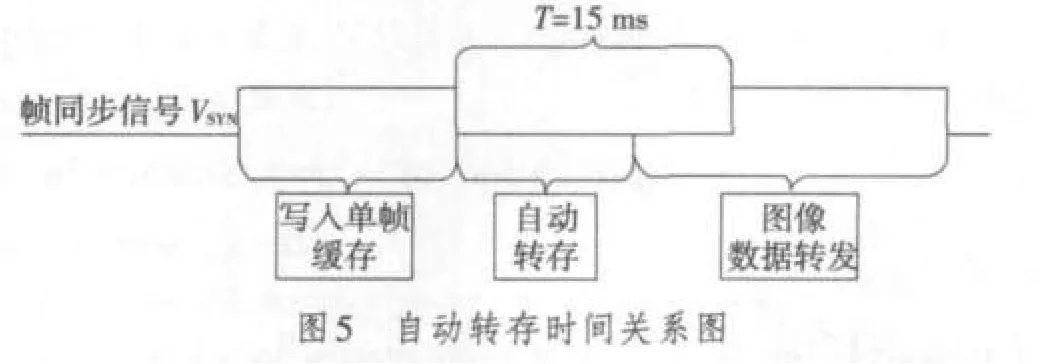

自动转存能否成功进行是整个系统的关键部分。如图5所示,两帧间的间隔决定了自动缓存时间。图像数据在VSYN为高时写入单帧缓存中,为低时开始图像数据的自动转存。依据设计需要,两帧间的最小间隔为15 ms,所以用于自动转存的时间必须小于15 ms。

自动转存一帧的图像数据量约为(320×240×2)bit=153.6 kbit,由此可得出自动转存最小理论频率为[0.015/(320×240)]-1Hz≈5 MHz。实际操作时,要留有一定的后操作时间,本文确定的转存时钟为8 MHz,写入阵列存储器一帧图像的时间约为(320×240/(8×106))s=9.6 ms。因此,根据计算有足够的时间将单帧缓存中的图像数据转存入阵列存储器中。

5 PCM编码模块

PCM码是无线遥测系统中常用的一种编码过程,本系统由采编器提供码同步(YCK)和字同步(YZM)信号,将并行图像数据编码输出为串行PCM码流。在YZM变为高电平时,系统在YCK的上升沿输出一个图像数据位,每个图像数据字节用8个YCK输出。在读主存储器之前,CPU首先向FIFO写入帧头和帧计数,然后CPU控制FPGA读取图像数据写入FIFO,最后依据YCK和YZM信号从FIFO中读出数据进行PCM编码,以60 kbyte/s的速率通过RS-422接口下发给采编器。

6 系统调试结果

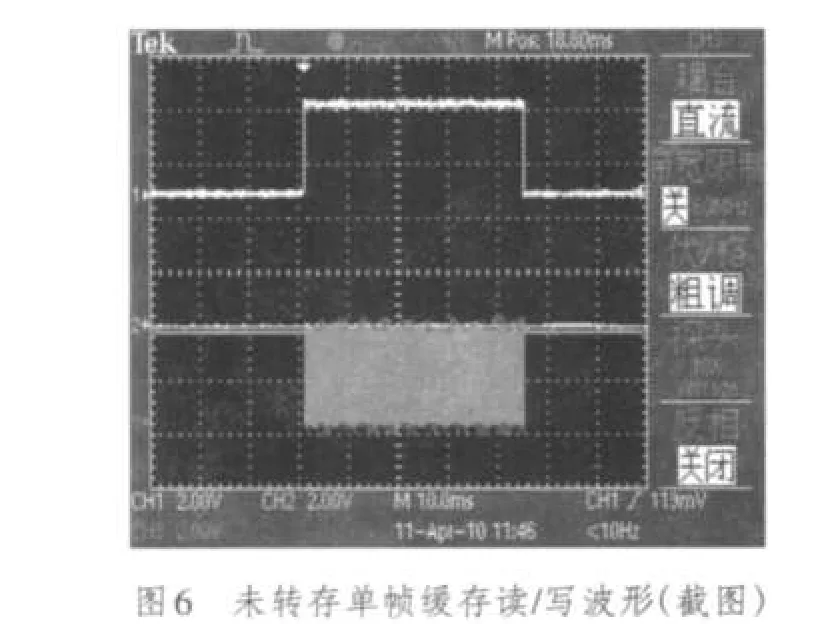

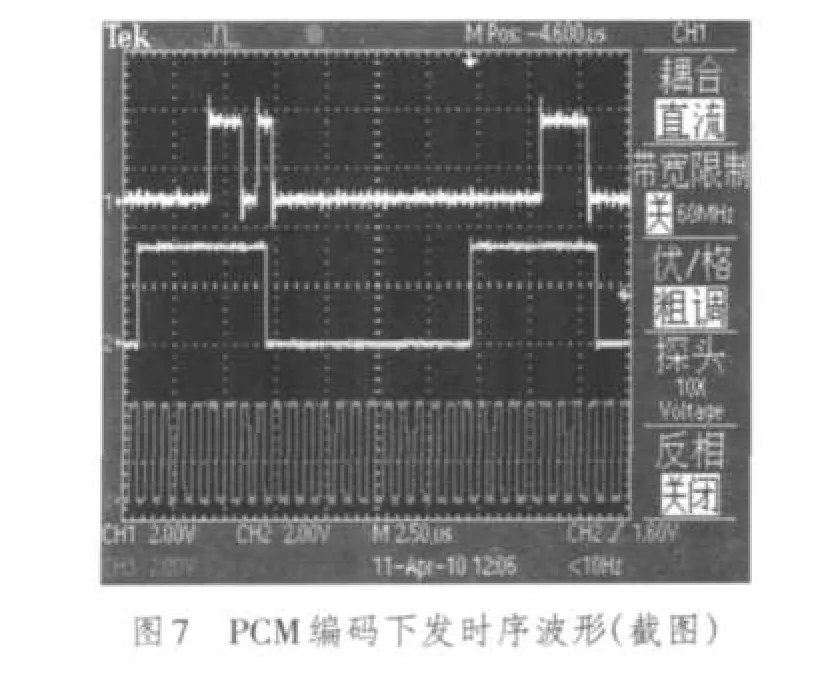

图6为初始20帧的单帧缓存状态,CH1为图像数据的帧同步信号,CH2为写单帧缓存信号。在阵列存储器没写满时,图像数据先存入单帧缓存,然后自动转存到阵列存储器。编码测试如图7所示,FIFO中读出的图像数据在YZM为高时进行PCM编码,CH1为编码数据YDT,CH2为字同步YZM,CH3为码同步YCK,图中下发的YDT为0x0D和0x0E。

7 小结

本文利用CPU+FPGA的组合设计方法,实现了遥测图像数据的无缝缓存,完成图像数据的PCM方式串行下传。设计中采用单帧缓存和阵列存储的数据处理方式,并对图像数据自动转存的关键参数进行了详细的分析,针对系统的功能进行了实际测试,测试结果表明阵列存储可以高速有效地缓存图像数据。

[1]孙榕,刘峰.高清视频编解码芯片选型及压存系统的设计[J].电视技术,2007,31(11):26-28.

[2]蔡波.视频实时图像处理系统研究及设计[J].电视技术,2005,29(5):23-25.

[3]孙春凤,袁峰,丁振良,等.基于LVDS技术的高速图像采集系统的设计[J].仪表技术与传感器,2009(3):46-48.

[4]张国兵.基于LVDS的图像存储转发装置的设计与实现[D].太原:中北大学,2010.