多通道数字脉冲发生器的SoPC实现

龚 敬,孟令军,严 帅,尹维汉

(中北大学 仪器科学与动态测试教育部重点实验室 电子测试技术国家重点实验室,山西 太原 030051)

0 引言

片上可编程系统(System on Programmable Chip,SoPC)是Altera公司提出的一种灵活、高效的SoC解决方案,将处理器、缓存、存储器、I/O口、高速总线等系统设计需要的功能模块集成到一个FPGA器件上,构成一个可编程的片上系统[1]。采用SoPC技术可以大大提高系统运行速度,缩小尺寸,降低总体系统成本,克服多芯片集成系统设计所产生的一些困难,通过提高芯片集成的系统功能以获得更高的系统性能,减少电路板面积,降低制造成本。本文采用的方法充分利用了SoPC的特性和优势,合理地选择所需处理器和外设接口控制模块,既保证了处理速度,又最大程度地降低了系统成本。

1 工作原理

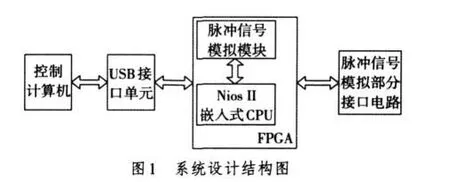

本文采用基于大规模FPGA的嵌入式系统设计,硬件上主要由控制计算机、USB接口单元、FPGA和外围接口电路等部分组成。软件上,Nios II主控制软件采用C语言设计,部分外围逻辑模块使用VHDL程序设计,该设计的模块功能划分清楚明确,并且各个功能模块之间的耦合性极小,因此模块可以实现切割测试,整个系统整合后可以达到较高的可靠性,缩短了开发周期。系统的结构框图如图1所示。

系统主控器件为一个基于FPGA的32位嵌入式CPU系统,由Altera公司的EP2C35和SRAM等芯片构成,各功能模块在它的控制下协同工作。其中嵌入式CPU是一个Nios II内核,它与外设控制接口、核外逻辑单元构成一个完整的SoPC系统,处理器根据需要添加各种嵌入式外设,可以较为容易地在硬件方面实现对系统外设的管理,控制计算机与脉冲发生器之间的数据通信则由一个USB接口单元实现。

2 系统实现

本文包括硬件电路设计、SoPC系统搭建和Nios II软件设计3个层次。

2.1 硬件实现

系统主要由EP2C35,SRAM,EPCS等芯片和相应的外围接口电路构成。

2.1.1 主机与各功能部分之间的通信

脉冲发生器由USB接口单元与主机连接,以FPGA作为控制中心,通过USB接口单元实现FPGA与计算机之间的数据通信。USB接口单元采用FT245芯片,可以实现计算机与FPGA芯片之间的并行通信,最大传输速度可达到1 Mbyte/s。

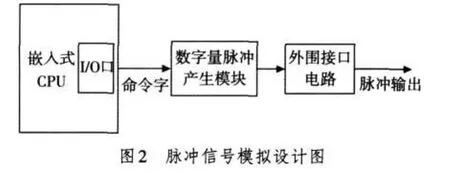

2.1.2 脉冲信号模拟模块

脉冲信号模拟部分主要产生各种特定的数字脉冲信号,包括4种脉冲波形:第1种为72位不归零码,共1路,它在中断信号和移位脉冲信号的时序控制下按位输出固定数码,可以手动设置输出,默认状态为01,23,45,67,89,AB,CD,EF,0F,其中中断信号频率为40 Hz,脉宽为7 ms,移位脉冲是周期为12 μs,8位一组,每组间隔96 μs的信号;第2种为特定频率的规则脉冲信号,共1路,频率为256 kHz,占空比50%,需产生的脉冲个数范围为0~216个;第3种为特定频率的不规则脉冲信号,共2路,每路均包括两通道脉冲信号,频率为500 Hz,脉冲宽度为6 μs,两通道脉冲信号间时间间隔为0.5 μs的整数倍,最大为1 ms,发送脉冲的个数范围为0~216个;第4种为可变频率的不规则脉冲信号,共6路,频率为1~75 kHz,平均分为6挡,脉冲宽度为2 μs,发送脉冲个数范围为0~224个。可以通过计算机软件实时修改各种输出脉冲信号的路数、频率和个数。图2为脉冲信号模拟模块原理框图。

计算机软件根据设置产生相应个数和频率参数的各路脉冲信号,并通过以下步骤实现脉冲信号输出:1)通过USB接口单元向脉冲信号模拟模块发送复位指令,复位FPGA;2)计算机通过USB接口单元发送脉冲参数,FPGA接收并暂存入一数组中,经校验无误后,通过Nios II内核相应的I/O口输出脉冲参数给相应的脉冲产生模块,各数字量脉冲产生模块输出相应的脉冲信号。如果与发送的参数不一致,则需要向上位机返回重发命令请求,重新执行步骤1)~2)。

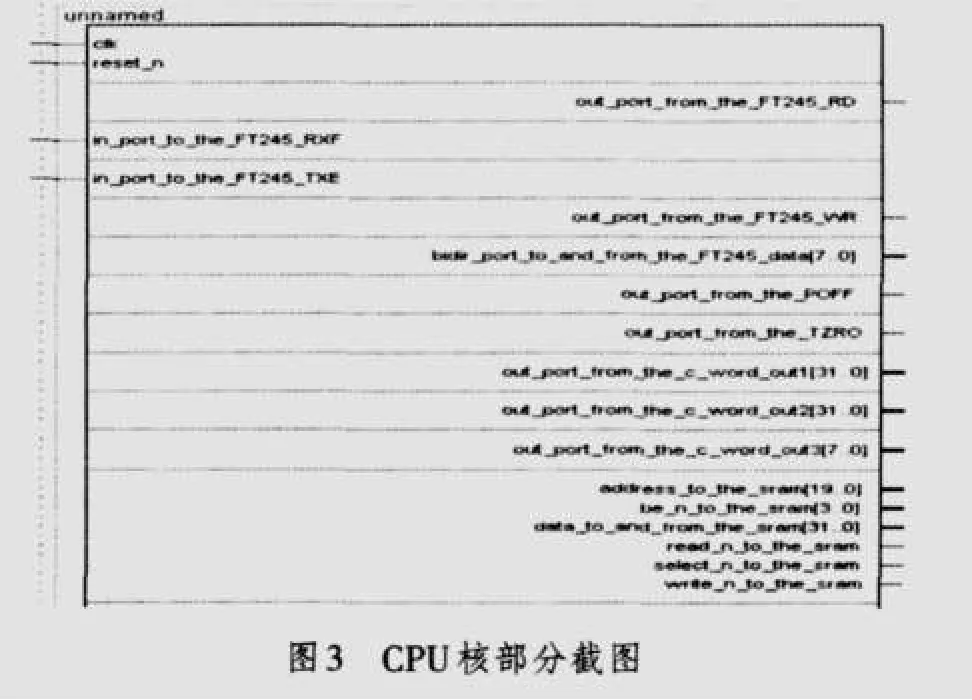

2.2 SoPC系统搭建

Nios II嵌入式内核是系统的核心模块,包括CPU核、JTAG控制接口、EPCS控制接口以及与外围模块进行数据通信的I/O控制接口,为了满足程序代码存储特性的需求,存储器采用EPCS16和SRAM芯片。图3是CPU模块的部分截图,其中包括部分芯片与FT245通信的I/O控制接口和SRAM控制接口。

2.3 Nios II主程序

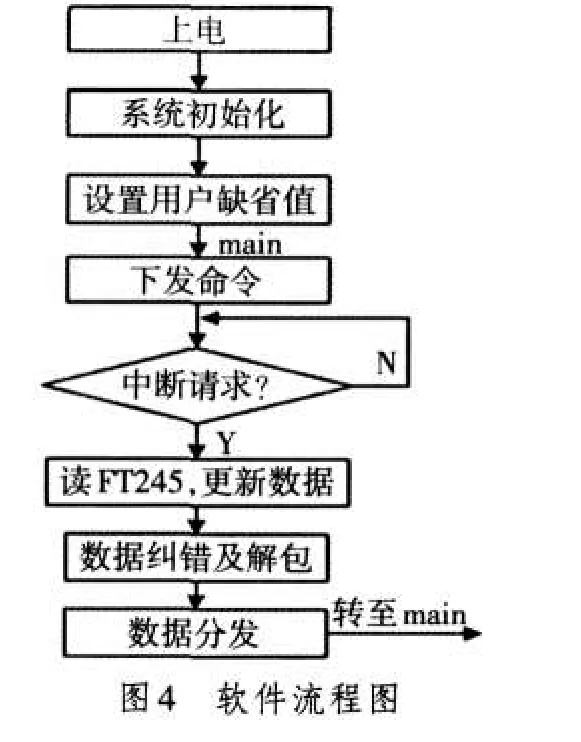

系统的主程序采用C语言设计。相比VHDL语言来说,代码更优化、系统更方便维护和升级。主程序的流程是:上电后系统进行初始化,在上位机界面设置好各参数值后,参数值以数据包的形式下发至FT245,并暂时存储至FT245内部的缓存器中。程序进入等中断请求的状态,如果没有中断请求信号到来则继续等待,如果有中断请求到来则读FT245中的数据并将其存储至一数组中进行数据校验、解包,解包后的数据如正确无误则下发至CPU核各I/O端口,从而控制其相应的数字脉冲产生模块产生所需数字脉冲信号。数据分发完成后再次进入等待命令的状态,如此循环进行。流程如图4所示。

3 上位机控制软件

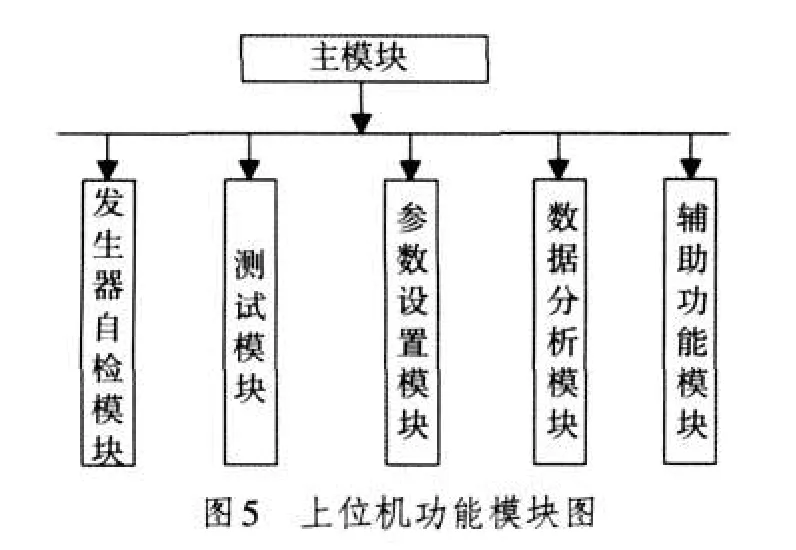

上位机软件是数字信号发生器的主控软件及数据处理软件。该软件主要实现地面计算机与信号发生器之间的通信、数据传输、实时显示、接口检测、信号发生器工作状态检测及数据处理等功能,是实现人机对话的中间媒介。本软件采用VB进行设计,可以在Windows 7/XP操作系统上运行。图5是上位机软件的功能模块图。

4 系统测试结果

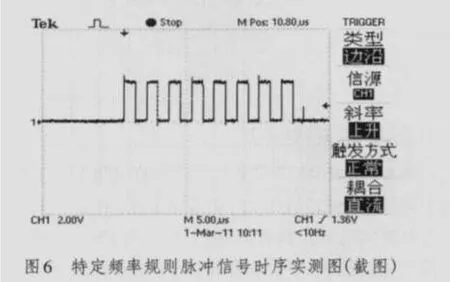

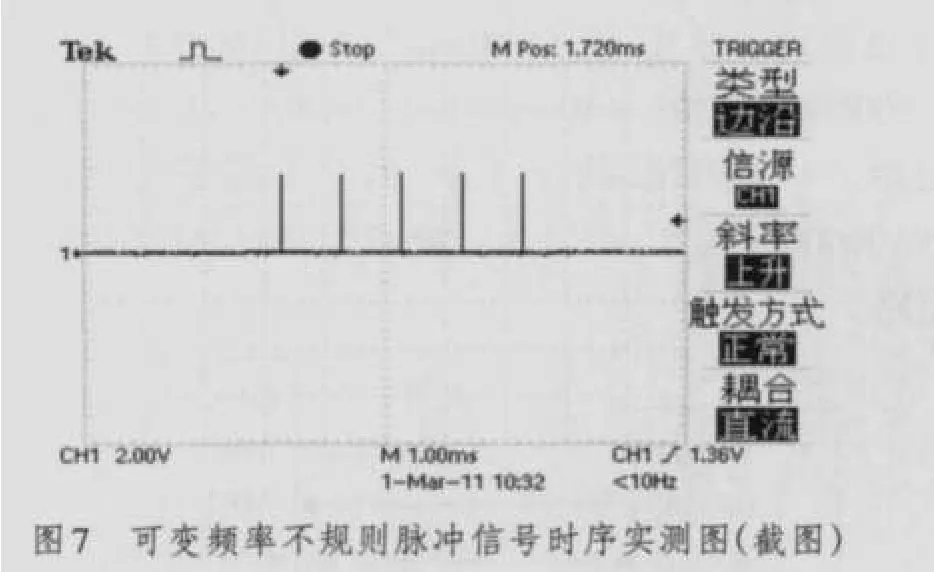

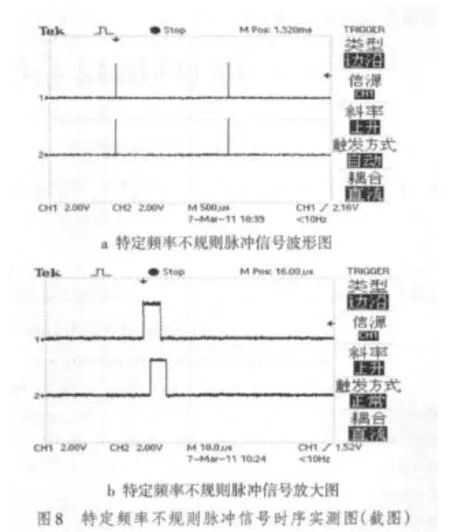

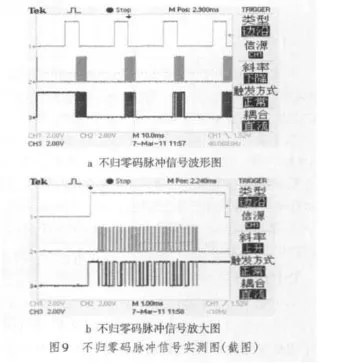

本系统经过实际测试后,各项功能指标均满足任务要求。图6为脉冲信号模拟模块产生的1路特定频率规则脉冲信号,其中上位机软件中的个数设置为8个。图7为可变频率不规则脉冲信号,其中个数设置为5个,频率为1 kHz。图8为特定频率不规则脉冲信号,两脉冲信号的时间间隔设置为1.5 μs,个数为2个。图9为不归零码测试波形,其中CH1为中断信号,CH2为移位脉冲信号,CH3不归零码信号。

经过测试和试验,完全满足各项指标要求。各脉冲信号精度要求以及达标情况见表1。

5 小结

本系统采用SoPC技术,利用Nios II嵌入式软核CPU软硬件系统可编程及可在线调试的优点,将所需模块控制接口集成至Nios II处理器系统中。根据上位机下发的不同命令来产生不同频率和个数的数字脉冲信号,通过示波器观察所产生的各种脉冲信号,满足了系统设计要求,实现了可选通道、可变频率和个数可控数字脉冲信号的产生。

表1 精度参数要求

[1]SOPC(片上可编程系统)灵活、高效的解决之道[EB/OL].[2010-08-06].http://www.dianzi9.cn/SOPC/200808/12-6483.html.

[2]倪亮,吴丽敏,赵鹏飞.基于SOPC基本信号产生器的设计与实现[J].电子科技,2011,24(1):89-92.

[3]周立功.SOPC嵌入式系统基础教程[M].北京:北京航天航空大学出版社,2006.

[4]张拥军,赵雪峰,朱维乐.基于FPGA平台的DVB-T发射端的实现[J].电视技术,2004,28(11):61-63.