光电跟踪系统控制器硬件设计

徐晓霞

(西安工业大学北方信息工程学院 电子信息系,陕西 西安 710025)

现代战争的特点是高技术、多方位、立体、全天候作战。陆、海、空的协调统一是致胜的关键。尤其是空中侦察作战的优势显得越来越重要。因此,作为侦察、测量和校射及打击效果评估的重要手段,光电跟踪测量设备日益受到重视,各国竞相研制。由于现代武器技术的发展,将靶场测量设备应用到飞机上是当前光电跟踪测量系统的新发展。光电跟踪测量系统可完成对地面、空中目标的搜索、扑获、锁定、跟踪和瞄准,并将飞机相对目标的方位、俯仰、距离等信息进行记录处理。它可应用到常规武器靶场、机载光电侦察、机载光电火控等领域。光电跟踪系统是一种利用光电传感器如前视红外、激光、电视、微光、可见光等对地面目标进行搜索、识别、跟踪和瞄准的机载目标探测设备。文中对光电跟踪系统控制器的硬件部分进行了设计。主要包括光电跟踪系统控制器硬件电路框图,最小控制系统设计,模拟、数字量模块和通信模块设计等部分。

1 光电跟踪系统控制器硬件电路框图

CPU和信号检测与解码电路供电。测量元件测得当前方位和俯仰位置,由信号检测与解码电路板将位置信号转换成模拟信号送给CPU。CPU将这些信号进行处理,得出需要追加的方位角和高低角,并将这两路控制信号送给方位力矩电机和俯仰力矩电机。CPU与上位机之间采用RS232协议进行通讯。

图1 光电跟踪系统电路结构框图Fig.1 Circuit block diagram of optical tracking system

2 最小系统设计

光电跟踪系统的电路结构如图1所示,由电源电路板给

在ERT模块中,除了核心处理器F2812外,其余外围器件还有:5 V 转 3.3 V、3.3 V 转 1.9 集成电源,10MHz的晶振,外扩RAM,JTAG以及看门狗电路复位电路等。其结构示意图如图2所示。

图2 最小系统的电路结构框图Fig.2 Circuit block diagram of theminimum system

最小系统电路的主要工作过程是,由时钟电路产生时钟周期,构成机器产生动作的机器周期。CPU对从外部采集来的数据进行分析,并发出命令。JTAG接口提供了简单灵活的调试手段,用户可以通过JTAG接口,将在 PC交叉编译生成的结果下载到DSP中,或者通过JTAG接口即时查看DSP内部寄存器和RAM的值,对程序的行为进行调试。当程序跑飞时,看门狗复位电路可以使系统回到初始状态。

TMS320F2812最小系统原理主要包括存储器扩展,外部时钟,复位电路,电源电路,CPU板的抗干扰分析与设计,下面将对各部分做出详细介绍 。

2.1 存储器扩展

F2812采用32位的寻址方式,数据空间和程序空间统一编址。F2812有1 056 K×16 bit的外部存储器接口能力,分为5个地址区间:区间0、区间1、区间 2、区间6和区间 7,各空间均可独立设置读、写信号的建立时间、激活时间及保持时间。其中区间6、7共用一个片选引脚 XZCS6AND7。

F2812内部已经集成了18 kB的RAM,对于一般的应用来说,已经无须再扩展外部RAM。片内RAM能以150MIPS的速度进行访问。在对运算速度要求很高的处理程序中,通常将经常访问的程序段放到内部RAM中运行,这样能大大提高运行速度,因此片内RAM显得格外宝贵。而且本系统是一个汇流条功率控制系统,将来会用于进行处理大量数据,因而也要求外括RAM用于存放数据。本系统扩展了512 kB SARAM,芯片选用 IS61LV51216 (512 k×16 位),其数据访问时间为10 ns片选信号为片选信号为XZCS6AND7,当MP/MC端置高电平时工作在MC模式,映射到存储空间7,当MP/MC端置低电平时,映射到存储空间6。

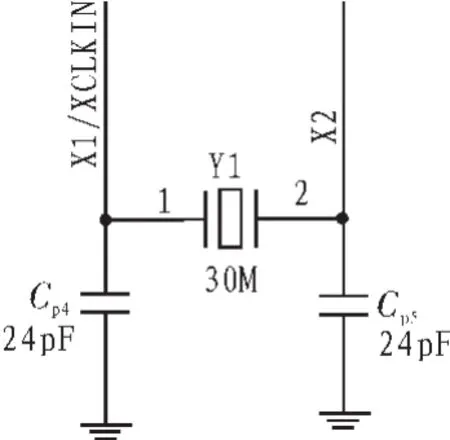

2.2 时钟电路

F2812具有内部锁相环电路,可以从一个较低的外部时钟通过锁相环倍频电路实现内部倍频。这对于整个电路板的电磁兼容性是很有好处的,因为外部只需要使用较低频率的晶振,避免外部电路干扰时钟,同时也避免了高频时钟干扰板上其它电路。

本系统选用30MHz外部晶体给F2812提供时钟,并使用F2812片上PLL电路。PLL倍频系数由PLL控制寄存器PLLCR的低 4位控制,可由软件动态地修改,外部复位信号(XRS)将此 4位控制位被清为 0。F2812的 CPU最高可工作在150MHz主频下,也即对 30MHz输入频率进行 5倍频。晶体电路最为简单,只需晶体和两个电容。

图3 扩展RAM原理图Fig.3 Extended RAM schematic

图4 时钟电路图Fig.4 Clock circuit diagram

2.3 手动复位电路

为了避免不可预知的错误,可以手动给CPU提供复位信号,使系统终止当前所有操作,使CPU进入已知的初始状态,刷新所有的流水线操作,复位所有的CPU寄存器,复位相关的信号的状态。

该系统可以通过硬件和软件进行复位,任何一个复位都有效,都将导致系统复位。软件复位主要是通过F2812片上的看门狗计数器产生复位脉冲实现的。手动复位的过程如下:F2812的复位端第160脚XRS是低电平有效,当它是低电平的时候才能复位。SP1按下的时候,XRS为低电平,F2812复位。同时CP1通过SP1的回路进行充电,XRS端达到高电平,复位结束。在这个电路中,电容有充电,提供了可靠复位的有效时间。

2.4 电源电路

电源电路的选择是系统设计的一个重要部分,设计好坏对系统影响很大。对于F2812芯片而言,一般有以下2种电压需要电源电路提供:一种是DSPCPU内核电压。现代DSP为了省电,通常把内核电压和外围电路的供电分开,内核工作于低电压减少功耗,外围电路与其它器件采用相同的电压规范。另一种是DSP外设电压。主要给DSP的片内外设供电。

图5 复位电路原理图Fig.5 Reset circuit schematic

首先需要注意的是,为了减少电源噪声和互相干扰,数字电路和模拟电路一般要独立供电,数字地和模拟地也要分开,并最终通过一个磁珠在一点连在一起。

本系统选用 asm1117-5、asm1117-3.3、asm1117-1.9, 输出电压分别是 5 V、3.3 V、1.9 V, 连接电路如图 6 所示,电路为 F2812提供 3.3 V和1.9 V的工作电压,为通信模块提供5 V的电压。考虑到很多应用系统需要供很多不同的电压,如很多DSP本身就需要分内核和外围电路,此时就需要考虑一个上电次序问题。一般来说,CPU内核先于外围上电,后于外围掉电;但是两者相差不能太大,否则将损坏芯片。

图6 电源转换电路原理图Fig.6 Power conversion circuit schematic

2.5 CPU板的抗干扰分析与设计

为了更有效防止干扰,在设计CPU板的时候采用了4层板设计,上层放置芯片,第2层放置完整的地面,第3层放置电源,下层放置电阻电容。相比普通得两层板增加了GROUND层和POWER层,GROUND层将模拟地与数字地进行隔离,最后用磁珠相连。POWER层把5 V,3 V,1.9 V的电源分开。最后将焊盘连接处修改为泪滴连接使焊盘连线的强度增强。

图7 模拟地与数字地隔离电路图Fig.7 Analog ground and digital ground isolation circuit diagram

3 模拟量和数字量模块设计

调理电路应具备的基本功能有:降压,将信号的幅值降到0~3.3 V范围内。否则将会烧坏芯片。隔离。当有高脉冲到来时,调理电路能有效将脉冲进行隔离。滤波,调理电路应滤除干扰信号,才能使系统对信号做出正确反应。

通过设置调理芯片、滤波电容、稳压二极管能搭建调理电路,完成降压、隔离、滤波等功能。下面将分别对各电路的原理和工作过程做详细介绍。

3.1 直流电压调理电路

调理电路的分压比为15:1,将直流电压可能出现的最大电压变换到3.3 V以内。为抑制高频干扰,分压电路输出端并接了一个滤波电容,并增加了一限幅稳压二极管以防止电压过大损坏芯片。当电压小于0时,稳压管导通,使输出电压为零。输出电压将在0~3.3 V之间。该系统使用芯片LM124。它是一种低功耗四运算放大器,工作电压范围宽。共有7路这样的电路,使用两片LM124。

图8 直流电压调理电路Fig.8 DC voltage conditioning circuit

3.2 动电压检测电路

在故障状态下(如三相输入交流电源缺相),系统会出现幅值很高、频率很大的脉动电压。此故障对系统危害很大,必须迅速查出。当程序检测出系统的电压幅值或频率过大时,立即断开其输出主接触器并置故障标志。

脉动电压检测电路如图9所示。输入信号LP先通过CAD1阻隔其中的直流信号,通过运放U8D改变输入信号的幅值。电容CAD2将交流信号转化为直流信号输出。其中,可变电阻R7的作用是改变输出信号与输入信号的比值,如果没有它,输出信号的幅值将不能控制;二极管DAD1的作用是防止电压过高损坏CPU;二极管DAD2的作用是防止电压过低损坏CPU;稳压管DAD3的作用是防止电压突然过高损坏电源。在这个电路中,输入信号经第一个电容后成为交流信号,经第二个电容后又成为直流信号,两个电容的作用不同。

图9 TRU脉动电压检测电路Fig.9 TRU pulsating voltage detection circuit

3.3 数字量输入模块设计

F2812由56个通用、双向数字I/O引脚,对它们的使用非常灵活,也相对较为简单,只要设置好相应的复用寄存器以及数据和方向控制寄存器就基本完成了所有工作。

如果需要更多的I/O端口,系统还提供了另一种方法:把地址线作为I/O端口来使用,并使用芯片LVC16245进行缓冲。这样做为系统多提供了16个I/O端口,使系统的I/O端口的数量达到72个。

图10 扩展I/O接口Fig.10 Extended I/O interface

3.4 数字量输出模块设计

数字量输出模块主要用于控制接触器等装置,由于要驱动继电器类负载,要求有较大的输出电流,因此需要加驱动电路。

输出控制驱动板主要完成对各接触器或继电器以及各告警指示灯的控制与驱动。输出控制驱动电路如图11所示。本电路中使用芯片MC1413,它是一种反向驱动器,主要用于电路的后级驱动,对前级电路的影响很小。IOA0可以控制接触器K1,驱动电流为0.5 A。IOA1可以控制三级管Q1。

4 通信模块设计

在本研究阶段采用的数据总线为RS232总线,下面是利用F2812内部的SCI控制器与上位机NAMP进行通信的接口电路。通信模块原理图如图12所示。

图11 输出控制驱动电路Fig.11 Output control drive circuit

图12 通信模块原理图Fig.12 Communication module schematic

图13 缓冲与电平转换电路Fig.13 Buffering and level shifting circuit

SCITXD是数据发送引脚,SCIRTXD是数据接收引脚。因在试验阶段,该电路采用了符合RS—232标准的驱动芯片MAX232,进行串行通信。MAX232芯片功耗低、集成度高,+5 V供电,具有两个接收和发送通道。

由于 F2812采用+3.3 V供电,所以在MAX232与F2812之间加了TI典型的电平转换电路,起双向、缓冲与电平转换的作用。整个接口电路简单、可靠性高。在通信过程中,LVC16245所起的作用非常关键,接法不对将会引起外部通信与DSP之间的冲突。在这种方式下,F2812的串行通信接口与RS—232串行口进行DSP与上位机之间的异步通信。

5 结束语

文中对光电跟踪系统控制器的硬件部分进行设计。包括光电跟踪系统控制器硬件电路框图,最小控制系统设计,模拟、数字量模块和通信模块设计等部分。采用此光电跟踪系统控制器使得动态性能得到了改善,不仅可以满足系统的精度要求,还具有较强的自适应能力。

[1]陶永华,尹怡欣,葛芦生.新型PID控制及其应用[M].北京:机械工业出版社,2008.

[2]李颖,朱伯立.Simulink动态系统建模与仿真基础 [M].西安:西安电子科技大学出版社,2009.

[3]刘金琨.先进PID控制MATLAB仿真[M].2版.北京:电子工业出版社,2005.

[4]Writes MH,Joris JL.Advanced of the pods:enhancing precision attacks night and day[J].Jane’s International Defense Review,2002,35(3):44253.

[5]Writesm H.The all-seeing eye above[J].Jane’s International Defense Review,2002,35(12):48-621.

[6]Richman JS,Moorman JR.Physiological time series analysis using app roximate ent ropy and sam ple entropy[J].Am.J.Physio l.Hear t Physio,2000(278):H2039-2049.