基于NiosⅡ的UART设计与实现

王一平 , 王代强 ,2

(1.贵州大学 贵州 贵阳 550025;2.贵州大学 人民武装学院,贵州 贵阳 550025)

SOPC技术自2000年提出以来,以其灵活性、可裁剪和扩展、系统可编程等优点被广泛应用于通信、军事等嵌入式领域。SOPC技术以NiosⅡ处理器为核心采用软硬件协同设计方案以及IP核复用等技术使得它在可靠性、体积、功耗、设计周期等方面实现了最优化,是未来的SOC和嵌入式发展的方向。

传统的UART专用芯片引脚多、内部还有许多其他的功能模块、占用面积大使得电路设计复杂,PCB面积增加。相对于集成度越来越高的SOC系统来说越来越不符合要求。而基于SOPC技术的UART设计可以合理应用在含有FPGA器件的系统中,将UART集成其中起到节约PCB面积的作用[1]。

文中设计了一种基于NiosⅡ的UART,并在EP2C8Q208C芯片上通过串口调试工具加以验证。

1 UART原理及协议介绍

串行异步接口即通用的异步收发器(UART,Universal Asynchronous Receiver Transmitter)成本低、传输线少、可靠性高因而应用广泛于。根据通信接口的传输速率、电气特性、连接特性等的不同, 有 RS-232、RS-423、RS-499、RS-485等不同的通信协议。其中RS-232是目前广泛采用的一个标准,常用于短距离、低速、低成本的通信[1-2]。

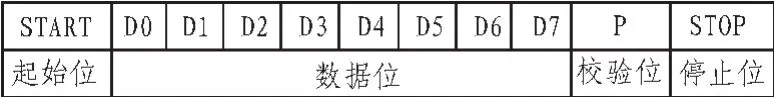

RS-232的基本通信只需要两条信号线(RXD、TXD)就可以完成数据的相互通信,接受和发生采用全双工形式,RXD是接受输入端,TXD是发送输入端。其基本的通信协议十分简单:以低电平为起始位,高电平为停止位,中间可传输5~8比特数据和1比特奇偶校验位,奇偶校验位的有无和数据比特的长度由通信双方约定,一帧数据传输完毕后可以继续传输下一帧数据,也可以继续保持为高电平,两帧之间保持高电平,持续时间可以任意长。图1为UART的数据帧的格式。

图1 UART的数据帧格式Fig.1 UART data frame form

2 SOPC中硬件构造实现

1)系统的整体硬件结构

SOPC系统一般Nios软核cpu、存储器、I/O等构成。用户的根据需求选择Nios软核、存储器、IP核或自定义IP核,分配好内存地址和中断优先级别,就构成了所需要的系统。Nios软核与UART核、其他IP核、SDRAM等通过Avalon总线侨联并与外设相连[3]。

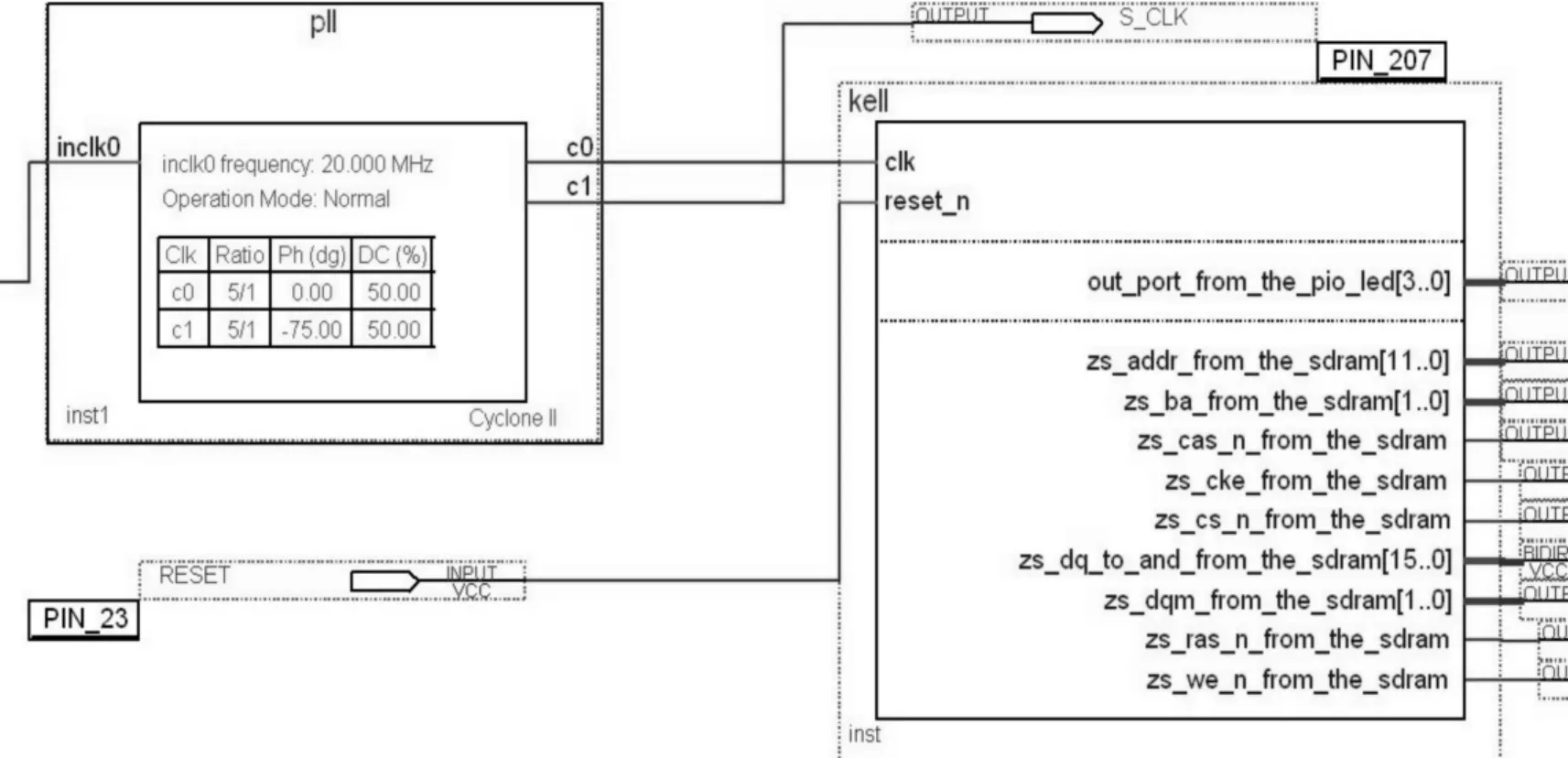

NiosⅡ提供3种供用户选择的软核,在本文设计中我们选择NiosⅡ/e(经济型)软核,并调用系统自带的UART核(RS232)、epcs、sdram等构成系统,并设置好中断级别和内存地址,就生成了SOPC系统[4]。由于用到了SDRAM需要调用控制外部的sdram器件,由FPGA引入时钟信号后需要加上一个锁相环(PLL)模块倍频生成Nios系统和sdram的控制信号,并设置两个控制信号间的相位差。整体系统的电路原理图如图2所示。

图2 SOPC系统的组件Fig.2 SOPC system’smodule

2)UART 核的设置

作为整个系统的核心的UART核,是一款quartus软件自带的IP核。它内部是包括波特率除数寄存器、接收寄存器、发送寄存器、移位寄存器等。它提供目标系统与开发系统的连接。从功能设计上看:它与Nios软核通过avalonz总线结构连接,并提供外部的电平转换模块的接口。

UART核中初始的波特率设置为115200,Baud rate can be changed by software选项设置成允许软件设置波特率;检验方式、数据位、停止位等设置为none、8和1。

3)电平转换电路模块

本文中采用的RS-232标准规定逻辑1的电平为-15~-3 V,逻辑0的电平为+3~+15 V。COMS电路的电平范围一般是从0 V到电源电压,FPGA的I/O输入输出电压通常为0~3.3 V,为了保证 FPGA设计的 UART接口与 RS-232电平保持一致,必须加电平转换芯片,进行UART的TTL/COMS电平与RS-232电平的转换[5]。本设计采用MAX232电平转换芯片,支持两个串口的电平转换。

3 软件设计分析

1)UART核的寄存器结构及C语言描述

根据表1中UART核的寄存器结构[6-7],笔者在 sopc.h文件中定义一个UART_ST的结构体。它包含在硬件中用到的接收数据位、发送数据位、状态、控制及除数五个共用体。其中的每个共用体根据偏移量决定顺序,并包括一个结构体和用于整体清零WORD的变量。在sopc.h中还用宏定义声明了UART的基地址。然后需要编写一个uart.h文件用于以结构体形式声明UART核工作所用到的receive_flag、receive_count、*init等Nios开发包自带的需要用到的UART函数。编写sopc.h及uart.h文件是为了在后面编写UART核的驱动时候方便调用。

表1 UART核寄存器映射Tab.1 UART nuclear register map

2)UART核的驱动描述

在编写成功前面 sopc.h及 uart.h文件后, 需要根据UART的工作原理编写RS232工作的驱动文件uart.c。

在uart.c文件中我们要声明定义以下函数:

①intuart_send_byte(unsigned char data)用于发送一个字节

②void uart_send_string (unsigned int len, unsigned char*str)发送字符串数据

③intset_baudrate(unsigned intbaudrate)软件设置波特率

④void uart_ISR(void)声明 uart所用到的中断

⑤int uart_init(void)初始化 uart等等。

版面关系仅列举uart_send_byte函数的代码:

4 系统的实现验证

整个系统的软件硬件部分都编辑完成后首先通过quartus和Nios IDE软件编译并将硬件仿真无错误后下载到目标芯片EP2C8Q208C中通过串口调试工具实现PC机和UART的通信。

图3 串口的调试Fig.3 Serial port debugging

5 结束语

基于NiosⅡ设计的UART在以FPGA为核心控制芯片的嵌入式系统中有着一定的优势,可以节约PCB面积并且具有成本低、易于升级等优点。该系统实现了基本的UART功能,并且后续的可以通过添加FIFO模块提升传输容量等。

[1]Ahera Corporation.NiosⅡ proce,~sor reference handbook[S].[S.1.]Ahera Corporation,2003.

[2]任爱锋,初秀琴.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.

[3]Ahera Corporation.Quartus 11 version 6.0 handbook[S].[S.1.]Ahera Corporation,2006.

[4]郑哑民,董晓舟.可编程逻辑器件开发软件Quartus II[M].北京:国防工业出版社,2006.

[5]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天出版社,2003.

[6]王建校,危建国.SOPC设计基础与实践[M].西安:西安电子科技大学出版社,2006.

[7]张志刚.FPGA与SOPC设计教程——DE2实践[M].西安:西安电子科技大学出版社,2007.