基于边界扫描的混合信号电路可测性结构设计*

苏 波

(1.桂林电子科技大学 电子工程学院,广西 桂林5410041;2.广西工商职业技术学院 信息与设计系,广西 南宁530003)

随着超大规模集成电路、表面贴装元件、叠层多芯片模块及高密(多层)印制电路板PCB(Printed Circuit Boards)等的发展与广泛应用,现代微电子技术正朝着高密度、高速度、高可靠和微型化方向飞速发展[1]。然而,电路的规模剧增而物理尺寸锐减,导致了测试面临越来越多的问题,由此引发了对新测试方法的探索。文中对基于边界扫描技术的可测性结构展开研究。分模块设计符合IEEE1149.1及IEEE1149.4标准[2-3]的可测性结构各个组成部分,包括测试访问口TAP(Test Access Port)控制器、数字边界扫描单元、模拟边界扫描单元、测试总线接口电路及测试寄存器。

1 IEEE1149.4标准

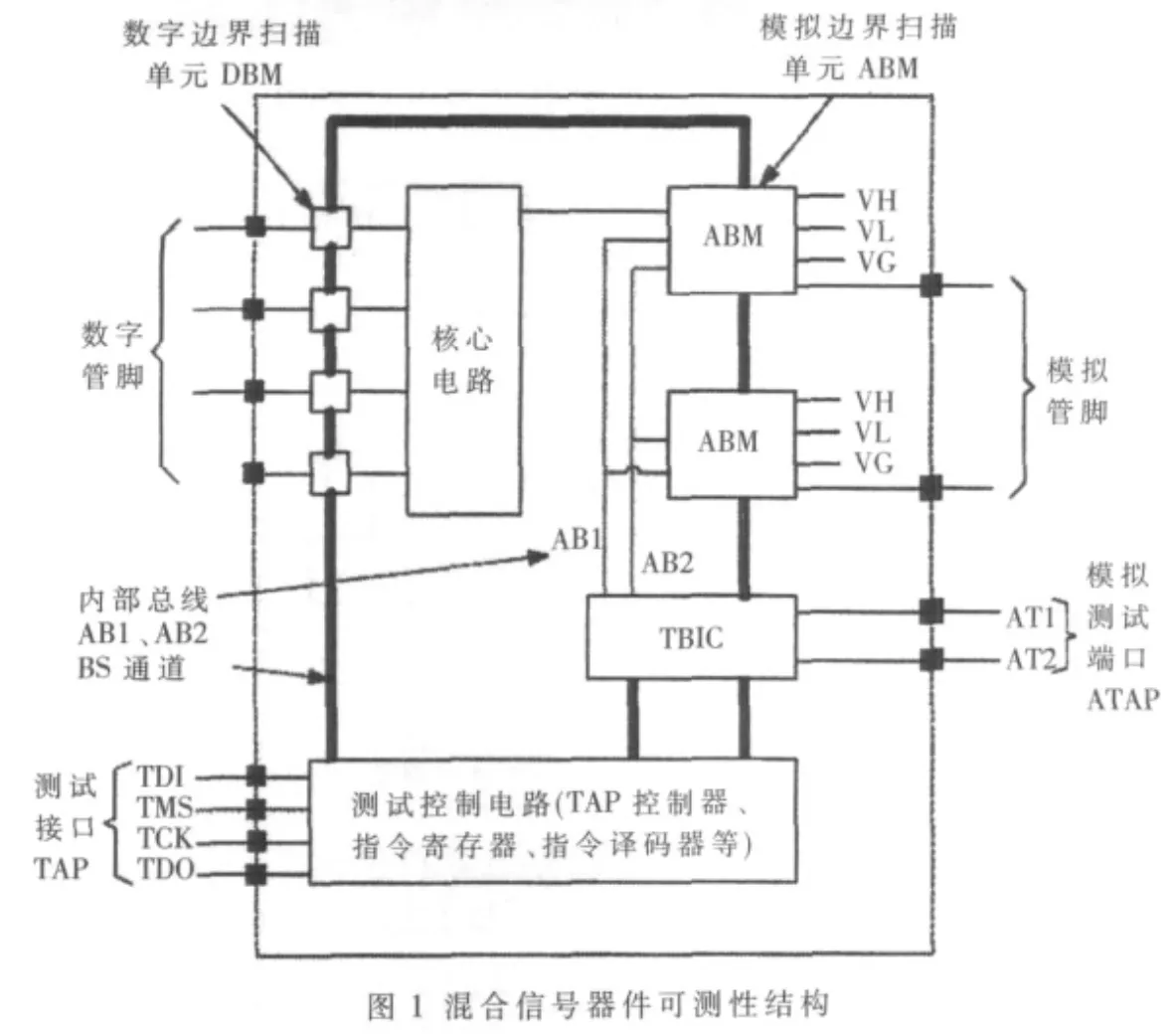

IEEE1149.4标准继承了IEEE1149.1标准的设计思想,它在模拟管脚上施加与数字边界扫描单元(DBM)相似的模拟边界扫描单元(ABM),将它们与数字边界扫描单元一起依次串联成边界扫描寄存器链,为测试指令和数字测试数据提供串行移位通路。为满足模拟管脚测试的要求,标准专门在芯片内部添加了两条内部模拟测试总线即AB1、AB2。各模拟边界扫描单元通过概念开关与内部模拟测试总线相连,内部模拟测试总线上的模拟信号可在测试总线接口电路(TBIC)的控制下,与模拟测试接口(ATAP)通信。而模拟测试接口则是外界模拟信号源、模拟测试响应处理器与模拟边界扫描器件的接口,这就构成了一条虚拟探针形式的模拟信号通路,外界模拟测试信号可通过这条模拟信号通路施加到某一模拟管脚上,模拟管脚上的模拟数据也可通过这条模拟测试通路输出到外界,由模拟测试响应处理器处理。模拟测试总线、模拟测试边界扫描单元以及模拟测试接口构成IEEE1149.4标准的主要特征。

混合信号器件的边界扫描结构由边界扫描测试接口(TAP)、边界扫描测试控制部件、测试总线接口电路(TBIC)和边界扫描测试单元(包括DBM 和ABM)组成,如图1所示。

2 混合信号电路可测性结构设计

IEEE1149.1及IEEE1149.4标准中对混合信号电路可测性结构做了比较详尽的论述,对于如何实现这种结构提出了指导性的规范。通过分析IEEE1149.1及IEEE1149.4标准可知,混合信号电路可测性结构主要由TAP控制器、数字边界扫描单元(DBM)、模拟边界扫描单元(ABM)、测试总线接口电路(TBIC)及测试寄存器构成。分别实现各个组成部分,设计出标准接口,以便在混合信号电路的可测性设计中调用。在实现方式上,可测性结构测试逻辑部分采用VHDL语言进行描述,并在Model Technology公司ModelSim6.1仿真调试软件及Synplify7.5高质量综合软件等工具上开发实现。

2.1 TAP控制器设计

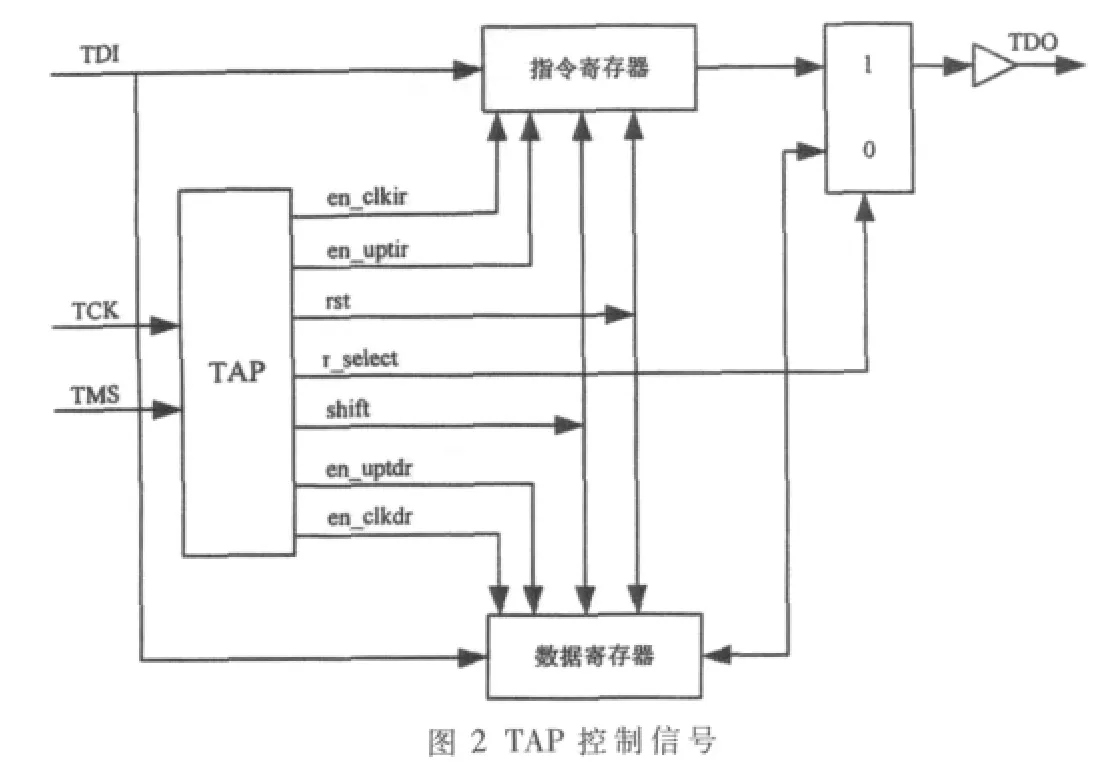

TAP控制器是整个混合信号可测性结构的核心部分,它在由IEEE1149.4接口输入的测试控制信号TMS和测试时钟TCK的控制下产生混合信号测试所需的各种状态,并发出所需的控制信号。TAP控制器生成各种测试控制信号如图2所示,这些控制信号用来控制指令寄存器、数据寄存器以及控制一些端口的选通。图中所示的由TAP控制器生成的各种控制信号用来给指令及数据移位提供时钟,其余的辅助状态实现测试数据准备、测试等待等操作。

TAP控制器的核心是一个16状态的状态机,每个状态对应生成控制信号。为了能获得可综合的、高效的VHDL状态机描述,设计中使用多进程方式来描述状态机的内部逻辑,一个进程描述时序逻辑,包括状态寄存器的工作和寄存器状态的输出;另一个进程描述组合逻辑,包括进程间状态值的传递逻辑以及状态转换值的输出。

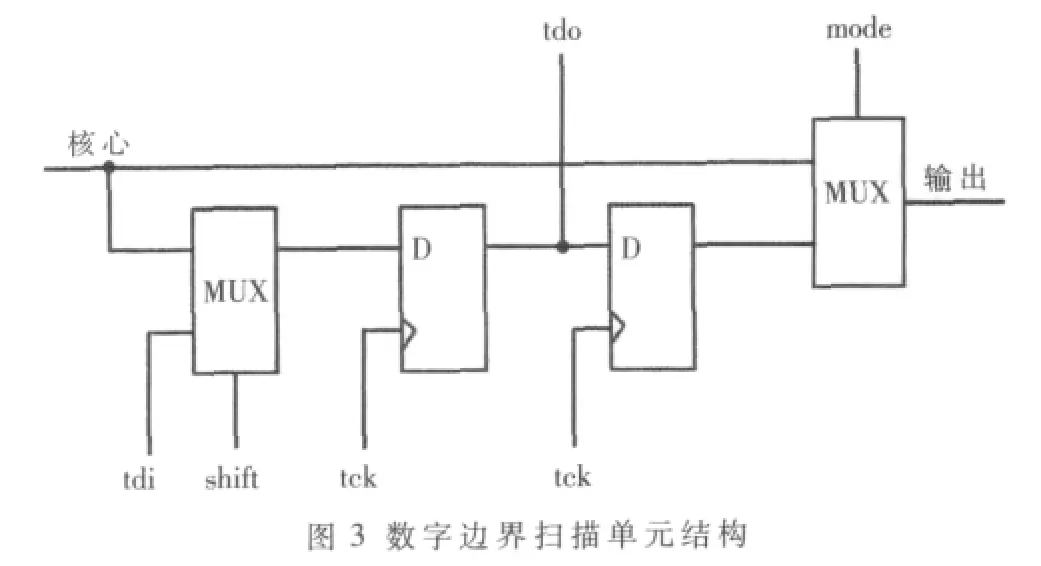

2.2 DBM单元设计

数字边界扫描单元有多种实现方式,文中对于输出数字边界扫描单元采用如图3所示的结构实现。虽然该结构不是最优的,但是它严格遵守了标准的最低要求且硬件开销小。

2.3 ABM控制逻辑设计

ABM单元逻辑部分结构主要由移位寄存器、更新寄存器和控制逻辑三部分组成。其中,移位寄存器和更新寄存器用来实现数字信号的输入/输出;控制逻辑则用来控制模拟引脚的开关矩阵。模拟边界扫描寄存器控制逻辑部分的实现是将控制逻辑按功能不同分作移位寄存器、更新寄存器和开关控制逻辑三部分,先分别设计后,再按各部分的连接情况组合在一起。

2.4 TBIC控制逻辑设计

TBIC控制逻辑结构与ABM控制逻辑结构类似,设计时采用自顶向下的设计方法,将整个控制逻辑结构分为移位寄存器、更新寄存器、开关控制逻辑三部分。移位寄存器和更新寄存器运用寄存器综合实现。开关控制逻辑通过行为描述来实现。在这三部分实现的基础上由一系列的寄存器和多路选择器组成多级寄存器链。

2.5 测试寄存器设计

测试寄存器主要包括边界扫描寄存器、指令寄存器、旁路寄存器、设计专用数据寄存器。其中边界扫描寄存器、指令寄存器和旁路寄存器是标准规定必选的测试寄存器,设计专用寄存器为可选测试寄存器。

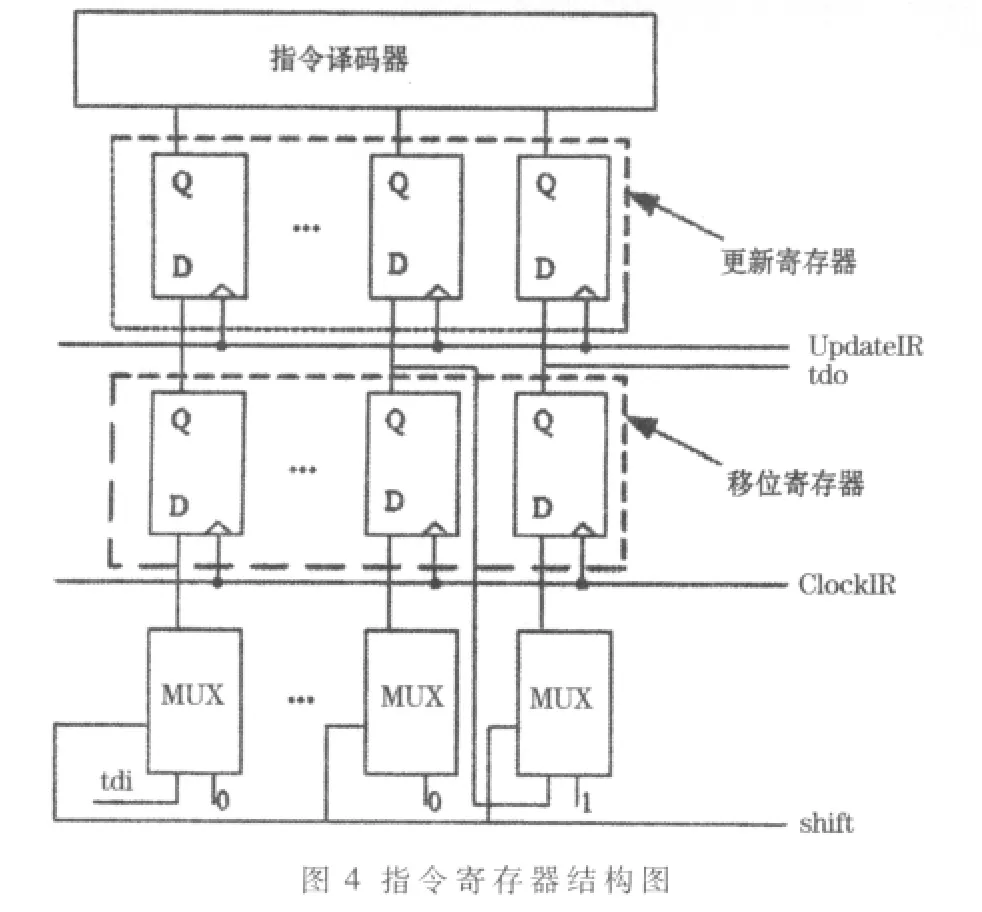

指令寄存器设计结构如图4,指令寄存器采用一种移位/更新寄存器结构。这种结构在时钟信号ClockIR的激励下,以串行方式将指令从tdi逐位移入指令寄存器IR中,并从tdo输出;在更新信号UpdateIR的激励下,移位寄存器中的指令将装入更新寄存器 (指令锁存器)中,指令锁存器中的指令经译码后,配合tms信号产生控制边界扫描电路的各种控制信号。

旁路寄存器设计为一位寄存器,它提供了从tdi到tdo的一位通路,允许迅速地访问PCB上的器件,将未选定的器件的边界扫描链长度缩减为一位,从而大大简化了测试复杂度,提高了测试效率。

3 验证电路设计

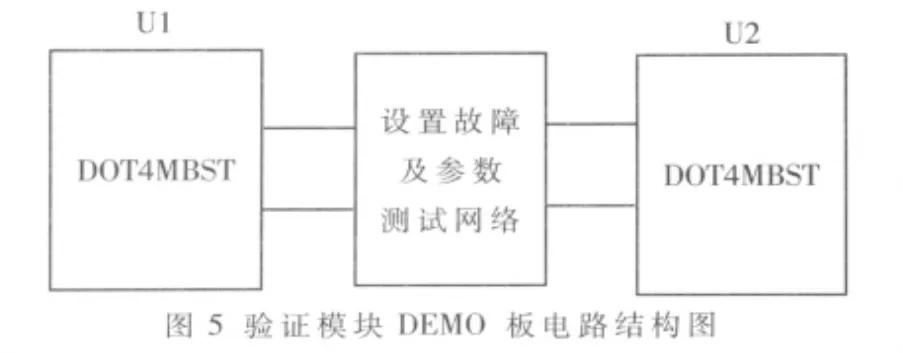

为检测所设计的可测性结构是否可行,在测试验证中将所设计可测性结构进行了硬件的实现,构成了一个验证模块DOT4MBST,并以此为主要构成部件设计了验证模块DEMO板。DOT4MBST中设计了2个模拟边界扫描单元、4个数字边界扫描单元,内核电路数字部分为一个半加器,而模拟部分为一个射随器,模块边界扫描链长度设置为16位。

验证模块DEMO板结构如图5所示,验证模块DEMO板以验证模块DOT4MBST为主组成,其中互连网络中设置参数测试网络如图6所示,P11与U1的输出模拟边界扫描单元的模拟引脚连接,P21与U2的输入模拟边界扫描单元的模拟引脚连接;P12与U1的一个输出DBM单元的数字引脚连接,P22与U2的一个输入数字边界扫描单元的数字引脚连接。通过开关设置,可以灵活配置U1、U2之间的参数元件网络。

4 测试验证

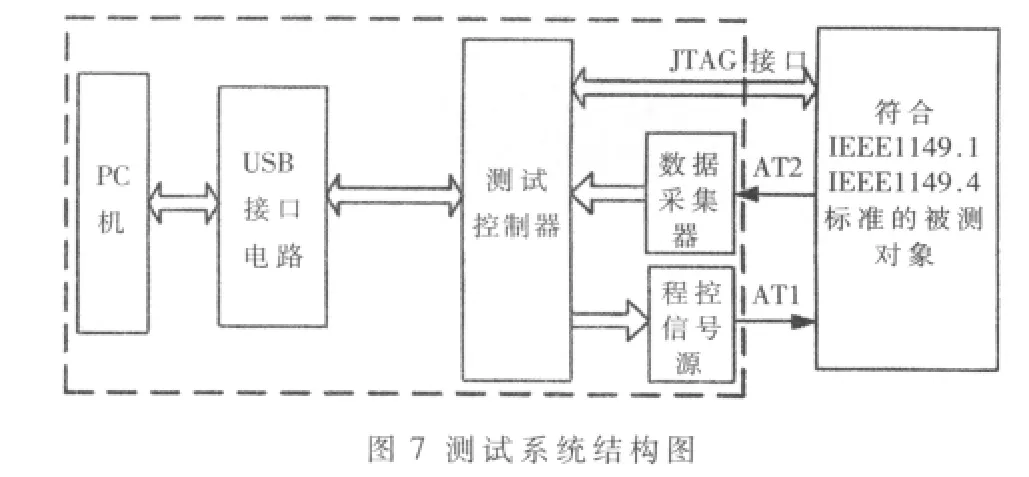

测试验证所用的测试系统是桂林电子科技大学CAT研究室开发的混合信号边界扫描测试系统。该系统是一套兼容IEEE1149.1标准和IEEE1149.4标准的测试系统,是“十五”国防预研项目的研究成果之一,已经通过专家鉴定和验收,它能对符合IEEE1149.1及IEEE1149.4标准的被测对象进行各种边界扫描测试[4-5]。

硬件部分的功能主要是发出测试控制信号、施加测试激励和处理测试响应,由混合信号边界扫描测试主控器、程控信号源、数据采集板和微机接口电路等模块构成,其结构如图7所示。

测试系统硬件结构的核心部分为测试主控器,采用RISC技术,用FPGA实现,是整个测试系统的控制者,是整个测试系统基本框架设计的关键。其功能主要有两方面:一方面是读入测试程序存储器中的测试主控器指令和测试激励数据,根据主控器指令产生相应的测试访问口信号,即 TCK、TMS、TRST、TDI,控制程控信号源产生模拟测试激励给 AT1、处理测试数字响应 TDO、读取数据采集板采集的测试模拟响应AT2的数字数据;另一方面是与测试存储器、接口控制器、程控信号源、数据采集板和被测对象进行通信,以获得测试主控器指令和测试激励数据、捕获并存储测试响应等。

程控信号源的功能是根据测试主控器送来的模拟激励的幅度数据和频率数据生成相应的模拟测试激励,经AT1脚送给被测对象。

数据采集板的功能是将AT2脚采集到的测试模拟响应(包括幅度和相位)转换成数字数据送给测试主控器。由测试主控器将其读取并存入到测试存储器的响应存储器中。

微机接口电路采用USB技术,以CY7C68013接口芯片为主构建,支持测试指令及测试矢量的高速传输,实现了接口电路固件的自动下载,使测试系统的使用更加方便快捷。

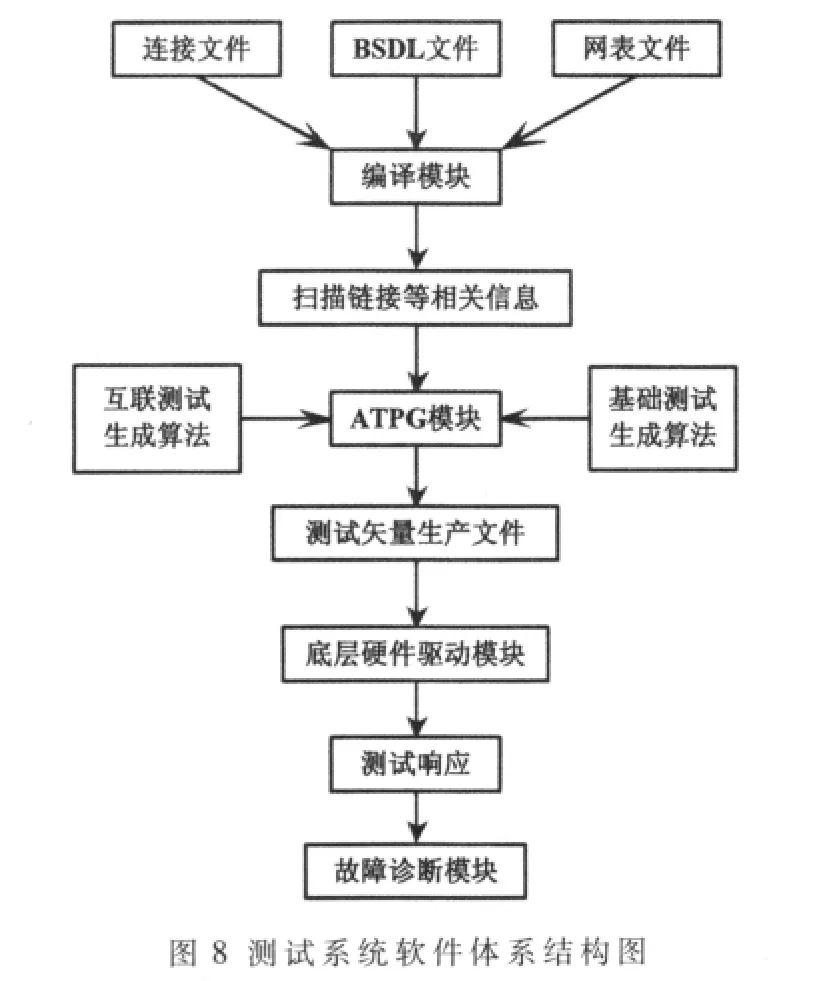

软件部分的主要功能是根据提供的电路连接信息文件、BSDL文件及网表文件生成测试矢量并进行故障诊断。混合信号边界扫描测试系统的软件体系结构如图8所示。

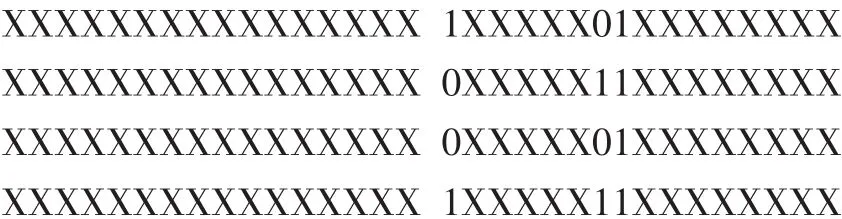

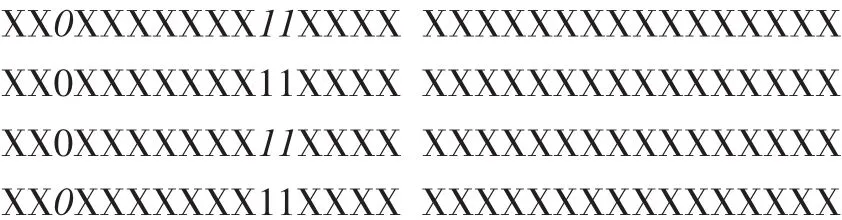

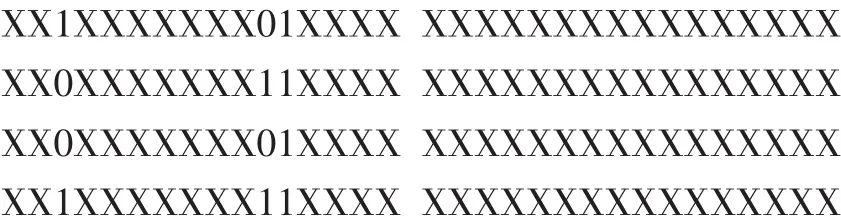

验证中所作的测试主要为互连测试,在验证模块DEMO板上,通过设置互连网络,将一个DBM所对应的管脚与一个ABM所对应的管脚分别设置为固定0和固定1故障。将下面的测试矢量加载到混合信号边界扫描测试系统中并执行EXTEST测试。

读回的测试响应为:

预期正确测试响应为:

矢量中“X”表示无关项,比较测试输出与预期正确测试响应,其中的斜体部分表示与预期正确响应相反。可以看出DBM与ABM对应的管脚分别发生了固定0和固定1故障。

由测试结果可知,测试系统能对验证DEMO板做互连测试,并能进行故障识别及定位,这说明设计的可测性结构符合IEEE1149.4标准,并能应用到实际的电路设计中,有效解决模拟电路测试问题。

[1]陈光礻禹..可测性设计技术[M].北京:电子工业出版社,1997.

[2]IEEE Standard 1149.1-2001.IEEE Standard Test Access Port and Boundary Scan Architecture[S].IEEE Standard Board,2001:1-2,16-20.

[3]IEEE Standard 1149.5.IEEE standard for Module Test and Maintenance Bus(MTM-Bus)protocol[S].IEEE Standard Board,199:1-4.

[4]雷加,陈凯.数模混合电路互连测试矢量自动生成的实现[J].计算机测量与控制,2006,16(6):844-846.

[5]雷加,陈寿宏.基于 IEEE1149.4标准的 K节点故障诊断研究[J].计算机测量与控制,2006,14(9):1113-1114.