高效率集成电路测试芯片设计方法

胡龙跃,史 峥,刘得金,邵康鹏

浙江大学 超大规模集成电路设计研究所,杭州 310027

1 引言

在超大规模集成电路工艺制造过程中用来测试器件电学性能、监测成品率和监控制程的测试基本单元或者基本结构,被称为测试结构。测试芯片是一系列测试结构的组合体[1-2]。

根据 ITRS(International Technology Roadmap for Semiconductors)[3]2011的报告,超大规模集成电路新技术产品从基础技术研究到工艺开发,从工艺开发到产品开发分别需要36个月的时间。在工艺开发中,一个很重要且不停循环进行的工作是通过设计测试芯片来检测工艺缺陷、评估器件性能使得工艺制程更加稳定和成熟,从而提高芯片的成品率[4-5]。其次,由于工艺制程复杂和成品率缺失来源繁多,要精确检测和定位,需要设计数目庞大的测试结构来完成测试实验[6-7]。基于以上两点,测试芯片设计是一个贯穿整个工艺开发过程的工作,需要不断设计、实验和测试,直到工艺达到稳定和成熟的高成品率阶段为止。

在PDK(Process Design Kit)测试中也同样面临以上问题,当前集成电路制造业普遍采用的方式是通过人工的方式手动完成所有结构的版图设计[8],通过修改SKILL脚本或者Tcl脚本等来完成PDK中PCell(Parameterized Cell)测试结构生成[9],其问题主要是需要大量的人力投入,而且时间周期长。

针对测试芯片中测试结构的相似性特点[10],提出了一种测试芯片设计方法,该方法通过对各类测试结构批量参数化建模,利用版图编辑器作图,来提高测试芯片设计效率。依据此方法,开发了一套针对工艺开发包的测试芯片,实验结果验证了其高效性。

2 测试芯片设计方法

2.1 测试结构参数化建模

对测试结构进行参数化建模是将测试结构的技术规格如关键尺寸、线宽、线间距、图层以及图层相对位置关系等所有可以表征测试结构的变量进行参数化定义,将参数作为测试结构版图生成工具(例如参数化单元)的输入变量,为后期测试结构版图生成工具的实现与应用做准备。

对测试结构的参数化建模分为两个步骤,第一步根据实验设计的要求将需要进行实验的关键尺寸或类型进行参数化。第二步是将测试结构中除实验设计的关键性参数之外的其余特征尺寸、类型等进行参数化定义。考虑到可制造性问题,这一部分规格参数需严格按照设计规则进行设计。设计规则规定了半导体制造的各工艺图层的最小线宽、最小线间距、最小/最大密度等,需严格按照设计规则设计才能够保证器件有良好可造性。

2.2 测试结构版图编辑器

为了缩短测试结构生成周期,本文提出了一种基于直观图形操作的版图编辑器,该编辑器利用优化设计后的约束操作及运算操作功能,可以高效、快速地产生测试结构版图。

该版图编辑器的架构图如图1所示,它包括属性参数输入、图形属性定义、约束定义、版图运算操作定义、版图编辑器和版图浏览器六个部分。其中属性参数的类型和命名用于图形属性的定义、图形间约束条件的定义和版图运算操作的定义。图形属性定义包括图层、几何尺寸以及坐标的设置。约束操作用来操作图形的相对位置关系,包括间距约束(space)和对齐约束(alignment)两类。版图运算操作包括通孔自动填充、布尔运算(与、或、异或等)等类型。

图1 版图编辑器的架构图

版图编辑器支持的约束操作有两种类型,一种是间距类型,一种是对齐类型。

space约束用于规定图形或者物体之间距离的相对位置关系。定义一个space约束需要有一个参照物体和一个移动物体,并制定约束的参考值。参照物体既可以是版图中的某一个图形的一条边,也可以是一个实例化单元的一条边。参考值是一个输入参数变量,可以从参数化建模中直接得到;如果是正数,那么被移动物体将被移动到参考物体的上方或者右方。负数反之。

alignment约束用于规定图形或者物体之间的水平或者竖直的对齐关系。同样地,需先定义一个参照物体和一个移动物体。参照物体通常是版图中某一个物体或实例化单元的某一条边的垂直中心线,也可以是某一个顶点或者中心点。移动物体是指被这个约束限制,其相对位置或者物体属性将发生变化的物体,也可以是某一个物体或实例化单元的某一条边的垂直中心线,或者某一个顶点或中心点。

alignment约束需要对对齐方向进行选择,有水平方向、垂直方向、和双方向三个选项。

版图编辑器支持的版图运算操作类型,主要有用于完成对版图运算如contact/via的自动填充,图形布尔操作等等。列举几种操作类型如下:

Fill,按照指定条件自动完成contact/via的填充;

Remove,移除指定的object;

Boolean AND,对图形进行“与”操作;

Boolean MINUS,对指定边框减去object;

Masking BBox,为指定cell或者object添加一个边框层,用于implant层的自动产生;

Cut hole,对object进行挖孔操作。

2.3 同类实验设计

结束前两步的操作后,将参数化建模的参数输入到版图编辑器生成的测试结构中,可以生成一个与之相对应的实例化的测试结构。

此时需进行同类实验设计。首先,将参数化建模中需要批量修改的参数提取到电子表格,保存成为电子表格格式。然后,利用电子表格对于数据处理的便捷性,如等差数值递增等,可以迅速得到一组参数并保存。最后,通过导入已经拥有大量数据的电子表格到版图生成器中,参数名称与版图结构拥有对应关系,从而生成多个测试结构。具体过程如图2所示。

图2 同类实验设计

2.4 实例演示

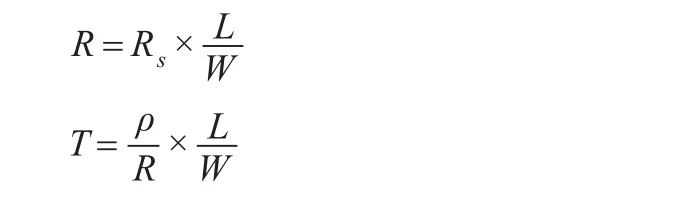

对于CMOS电路一个重要的电学特性就是方块电阻,普遍采用Van der Pauw method[11]中描述的Kelvin结构来测量。对于内部金属电阻需要下列公式计算:

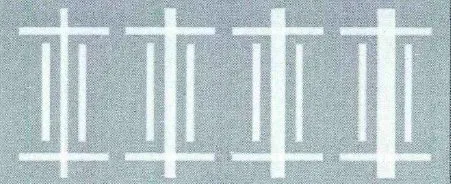

其中,R表示互连电阻值,Rs表示互连线条的薄膜电阻,L为金属线长度,W为金属线宽度,T为金属线条厚度,ρ为金属的电阻率。通过上面两个式子,可以将芯片互联线的设计尺寸和实际物理尺寸对比。其版图结构示意如图3所示。

图3 Kelvin结构参数化建模示意图

以此为例,演示测试结构版图的实验过程。

(1)参数化建模

参数化建模如图3所示,其中实验设计关键参数是KelvinWidth、DummyWidth和 DummySpace。列表如表 1所示。

表1 MOS管建模参数列表

(2)版图编辑器实现

通过使用相关约束操作和运算操作,可以迅速得到版图如图4。

图4 Kelvin在版图编辑器中生成

(3)同类实验设计

完成了MOS管版图编辑器实现之后,按照实验设计关键参数的电子表格,如表1所示,输入到版图编辑器中,根据实验要求修改参数的变量参考值产生一组参数,并依次生成与此组参数相对应的测试结构版图。例如此处取KelvinWidth的变量参考值分别为0.5、0.8、1.0、1.2,即可批量产生Kelvin结构如图5所示。

图5 批量生成Kelvin测试结构版图

3 开发PDK测试芯片

依据此设计方法,开发出了针对PDK的一套测试芯片,实验对象为基于Cadence公司软件工具所开发的PDK。生成此PDK的测试芯片分为以下步骤:

(1)通过 Cadence公司的全定制化集成电路开发平台Virtuoso执行SKILL命令集,引发通信调用机制[12-13],获得PDK的基本信息,即PDK的名字以及PDK对应的所有的单元的名字。

(2)通过图形编辑器的操作,完成参数化单元图形测试结构的绘制,自行设置该参数化单元的参数信息,并使之与图形测试结构对应,可以批量生成测试结构,保存在PDK的相应单元名称下。

(3)将多个测试结构置于焊盘之间,定义引脚和焊盘之间的连接关系,批量地进行布局和绕线,生成测试芯片。

(4)对生成的测试芯片进行设计规则检查,避免配置的参数与设计规则发生冲突,修改使其通过设计规则检查。

PDK生成测试芯片机制如图6所示。

基于国内某半导体生产商的40 nm工艺开发包,该工艺开发包含32个单元,用该设计方法开发了一套测试芯片进行实验。生产商要求一套工艺开发包测试结构数量为6 976个,平均每个单元需要测试结构218个,实验结果如表2所示。

表2 生成测试芯片时间 s

4 结束语

介绍了一种高效率的测试芯片设计方法。通过完成成品率测试所需的测试结构批量参数化建模,以及使用版图编辑器作图来快速生成测试芯片。依据此方法,开发出了一套针对工艺开发包的测试芯片,实验结果表明生成测试芯片的易操作性,以及在可制造性成品率提高中的高效意义。

图6 开发PDK测试芯片机制

[1]俞建峰,陈翔,杨雪瑛,等.我国集成电路测试技术现状及发展策略[J].中国测试,2009,35(3):1-5.

[2]孔睿,李莉.新型集成电路芯片测试仪[J].中国新通信,2009,11(9):90-93.

[3]ITRS.International technology roadmap for semiconductors[R].2011.

[4]Zhang Bo,Pan Weiwei,Zheng Yongjun,et al.A fully automated large-scale addressable test chip design with high reliability[C]//20th European Conference on Circuit Theory and Design(ECCTD),2011.

[5]Hansen C K.Effectiveness of yield-estimation and reliabilityprediction based on wafer test-chip measurements[C]//Reliability and Maintainability Symposium,1997.

[6]Wu Meng-Chiou,Lin Rung-Bin.Reticle floorplanning and wafer dicing for multiple project wafers[C]//6th International Symposium on Quality of Electronic Design,2005.

[7]LukaszekW,Grambow K G,YarbroughW J.Testchip basedapproachto automated diagnosisofCMOS yield problems[J].IEEE Transactions on Semiconductor Manufacturing,1990,3(1):18-27.

[8]祝晓波,冯江.工艺设计工具包PDK的应用及开发[J].电子设计应用,2006(2):77-78.

[9]Luo Haiyan,Chen Lan,Yin Minghui.A design method for process design kit based on an SMIC 65 nm process[J].Journal of Semiconductors,2010,31(10).

[10]Ternisien D'ouville T,Jeanne J P,Leclercq J L,et al.Automatic test chip and test program generation:an approach to parametric test computer-aided design[C]//ICMTS,1992.

[11]Van der Pauw L J.A method of measuring specific resistivity and hall effect of discs of arbitrary shape[J].Philips Research Reports,1958,13:1-9.

[12]俞宏峰,黄艳,耿卫东,等.基于SKILL的eda系统二次开发技术探讨[J].计算机应用研究,2001,18(8):85-88.

[13]刘成玉,姚芳.Cadence中的参数化单元的开发[J].集成电路通讯,2011(6):12-14.

[14]王阳元,张兴,刘晓彦,等.32 nm及其以下技术节点CMOS技术中的新工艺及新结构器件[J].中国科学:E辑,2008,38(6):921-932.

[15]Chiang C,Kawa J.Design for manufacturability yield for nano-scale CMOS[M].[S.l.]:Springer,2007.