数字电视传输流ASI接口的设计与实现

薛继霜 张敬坡

(1 天津职业大学电子信息工程学院 天津 300410)

(2 天津市德力电子仪器有限公司 天津 300113)

1 引言

数字电视传输流(TS)数据信号的接口类型有3 种形式:同步并行接口(SPI)、异步串行接口(ASI)和同步串行接口(SSI)。其中,同步并行接口和异步串行接口形式较常用。这2种接口各有优缺点:同步并行接口的优点是:接口有11 位有效信号,信号的每一位都是采用差分对形式传输,这样可以提高信号传输的可靠性和抗干扰性,缺点是:连接形式一般采用DB25 接口传输,DB25 接口连线多而且复杂,并且传输距离短,还容易出现故障。由于同步并行接口是并行11 位信号,处理起来比较简单且可扩展性强,因此目前数字电视常用的MPEG-2 解码器的输出都是标准的并行11 位信号。异步串行接口的优点是:采用串行传输,只需要一根同轴电缆线传输,连线简单而且传输距离长。缺点是:数据传输速率比较高,为270 Mb/s,在进行码率调整之前,需要对信号进行处理,将ASI接口中的同步字节删除,进行串并转换,再做进一步处理,所以说对ASI 信号的处理稍微复杂一些。根据同步并行接口和异步串行接口的优缺点,在实际应用中需要将传输信号的形式在SPI 和ASI 之间转换。

2 同步并行接口的信号结构

同步并行接口(SPI)数据格式如图1 所示,一般来说,同步并行接口数据包括一位时钟信号、8 位数据信号、一位数据有效信号和一位帧同步信号,分别对应图1 中的OCLK、DO[7:0]、DEN、PSYNC。有的解调芯片还附加输出一个数据不可纠错信号UNCOR,这个数据不可纠错信号UNCOR 的功能和数据有效信号DEN 的功能是大同小异的,可以根据实际需要进行取舍。帧同步信号对应传输流数据包的同步字节47 H,数据有效信号用来区分数据包的长度为188 个字节还是204个字节,如图1 所示。当数据包长为188 字节时,数据有效信号一直为高,数据信号和帧同步信号都与时钟信号的上升沿保持同步,在数据没有出错情况下,此时数据不可纠错信号UNCOR 的功能和数据有效信号DEN 的功能是一样的,当数据有错误发生时,数据不可纠错信号UNCOR 输出有效。

图1 SPI 数据格式

在实际应用中,常用的数字电视解调芯片都支持图1 的格式,方案中选用图1 的数据格式。

3 异步串行接口

异步串行接口的传输流(TS)可以有不同数据速率,但是传输速率是恒定的270 Mbps,因此异步串行接口可以发送和接收不同速率的MPEG-2 数据。方案是应用在数字电视信号分析仪中,作为仪器本身的一个功能模块使用,接口选用适用于同轴电缆传输的BNC 接头,模块的输入是SPI 数据,首先是CPLD 芯片控制FIFO 的数据写入,将SPI 数据临时保存在FIFO 中,以便后期使用,当FIFO 快写满的时候,CPLD 控制CY7B923 开始读取FIFO 中存储的数据,CY7B923 的主要作用就是将包同步的数据进行8b/10b 转换,然后进行并/ 串转换;在进行并转串时,当要求输入一个新字,而数据源还没有准备好时,自动插入一个同步字,以达到ASI 的恒定的270M bps 传输速率。当CY7B923 读取FIFO 的数据接近FIFO为空时,CPLD 控制CY7B923 停止对FIFO 的读取操作,此时就是CY7B923 自动插入同步字的时间。最终CY7B923 所形成的串行比特流将通过缓冲/ 驱动电路,输出到同轴电缆连接器上。这是DVB 标准中基于同轴电缆的ASI 传输系统的传输部分的工作原理概述,方案对传输部分做了实现。

4 ASI接口的实现

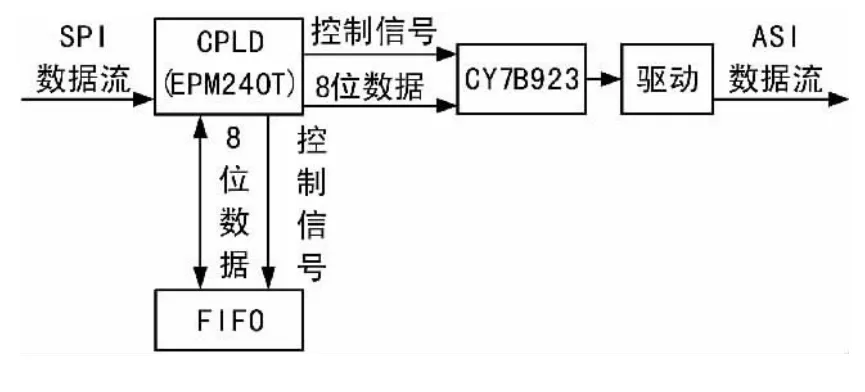

在方案中,传输流由多片MPEG-2 解码器提供,不同的解码器分别对应不同的数字电视制式,主要包括DVB-C、DVB-T、DTMB、VSB 等4 种常用制式。它们均输出符合SPI标准的并行11 位信号,传输流包长度为188 个字节。在同步并行到异步串行的转换方案中,主要选用CYPRESS 公司CY7B923 芯片、异步FIFO 存储芯片和ALTERA 公司的可编程逻辑器件实现。

CY7B923 的主要功能是实现数据的8 b/10 b 转换、插入同步字和并/ 串变换。异步串行接口的传输速率恒定为270 Mbps,而输入传输流的码率是不同的,所以要用异步FIFO 存储芯片实现速率匹配,需要对输入的SPI 数据、异步FIFO 和CY7B923 之间的数据传输进行逻辑控制。考虑到性价比和编程的难易程度,方案采用ALTERA 公司的可编程逻辑器件EPM 240T100,用VHDL 编程实现对它们的逻辑控制。

在方案中,传输流格式为188 个字节,因此数据有效信号DEN 一直为高,因此CPLD 可以忽略这个信号,只控制接收传输流数据,而不用关心传输流的同步字节,所以帧同步信号PSYNC 也是一样可以忽略的。CPLD 将接收到的同步并行数据以传输流时钟OCLK 写入异步FIFO,当异步FIFO 达到半满状态时,CPLD 接收到异步FIFO 输出的半满信号HF,然后CPLD 给CY7B923 发出异步FIFO 可读信号,此时CY7B923就以27 MHz 的速率读取异步FIFO 中的数据;当异步FIFO中的数据快要被读空的时候,它会输出一个PAE(几乎空)信号,CPLD 接收到该信号后,向CY7B923 发送异步FIFO 不可读信号,防止异步FIFO 被读空。MPEG-2 传输码率的并行最大速度为27/8=3.375 Mbps,而读FIFO 速率为27 MHz,因此FIFO 不会发生溢出现象。考虑到有延时的存在,方案选用小容量的异步FIFO 芯片CY7C4285V。CY7B923 在异步FIFO 不可读时,向ASI 传输流中填充同步字节以维持270 Mbps 的恒定传输速率,最后串行数据经过缓冲/ 驱动就可以通过同轴电缆传送出去。功能框图如图2 所示。

图2 ASI 编码功能框图

在同步并行SPI 转换成异步串行ASI 的设计中,直接对SPI 数据进行ASI 编码处理,没有考虑到误码问题的存在,主要是考虑到SPI 数据是直接从专用数字电视MPEG-2 解码器输出的,没有经过远距离传输,认为没有误码存在,因而降低了ASI 编码逻辑控制的复杂度。

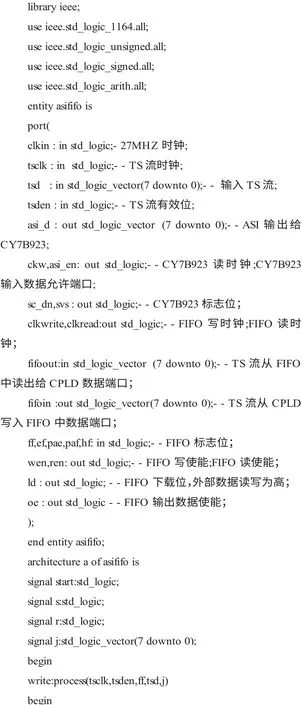

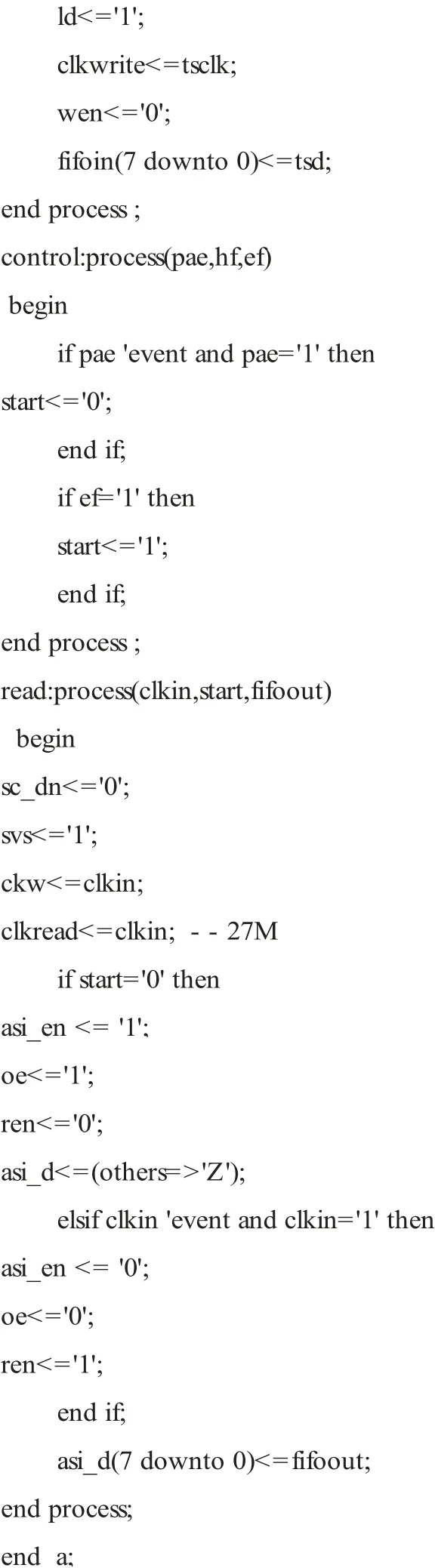

5 VHDL代码

6 结束语

方案很好地实现了SPI 到ASI 的转换,CPLD 软件设计灵活,为软件的升级和功能扩展提供了方便,产品模块面积小,便于安装,可直接应用于类似功能的需求,为相似应用提供了一个可实现的参考,并且已经成功应用于天津市德力电子仪器有限公司的量产机型DS8853Q 中,得到了客户的认可和好评。

[1]ISO/IEC 13818-1,CODING OF MOVING PICTURES AND ASSOCIATED AUDIO[S],1994.

[2]易 峰,何剑辉,全子一.DVB-C 视频传输接口ASI 的实现[J].电子技术应用,2004(1):58-59.

[3]赵伟民,赵照,薛丽军,吴 超,于 军.基于FPGA 的ASI 信号接收与发送的实现[J].中国有线电视,2006(21):2069-2071

[4]王飞飞,张雅绮,王书娟.基于FPGA 的DVB-ASI 设计[J].电子测量技术,2006,29(6):121-122.

[5]廖晓维,朱 红.应用CPLD 实现ASI-SPI 接口转换的方法[J].中国有线电视,2004(18):74-76.

[6]刘志勇,窦 衡,樊殊昱.基于FPGA 的视频接口转换实现[J].有线电视技术,2007(6):36-38.