基于选择进位32位加法器的硬件电路实现

高建卫

(北京外企徳科人力资源服务上海有限公司 上海 200335)

在数子电路设计中,高性能加法器是现代微处理器中的重要部件,是实时图象处理和数字信号处理的核心,同时也是微处理器中数据处理的关键路径,而且完成一次操作的周期影响微处理器得主频,因此人们对提高加法器的性能进行了大量的研究。

1 工作原理

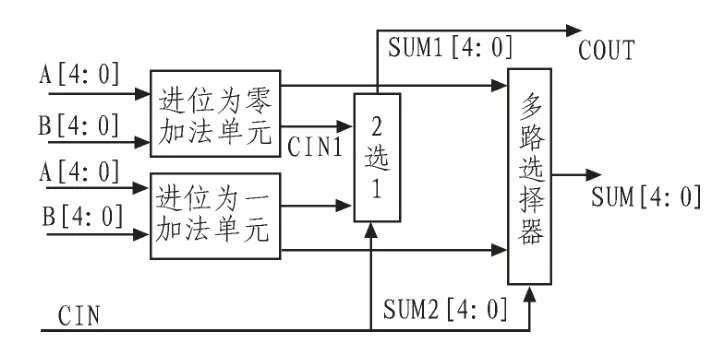

超前进位加法单元首先进行进位为零和进位为一的加法运算,由于加法运算是并行进行的运算速度相当快,硬件电路原理图分别为:加法单元,二选一,多路选择器[1]。如图1所示。

图1 加法运算硬件原理图Fig.1 Adder schematic

图1 中A,B为输入数据,CIN为进位输入,CIN1,CIN2分别为两加法单元产生的进位,SUM1和SUM2分别为两加法单元产生的和,SUM为两数最后之和,COUT为最后进位5[2]。

对于32位加法运算从原理上说,首先将其加法单元进行分组[3],也就是说把n位(一般n≥16)分成若干组不一定就是平均分组,因为平均分组以后,每一组加法单元都相同,电路运算花费时间相同,因而产生的选择进位信号的时间也相同,所以每一组加法单元的进位输出和最后和的输出都通过前一级的进位信号选择产生延时比较长。根据以上所述本文采用一种新的分组算法,也就是差额分组算法。首先将32位(作为例子,这里仅介绍32位,本设计可推广至2k位,K≥4,K∈N)进行差额分组,分别分为5位,6位,7位,8位,6位,形成阶梯形状运算单元,因为采用这种阶梯分组算法可以减少进位选择时间。例如:在运算的二组6位相加的同时,第一组5位也在进行相加,当第二组运算完成时,第一组运算结果和进位也以完成,通过第一组产生的进位选择第二组的运算结果和进位信号。以此类推可以得到第三,四,五组运算结果和最后进位结果。在运算32为加法时,其实与8位加法运算时间相当。

图2是超前进位(CLK)加法器的结构框架(作为例子,这里仅介绍4位CLA,本设计可推广至k位CLA,K≥2,K∈N)。图中,PG模块分别计算各组的进位传送函数(P)进位生成函数(G)得在值,与以往的超前进位算法相比版图容易实现,因为以往的超前进位算法计算各组的进位传送函数(P)和进位生成函数(G)用异或门和与门。

图2 超前进位加法器结构图Fig.2 Advanced carry selected adder

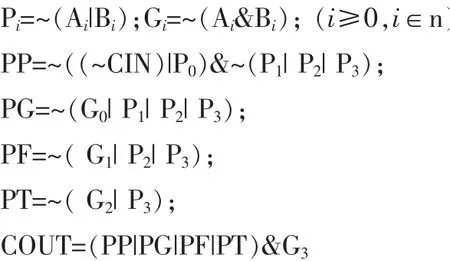

而本设计所用的超前进位算法计算各组的进位传送函数(P)和进位生成函数(G)用与非门和或非门。如图3所示即

图3 带进位生成函数的运算Fig.3 Operation with carry function

2 逻辑仿真

逻辑仿真是设计校验的重要步骤。利用ACTIVE HDL软件可直接提供这一功能。在ACIVE HDL中可以进行逻辑仿真和由SYNPILCITY提供综合后仿真,以及加入器件和线延时的时序仿真[4]。第一,在OPTION中选择上层模块,然后进行功能仿真。首先,用鼠标右击输入信号,弹出对话框选择STIMULATORS,可以加入任何想要的信号。第二,同样在SYNTHESIS的OPTION中选择上层模块和所需的器件(这里我们选用XILINX SPARTAN2提供的25200PQ208),然后进行综合后仿真。在此过程中我们可以通过SYNPLIFY进行电路优化,然后例如上面所述的相同的方法得到波形图。这时的波形图是已经加了器件延时后的结果。第三是在XILINX IMPLEMENTATIN中进行布局布线的时序仿真。在仿真前可以在OPTION中加入相应的约束条件,使其提高运行频率,图4即为仿真结果,这个仿真基本上与FPGA的仿真相接近,FPGA是近年来发展迅速的大规模可编程专用集成电路,它在它在电路设计中的应用使设计的电子产品达到小型化和集成化,大大缩短了设计周期,减少了设计费用,降低了设计风险。FPGA器件必将成为电子系统设计的重要手段,具有极其广阔的发展前景。

图4 仿真结果Fig.4 Simulation results

3 目标文件产生和器件下载

设计校验完成之后,利用ACTIVE HDL软件系统自动处理和生成目标文件(BIT文件),且可经一定方式(主动模式或被动模式)把目标文件配置于XILINX SPARTAN2芯片中,从而完成编程工作。

这里采用被动串行方式(PS)进行配置。专用下载电缆的一端与微型机USB口相连,另一端连至目标系统PCB板的配置插座,经一定的控制方式,把计算机内存中的目标文件配置于PCB板上的XILINX SPARTAN2芯片中[6]。

4 结 论

综上所述,这种选择进位加法器运行速度相当快,已经通过FPGA[7-8]验证,可以运行40—50兆的频率,如果制成芯片速度应比在FPGA上运行的更快,因为版图的布局布线比FPGA更加合理,基本上满足实际工程需要。

[1]RABAEY J M.数字集成电路设计透视[M].2版.北京:清华大学出版社,1999.

[2]Mittal M,Salama C A T.DPTL 4-6 carry looks head adder[J].IEEE J.of Solid State circuits,1992,27(11):1644-1684.

[3]于敦山.沈绪榜.32位定/浮点乘法器设计[J].半导体学报,2001(1):91-95.YU Dun-shan,CHEN Xu-bang.Design of a 32-Bit CMOSFix floating point multiplier[J].Chinese Journal of Semiconductors,2001(1):91-95.

[4]张亮.数字电路设计与Verilog HDL[M].北京:人民邮电出版社,2000.

[5]Agrawal V D.A tutorial on built-in self-test[J].part 1:principles.IEEE Design&Test of Computers,1993(2):73-82.

[6]Configuration and Readback of the Spartan-II and Spartan-IIE FPGA Families[M].Xilinx Company,2008.

[7]周建,祝连庆,张荫民.基于FPGA的脉冲光纤激光器功率控制系统设计[J].电子科技,2012,25(12):52-55.ZHOU Jian,ZHU Lian-qing,ZHANG Yin-min.Design of pulse fiber laser power control system based on FPGA[J].Electronic Science and Technology,2012,25(12):52-55.

[8]欧亚军,陈杰.基于FPGA的频率特性测试仪的设计[J].现代电子技术,2011,34(6):113-115.OU Ya-jun,CHEN Jie.Design of Frequency Characteristic Instrument Based on FPGA[J].Modern Electronics Technique,2011,34(6):113-115.