多发多收网络仿真器的FPGA实现及测试

郭 勇,陈艳玲

(南京北方信息控制集团有限公司产品研发中心,江苏南京211153)

0 引言

战术电台组网时,网络之间的拓扑结构经常会发生变化,为了验证电台之间的组网性能,需要根据节点之间的拓扑图生成网状的节点。常规条件下,生成多个网络节点需要很大的人力、物力,且拓扑图的更换不方便。目前介绍这方面设计的文献不多,文献[1-3]都是使用Open-Net等网络仿真软件等对链路层以上进行仿真,直接对物理层的数据通路的设计没有涉及。下面采用FPGA设计了一种网络仿真器,可以对拓扑图进行动态配置,以验证组网的性能,并可以对拓扑图进行快速修改。采用16个节点,因为节点数较多,测试信号多,如果没有逻辑分析仪采集大量的信号,则测试不是很方便。这里采用QuartusII自带的SignalTapII进行测试,能直观地验证设计的仿真器的正确性。

1 硬件设计结构及工作原理

网络仿真器由以下几个功能模块组成:一个5-32译码器,用来产生32个锁存使能信号,因为对每个节点的配置采用16位,为了方便与上位机通信,采用8位的分时输入的方式;一个32X8位的配置信号锁存器,16个节点拓扑生成器;一个发信号产生器,采用2种方式验证,一种是16个节点同时发送信号,同时验证16个节点的收信号情况;另一种是每个时刻只有一个节点发送信号即TDMA方式。因为所设计的仿真器输出管脚很多,需测试信号很多,硬件设计完成后,在开发板上采用QuartusII自带的SignalTapII进行测试,能直观地验证设计的网络仿真器的收发性能。

因为网络仿真器是在50 MHz的开发平台上设计验证,实际不需要那么高的时钟,因此设计一个4分频器,把时钟频率降为12.5 MHz。每个时刻只有一个节点发送信号,每个时刻写入一个8位的配置数据,因为总共16个节点,需要32个时钟完成一张拓扑图的配置,拓扑图配置完成以后,就可以验证各个节点的输入输出关系,设有全局复位信号,当需要产生并验证新的拓扑图时,按下全局复位键后,再重新配置,在32个时钟周期后,新的拓扑图产生。

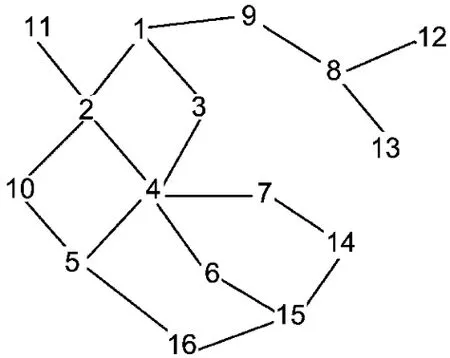

图1 拓扑图1

设拓扑图1如图1所示。各相邻节点之间互通,但是不相邻的节点不能互通,需要转发。比如节点1发出数据,节点2、节点3和节点9都能收到。节点4发数据,节点2、节点 3、节点5、节点6和节点7都能收到。按照节点配置规则,16个节点配置如下:节点1:0000_0001_0000_0110;这16位配置数据中,从右数,第2位、第3位和第9位为1,表明节点1与这3个节点是相连的。依次类推,可知其他节点的配置数据为:

节点2:0000_0110_0000_1001;

节点3:0000_0000_0000_1001;…;

节点15:1010_0000_0010_0000;

节点16:0100_0000_0001_0000,为节省篇幅,不一一列出。

拓扑图2如图2所示。拓扑图2的配置数据为:

节点1:0000_0000_1000_1010;

节点2:0000_0000_0001_0001;

节点3:0010_0000_0101_1000;…;

节点15:0001_0100_0000_0000;

节点16:0001_0010_1000_0000。

图2 拓扑图2

2 模块电路及整体电路的设计

2.1 节点拓扑生成器的设计

节点拓扑生成器的管脚定义如下:en1为配置低8位数据使能信号;en2为配置高8位数据使能信号[4]。data1[7..0]为某节点的低 8 位配置数据,data2[7..0]为某节点的高8位配置数据,对节点 1 来说,data1[7..0]=0000_0110,data2[7..0]=0000_0001。

TXD1、TXD2分别表示节点1发数据、节点2发数据等。对于每一节点,比如节点1,RXD1表示节点1收到节点1发出的数据,因为不能自发自收,所以如果TXD1发数据,则RXD1=0;RXD2表示节点1收到节点2发出的数据,RXD3表示节点1收到节点3发出的数据,如果节点1和节点3相连,则RXD3能收到数据,RXD3=TXD3。

当16个节点同时发数据时,节点1能收到节点2、节点3和节点9发出的数据。也就是说,RXD2=TXD2,RXD3=TXD3,RXD9=TXD9。整个仿真器需要16个节点,因此需要16个节点拓扑生成器模块,且方便节点数的扩展。

2.2 5-32译码器的设计

该译码器的设计是产生锁存信号,Y1~Y32信号为低时,dout<=din;当 Y1~Y32信号为高时,dout<=Q;锁存8位配置信号。每个节点的配置信号为16位,每个时刻写入8位配置数据,需要32个时钟[5]。

2.3 发送数据模块的设计

为了验证TDMA模式和多发多收模式下网络仿真器的性能,本文设计2种模式下的发射模块。TDMA模式就是一个时刻只有一个节点发送数据,多发多收模式是指同一时刻由多个节点同时发数据,也同时可以接收数据。

3 整体模块的仿真

该仿真器由1个发送数据模块(用于测试组网模式)、1个5-32译码器模块和16个节点拓扑生成器模块组成。该仿真器能快速地进行新拓扑图的配置和生成,既能仿真TDMA模式也能仿真多发多收模式[6]。假设t=t0时刻,需要生成拓扑图1,t=N+t0时刻,需要生成拓扑图2。在生成拓扑图2时,只需按下RST(复位键),再重新配置拓扑图即可。由于篇幅的限制,只给出多发多收模式下的仿真波形图。

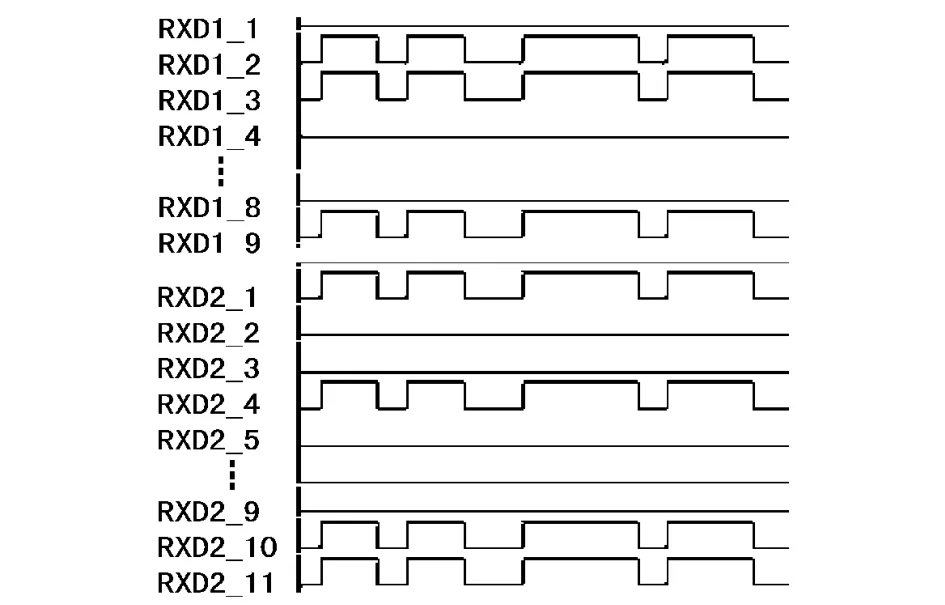

在多发多收模式下,16个节点同时发送数据,也同时接收数据。图3模拟了节点数不断增加的情况。因为仿真信号多,只截取节点1的输出波形图。由拓扑图1可知,节点1在发数据的同时,节点2、节点3和节点9能收到节点1发出的数据,表明节点2、节点3和节点9与节点1相连;节点2在发数据的同时,能收到节点1、节点4、节点10和节点11发出的数据,表明节点1、节点4、节点10和节点11与节点2相连,这也验证了拓扑图1正确地生成了。同理,在拓扑图 2形成后,RXD1_2,RXD1_4和RXD1_8有数据输出,表示节点2、节点4和节点8与节点1相连,同时RXD2_1和RXD2_5有数据输出,表示节点1和节点5与节点2相连,这也验证了拓扑图2正确地生成了。

图3 多发多收模式仿真波形

4 网络仿真器的SignalTapII测试

采用QuartusII自带的逻辑分析仪SignalTapII对多路并行输出的信号进行测试,既避免了使用昂贵的仪器,又能快速地验证所设计的功能电路的正确性。该方法适用于采用FPGA设计的其他复杂电路的测试验证。

性能测试在红色飓风III的开发板上进行,因为其主时钟为50 MHz,实际时钟速率不需要这么高,因此加上一个4分频的时钟模块,把时钟周期降为T=80 ns,该时钟作为后续各模块的工作时钟。

4.1 TDMA 模式

TDMA模式下SignalTapII接收波形测试图如图4所示。由图4可知,TDMA模式每个时刻只有一个节点发数据,当节点2发数据时,RXD2_1、RXD2_4、RXD2_10和RXD2_11能收到数据,表示节点1、节点4、节点10和节点11与节点2相连。当节点3发数据时,RXD3_1、RXD3_4能收到数据,表示节点1和节点4与节点3相连。这也验证了拓扑图1正确地生成了。

图4 TDMA模式下SignalTapII接收波形测试

4.2 多发多收模式

多发多收模式下SignalTapII接收波形测试图如图5所示。由图5可以看出,当16个节点同时发送数据,在拓扑图1完成后,节点1能同时收到节点2,节点3和节点9发出的数据,表明节点2,节点3和节点9与节点1相连;同时 RXD2_1,RXD2_4,RXD2_10,RXD2_11能收到数据,表明节点2与节点1、节点4、节点10、节点11相连。因此拓扑图1配置完成,对拓扑图2的分析,依此类推。

图5 多发多收模式下SignalTapII接收波形测试

5 结束语

采用FPGA设计了多发多收的网络仿真器,仿真器可兼容TDMA模式和多发多收模式的数据传输,设计的仿真器拓扑图动态配置快,拓扑图的节点增加方便,只需要修改译码器模块和增加拓扑生成器节点即可。因为仿真测试信号多,采用SignalTapII内嵌逻辑分析仪进行信号的测试,直观且方便地对所设计的网络仿真器进行测试,并验证了设计的正确性。采用的方法具有一定的适用性。

[1]龙 芳,黄进永.无线通信网络仿真器性能对比[J].计算机与网络,2006,30(9):211 -213.

[2]李学杰,金志刚,罗咏梅.基于Windows平台的无线网络模拟器设计与实现[J].计算机应用,2005,25(8):1 719-1 721.

[3]陈芳露,陆雯青.一种新型片上网络互连结构的仿真和实现[J].小型微型计算机系统,2010,5(5):883-886.

[4]西瑞克斯(北京).无线通信的Matlab和 FPGA实现[M].北京:人民邮电出版社,2009:46-52.

[5]史治国,洪少华.基于XILINX FPGA的OFDM通信系统基带设计[M].杭州:浙江大学出版社,2009:46-52.

[6]吴 丹,刘 衍.无线通信实验室信道仿真器的设计与实现[J].电子测量技术,2008,31(9):185-188.