一种高性能数字化采样新平台的研制

张 吉,谢 黎,汪世平

(国电南瑞科技股份有限公司,江苏南京210003)

随着新一代智能变电站的大力推进,继电保护装置数字化、集成化的趋势日益明显,对装置类产品性能的要求越来越高[1]。GOOSE、采样值(SV)和制造报文规范(MMS)三网合一概念的提出,是对装置类产品平台处理性能的考验,高速、大容量的数据实时采样要求使得传统平台在实时性及数据处理能力上后继乏力。传统的继电保护平台多采用双CPU架构或多核架构。双CPU架构[2,3]在数据共享、设备间隔扩展、时钟同步上存在很多技术壁垒,不利于智能变电站的推进和继电保护的发展。多核架构[4]适合于中低压保护测控装置,成本低、功耗少,但数据采样的实时性和处理能力有限,无法满足大容量、高速数据采样的需求。目前继电保护技术的发展趋势是向网络化、智能化、保护测控一体化、数据通信一体化方向发展,高速数据处理已经成为评价装置类产品重要指标之一[5,6]。因此需要一种高性能的采样平台,解决高速数据传输、大容量数据采样、保护算法和数据采样同步等问题。文中提出的高性能平台采用外设组件互连标准扩展 (PCIe)高速总线技术 (传输速度可达2.5 Gbps)解决了单CPU多路、大容量采样数据实时传输问题,并融入了直接内存操作(DMA)技术,使得数据处理更加高效,完全满足三网合一对数据吞吐率的要求;同时将保护采样和保护算法放在一块保护板上实现,提高了CPU的利用率,减少了数据传输延时,增强了平台的集成化,是适合于智能变电站推进的高性能数字化采样新平台。

1 高性能平台软硬件架构

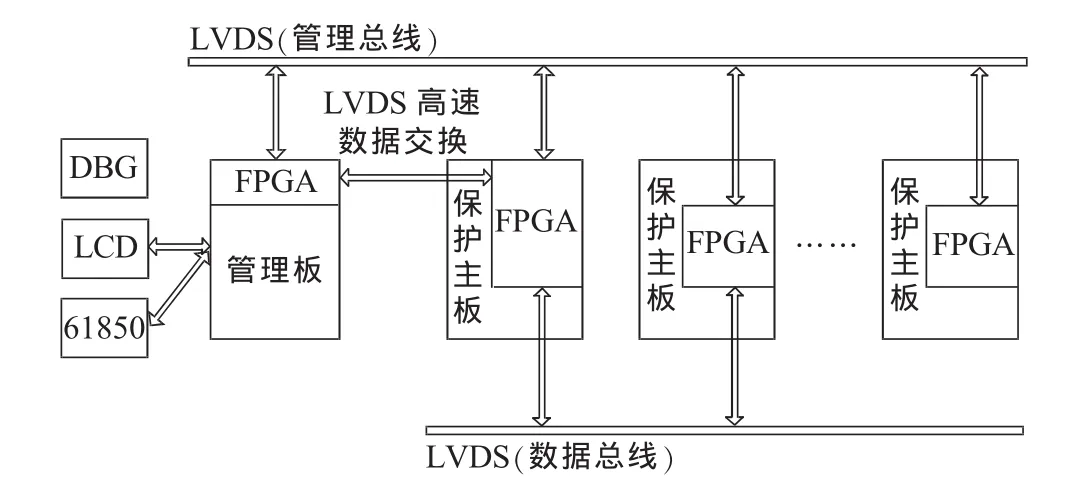

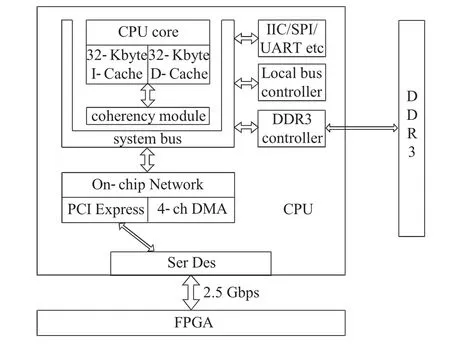

该高性能平台软件选择LINUX 2.6内核,硬件以高性能处理芯片P1011为基础进行扩充,平台总线框图如图1所示。

1.1 软件架构

图1 平台总线框图

软件架构主要采用注册机制,通过管理板统一管理,并随时更新保护主板信息。软件平台作为硬件与应用的接口,设计采用一体化结构,保护程序统一接口,大大提高了保护程序的可移植性。

高速数据交换总线是管理板和保护主板之间实时数据交换的桥梁。管理板负责对外通信、人机接口、运行信息、录波文件、日志管理等功能,信息的调用和获取都需要通过此接口与保护主板进行通信,实时性要求很高。

管理总线负责传送配置信息、注册信息及实时检测等功能,同时采用节点拓扑方式,实时检测是否有新板件加入或原板件移除,以备数据库更新管理。数据总线负责将保护从板信息实时传送给保护主板,由其进行统一管理和逻辑运算,同时保护从板也分担了一些保护主板的运算逻辑,既减少了主板的负担,又降低了数据交换流量。

1.2 硬件架构

新平台保护板硬件上采用一体化平台设计,主从板件硬件统一,兼容性强,且对外接口一致,只需根据工程实际需要进行配置板件数量即可;同时机箱底板硬件采用热插拔技术,可在带电情况下随时插拔板件,与软件架构配合,实现不断电基础上对装置间隔数量进行更改。

现场可编程门阵列(FPGA)在一体化设计上发挥了重要作用,保护主从板的功能区别通过FPGA得以实现。随着其在电力系统中的作用日益加大,高速内部总线、大容量的逻辑门电路,并且集成锁相环,可以对外部时钟进行倍频,主频可达几百兆以上,运算速度快,编程容易,应用灵活,高端FPGA芯片内部集成了很多模块,比如串行接口、差分接口、PCIe、介质访问控制层(MAC)等。

保护主从板通过配置不同的FPGA程序,实现硬件一体化设计,如图2所示。

图2 保护主从板一体化框图

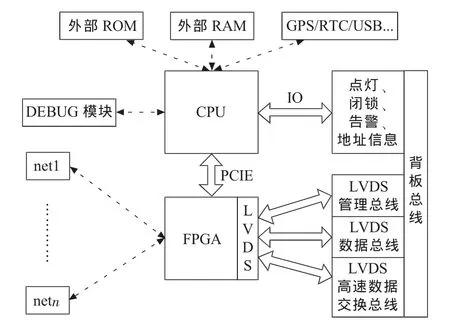

该系统中内部通信主要采用低压差分信号(LVDS)技术,实现开入开出、信号同步等实时性较高的数据传输。LVDS总线分为发送总线和接收总线,物理上都由一对差分线构成,实现点对点全双工通信,通信速率为100 Mb/s,其数据交换过程如下。

FPGA将LVDS串行数据经串并转换后写入FPGA中的接收缓存区,CPU通过自身并行总线访问接收缓存区获取接收数据。CPU通过自身并行总线将要发送的数据写入FPGA中的发送缓存区,FPGA从发送缓存区中取到数据后进行并串转换后通过LVDS总线往外发送。其收发过程如图3所示。

图3 LVDS差分信号传送

2 PCIe高速总线技术

随着现代处理器技术的发展,在互连领域中,使用高速差分总线代替并行总线是大势所趋。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

总线结构根本性的变革主要体现在以下两方面:一是有并行总线变位串行总线;二是采用点到点的互连独享带宽。将原并行总线结构中桥下面挂连设备的一条总线变成了一条链路,一条链路可包含一条或多条通路。没有专用的数据、地址、控制和时钟线,总线上各种事务组织成信息包来传送.地址空间、配置机制及软件上均保持与传统PCI总线兼容。

PCIe设备支持3种类型的地址空间,分别是存储器、IO和配置空间。配置成功后,可以直接通过地址对其他设备进行访问,实现数据共享。文中采用P1011芯片上的PCIe控制器,外接链路一个Lane,总线规范1.x,速率2.5 Gb/s。下面以LINUX2.6x为例,介绍其配置过程。

2.1 地址信息传递

LINUX启动获取板件硬件设备信息是通过设备生成树DTB来实现,而PCIe空间地址等信息也在其中进行配置,修改p1011rdb.dtc中PCIe对外空间地址及大小:

并通过命令:

dtc–I dts–O dtb p1011rdb.dtc>p1011rdb.dtb生成.dtb文件,写入指定ROM空间,系统启动时将按此配置对PCIe进行初始化。

2.2 控制器原理

PCIe采用数据包传输方式,通过事务层、数据链路层和物理层,将数据报文发送到对端,通常将PCIe两端称为源端设备(RC)和终端设备(EP)。在一些复杂系统中,通过桥接芯片可实现RC对多个EP的访问。

P1011所提供的PCIe控制器,可以更方便地对外设空间地址进行访问。通过配置Outbound寄存器可实现RC对EP的空间直接访问,通过Inbound寄存器可让EP直接访问RC空间。文中将CPU侧作为RC端,配置Inbound。

Inbound包括3个基本参数,由于EP无法对RC进行扫描,故此RC端需手动对Inbound所有参数进行配置,并要知道EP所有配置的PCIe空间地址,因此在编写程序前将所有空间进行分配好,统一管理,防止重叠。

PEXITAR:配置本板物理空间地址。

PEXIWBAR:配置PCIe虚拟空间地址。与EP访问的PCIe空间地址相对应。

PEXIWBEAR:Inbound属性。被访问的大小不能超过EP的Outbound空间大小,尤其多个EP出现后,要对空间地址及大小严格控制。

该平台CPU作为RC侧,首先对EP端进行扫描获取EP信息,之后对控制器进行初始化,将配置信息通过配置空间地址写入EP端,建立连接。

2.3 提高PCIe访问空间速度

UBOOT启动后初始化PCIe接口,建立与EP连接的高速通道,同时预留一片DDR3空间作为EP的访问空间,在传递给内核参数时保留此物理地址,使其不被MMU管理,这样RC与EP之间即可在此物理空间内进行实时数据交换。而在内核驱动中将PCIe操作部分删除,重新编写驱动程序,直接访问物理空间,减少中间环节,大大提高了对总线操作效率。

2.4 信号质量采集

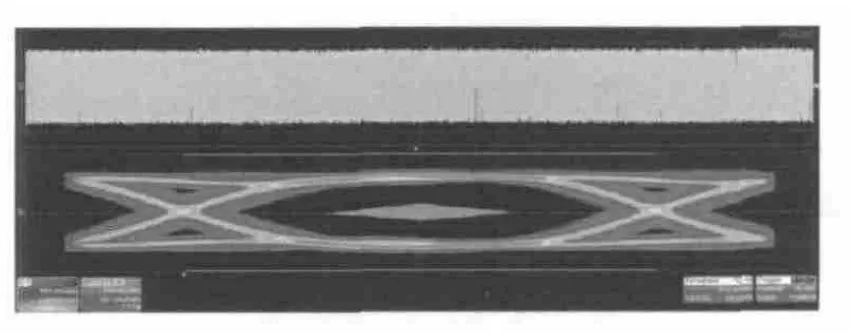

测量高速差分信号线噪音,保持良好的信号质量十分重要,文中采用Lecroy的高速示波器SDA系列,带宽 6 GHz,采样率为 40 GHz;探头 wave-link D620,带宽为6 GHz。常温下,同步时钟,预加重-3.5dB,取靠近CPU侧的引脚,基于PCIe1.x-RX眼图模板的眼图测试结果如图4所示。可以看出眼图质量很好:眼图比较对称、眼线很细、消光比适中、Q因子很高。

图4 PCIe效果眼图

3 DMA技术

DMA是现代CPU的重要特色,可对不同速度的外设进行访问,而不需要依于CPU的大量中断负载。DMA传输是将数据从一个地址空间复制到另外一个地址空间,而PCIe就是对外设空间的直接访问,将两者融合后,大大提升CPU与外设的交换速度,充分利用高速总线,如图5所示。

此平台CPU内部包含四路DMA控制器,采用其中一路作为高速数据传输。当启动DMA时,CPU将系统总线控制权交给DMA,建立DDR3控制器与PCIe之间的高速通道,完成数据交换后,DMA控制器立即将系统总线控制权交给CPU。

图5 DMA&PCIe传输框图

手动控制此过程会增加CPU负荷,因此采用链式DMA方式,将收发缓冲区按链式指针模式做成环形结构,只需将待处理数据放入缓冲区,由DMA控制器和CPU之间自行协商,完成传输过程,提高了程序处理效率。

DMA技术的引入,不仅提高了总线带宽利用率,还节省了CPU负荷,大大增强了平台的数据吞吐能力,实现高速数据的传输。

4 平台性能验证

采用此平台研发的装置顺利通过了国网就地化测试和六统一测试。高速的总线技术、强大的CPU处理能力,使GOOSE、SV数据共网得以实现,并顺利通过了新一代智能变电站的三网合一测试。尤其在网络风暴测试中,性能体现优越,过程层8个共网口接收报文的流量分别可达百兆,处理800 Mb/s流量报文的同时,还能正确处理GOOSE、SV的有效报文数据,且在此情况下CPU的负荷率远远没有达到此平台处理能力的上限,充足证明了此高性能平台的优越性。

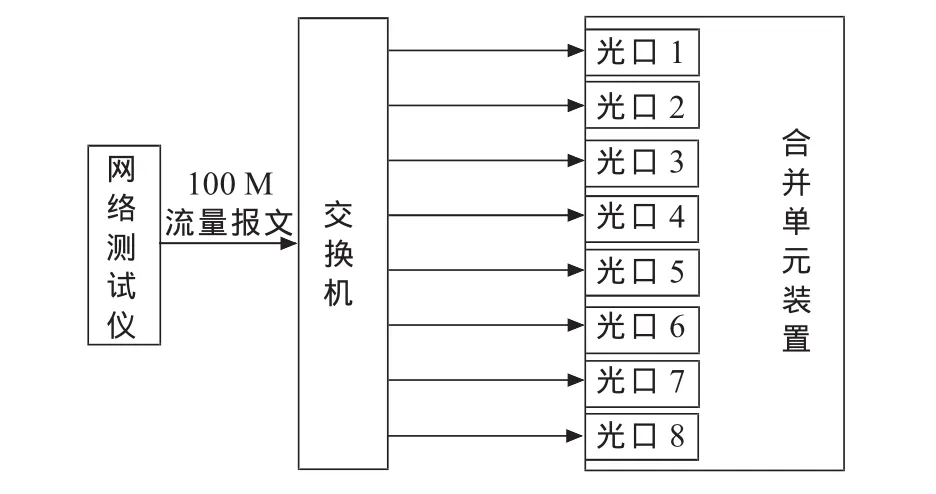

基于此平台的保护、测控及数字化装置,已成功应用于现场并已投运,处理能力强、吞吐率高、运行稳定,取得了用户的一致好评。以合并单元装置为例,测试平台采样速率及处理能力如图6所示。

图6 采集数据测试框图及数据

网络测试仪发送100 M流量报文,报文字长100字节,发送报文总数为48 065 480。经测试,8个光口接收报文总数为48 065 480个,丢包率为0,吞吐率达到800 Mb/s,达到测试目的。

5 结束语

采用高频差分总线,提高平台数据吞吐能力,是继电保护的发展趋势,文中所提出的高性能采样新平台有以下几大优势:采样容量大幅提升,PCIe技术的引入,使得网络吞吐能力大大加强,同时LVDS高速总线又使数据的实时交互上不存在瓶颈,可满足GOOSE、SV共网等大容量数据吞吐需求;处理速度提高,CPU主频达800 MHz,并支持硬件双精度浮点运算,大大提升保护逻辑处理能力,同时外部采用DDR3存储芯片,使平台整体性能大幅增强;集成化强,平台软件的注册机制可将各保护功能相互隔离,互不干扰,实现不同保护功能共存于同一台装置中,满足集成化的需求;扩展性能好。热插拔技术及软硬件一体化机制的引入,使装置平台对应用间隔的扩展可在线实现,平台的软件设计采用实时注册机制,增加间隔单元只需将配置好的保护从板插入机箱任意插槽,保护从板会向保护主板主动进行注册信息,方便快捷的融入系统;成本降低。由于高速总线的引入,使得板件可配光口数目得到提升,单板可同时处理组网口的最大数可达8个,大大减少板件数量,降低了装置整体功耗。PCIe总线技术和DMA技术的引入,无疑会给继电保护行业带来一场新的变革;同时,保护主板和保护从板的软硬件一体化设计,可在线实现更改间隔数量,也紧跟着智能变电站发展的步伐。

[1]国家电网公司.Q/GDW 393-2009 110(66)kV~220 kV 智能变电站设计规范[S].北京:中国电力出版社,2010.

[2]王海燕,徐云燕.一种基于DSP+MPC的数字化保护测装置[J].电力系统自动化,2010,34(9):112-114.

[3]彭志强,张小易,高 磊,等.智能变电站二次系统双重化配置技术应用分析.江苏电机工程,2012,31(4):34-39.

[4]周华良,夏 雨,汪世平,等.多核处理器在中低压保护测控一体化装置中的应用[J].电力系统自动化,2011,35(24):84-87.

[5]李 响,刘国伟,冯亚东,等.新一代控制保护系统通用硬件平台设计与应用[J].电力系统自动化,2012,36(14):52-55.

[6]张小飞,李佩娟,王洁松,等.智能变电站网络应用及测试技术研究.江苏电机工程,2012,31(4):34-39.