基于智能天线的UHF RFID接收机中IQ解调器的设计与实现

李建雄,刘 崇,范 超,史伟光,熊海青

(1.天津工业大学 电子与信息工程学院,天津 3003873;2.厦门软件职业技术学院,福建 厦门 361024)

基于智能天线的UHF RFID接收机中IQ解调器的设计与实现

李建雄1,刘 崇1,范 超1,史伟光1,熊海青2

(1.天津工业大学 电子与信息工程学院,天津 3003873;2.厦门软件职业技术学院,福建 厦门 361024)

论述了基于智能天线的RFID接收机中IQ解调的基本原理和实现方法.运用ADI公司PLL ADF4350输出本振信号与固定IF调制信号在IQ解调器ADL5380混频得到IQ基带信号,然后进行滤波和调理,并送入模数转换器AD7352中进行数字化.经测试表明:本设计在中心频率837.5 MHz的10 M带宽内可以很好地实现RFID接收机中IQ解调的功能.

射频识别;UHF RFID读写器;功率可程控;防碰撞

无线射频识别(radiofrequencyidentification,RFID)是一种自动识别技术,该技术通过无线射频方式获取物体的相关数据,无需与被识别物品直接接触即可完成信息的输入与处理,能实时、准确、快速地采集信息,因此得到了广泛的应用[1].根据其工作原理,RFID系统可分为电感耦合和电磁反向散射耦合.而UHF RFID是根据电磁反向散射耦合的原理,运用雷达原理模型,依据电磁波的空间传播规律进行通信.但UHF RFID依然存在诸多不足,如阅读距离近、标签易丢失、天线增益小等缺点.智能天线是利用多个天线阵元组合进行信号收发的天线,能够通过每个天线阵元中调制信号的幅度加权系数、频率和相位,来调整发射和接收天线的方向图,以便在不同的信号环境中达到性能最优,大大改善其性能[2].本文主要给出了基于智能天线的RFID接收机中IQ解调原理与实现方法,重点设计了PLL本振模块、IQ解调模块、ADC模块以及各模块之间的接口和滤波电路,并进行了各个模块的调试.

1 RFID阅读器的接收机的整体设计

本接收机基于18000-6C(EPC Gen2)标准,并且根据智能天线多波束切换的思想,引入了无源相控阵智能天线.它通过四单元天线阵耦合标签反射回来的电磁波.四路调制信号经过滤波后分别进行低噪声放大,然后与由DDS产生的频率、幅度、相位可控的本地信号进行混频,下变频至固定的频率和相位,同时完成幅度系数加权.四路IF调制信号经过功率合成器耦合成一路信号,并进行IQ解调成基带信号,然后通过AD进行数字化后,送入DSP进行数字基带处理,系统的整体框图如图1所示.

图1 基于智能天线的RFID接收机的整体框图Fig.1 Overall block diagram of RFID receiver based on smart antenna

2 IQ解调器的设计与实现

RFID系统的读写器与电子标签之间的通信采用的调制方式是ASK,标签反射回来的载波信号经过一定的空间距离传播后,会有一定的相位偏移,IQ解调则可以消除相位偏移造成的信号误判,与包络检波相比,可以大大减小误码率[3].

2.1 IQ解调器的总体设计

接收机前端调制信号经过第一次下变频后的固定IF调制信号与PLL产生的本振信号进行混频产生IQ两路信号,分别经过低通滤波和隔直流之后,进行A/D转换,送至DSP进行数字基带处理,其总体框图如图2所示.

图2 I/Q解调器的总体设计图Fig.2 Overall design of I/Q demodulator

2.2 IQ解调电路的设计

本设计中采用ADI公司的ADL5380作为IQ解调主控芯片.ADL5380是一款宽频带的正交IQ解调器,涵盖从400 MHz到6 GHz的RF/IF输入频率范围.差分RF输入提供功能良好的50 Ω宽带输入阻抗.同时其内部拥有集成的移相器可把输入的PLL输出的LO信号转化为相位相差90°的正交LO信号,其工作过程大致如下:PLL输出的LO信号和IF调制信号,通过差分方式输入到ADL5380中,ADL5380内部分别进行IQ下变频,然后通过差分方式输出IQ两路基带信号.其具体的设计电路图如图3所示,但图3中略去了电源退耦电容.其中由于IF调制信号为单端信号因此需要用一个Balun(TC1-1-13)完成信号由单端到双端差分的转化.

2.3 本振信号源的设计

PLL主要由鉴相器、环路滤波器、分频器、压控振荡器,如图4所示.

压控振荡器输出的频率经过N分频后输入到鉴相器中与参考时钟进行瞬时相位比较,并输出二者误差电流.误差电流经过环路滤波器的低通滤波后,将误差电流转化为直流电压,进一步来控制压控振荡器输出频率,这样就完成一个闭环反馈,进而达到频率的稳定,实现锁相的功能[4-5].

图3 ADL5380 IQ解调电路Fig.3 ADL5380 IQ demodulation circuit

图4 PLL的原理框图Fig.4 Block diagram of PLL

本设计中PLL采用ADI公司的ADF4350作为LO的主控芯片,ADF4350是一款带小数N分频和整数N分频锁相环频率合成器,覆盖从137.5 MHz至4 400 MHz的频率范围.它集成了电压控制振荡器(VCO)以及鉴相器和程控的分频器.外部输入时钟是20MHz,鉴相器的参考时钟为10MHz,输出837.5MHz,采用差分形式输出,同时解调器ADL5380使用基于多相滤波器的分相器,对PLL各次谐波比较敏感,因此要对ADF4350输出的本振信号进行差分低通滤波器.因此要对本电路主要进行环路滤波器和差分滤波器的设计.

PLL采用 ADI公司的 PLL专用设计软件ADIsimPLL进行设计,设置环路带宽为50 kHz,相位裕度为45°.根据实际元器件的数值,环路滤波器的实现电路以及在Multisim中仿真结果如图5所示.由图5中可知在51.282 kHz处幅度为-0.167 7,其对应相位值为-11.135°.

图5 环路滤波器的实现电路及频率响应Fig.5 Implementation circuit and magnitude frequency response of loop filter

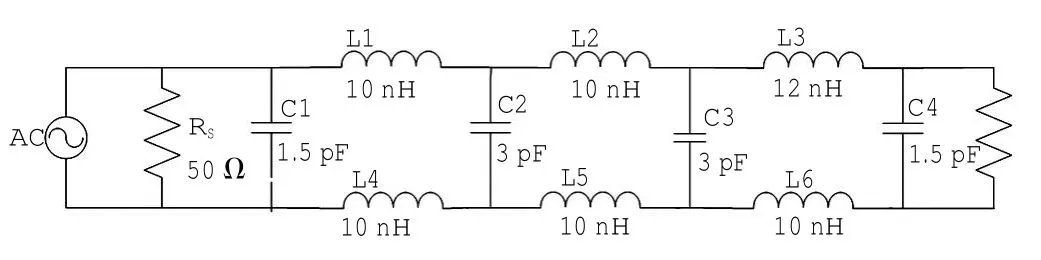

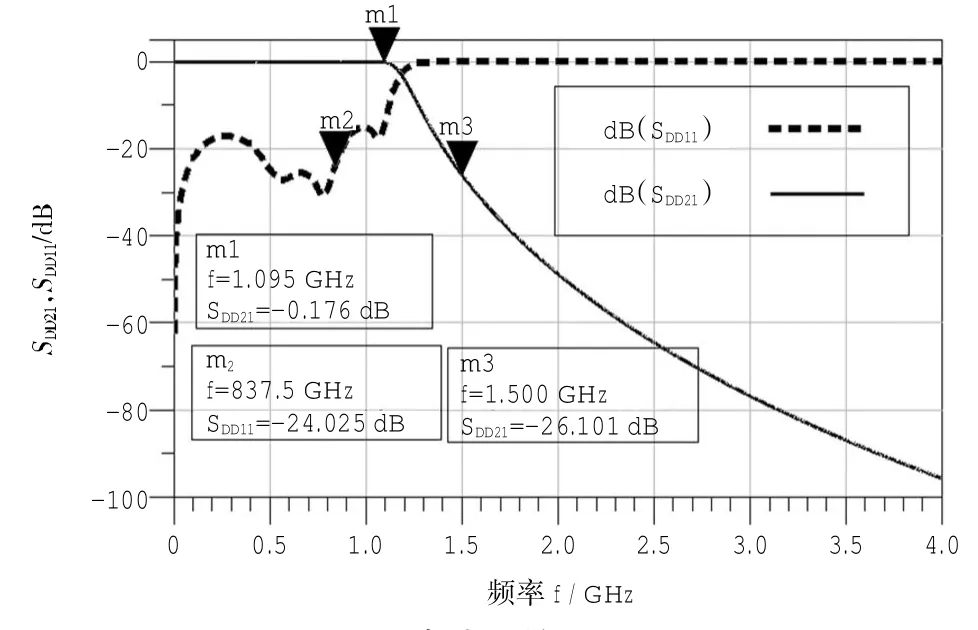

ADF4350采用差分信号输出,可以有效抗外界噪声干扰.根据PLL输出的频谱分析可知,未滤波前二次谐波为-36 dBm,三次谐波为-16 dBm,为了不影响ADL5380的特性,需要将其谐波功率降到-40 dBm以下,因此在ADF4350输出端需要差分滤波.ADF4350工作频率为837.5 MHz,二次谐波频率为1 675 MHz,故滤波器的通带截止频率为900 MHz,阻带截止频率为1 500 MHz,阻带插入损耗至少为-25 dB,根据插入损耗法设计滤波器原则,需要七阶切比雪夫等波纹滤波器[7].所设计差分滤波器电路和在ADS软件中滤波器混合模S参数SDD11、SDD21仿真结果如图6和图7所示.

图6 七阶差分滤波电路Fig.6 Seven order differential filter circuit

图7 差分滤波器的SDD11和SDD21Fig.7 SDD11and SDD21of differential filter

图7中的通带带宽为1.1 GHz,由于工程中软件仿真的带宽要比实际带宽高1.2~1.5倍,才能满足要求.

2.4 低通滤波器的设计

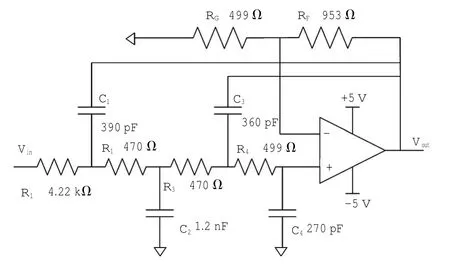

混频之后IQ路信号下变频为基带信号,采用低通滤波器进行滤波.在低频滤波中有源滤波器有着无可替代的优势,由于不需要电感,可以大大减少体积,且由于输入阻抗很高,可以大大减少电容的值.根据ISO18000-6C(EPC Gen2)标准,需要一个通带带宽为500 kHz、阻带频率为1 MHz的低通滤波器.本设计采用Sallen-Key拓扑结构,运用Filter Solution软件设计的有源全极点单放大器且增益的四阶巴特沃斯低通滤波器.根据元器件的实际值,用Multisim进行仿真调试最终得到的设计结果如图8所示[7-8].其幅频响应特性曲线如图9所示.

2.5 ADC的设计

本设计中ADC芯片选用的是ADI公司的AD7352.它是一款双通道、12位逐次逼近型ADC,具有最高达3MSPS的吞吐速率.AD7352内置2.048 V基准电压源,也可使用外部基准电压源.

为了给ADC提供适当的信号电平和功率,更好地发挥ADC的性能,在其输入端需要差分放大器进行驱动.本设计选用的芯片为AD8138,差分信号通过、端输入,配合外围电阻电容后可以提供适当的增益和滤波作用,同时输出的共模电压等于加载到输入端的电压.本设计中ADC的基准电压采用内部的基准电压即2.048 V,因此ADC输入端需要1.024 V的共模电压. ADC基准电压2.048 V在REFA端口输出,经过缓冲放大器AD8022之后,通过电阻分压,产生1.024 V的电压,为差分放大器AD8138提供端的输入电压,进而为AD7352提供适当的共模电平.其具体设计电路原理如图10、图11所示.其中差分放大器AD8138的增益为β=R70/R75,滤波特性为f=(2πR70C104)-1.

图8 四阶巴特沃斯有源滤波器电路Fig.8 Fourth-order Butterworth active filter circuit

图9 有源滤波器的幅频响应Fig.9 Active filter magnitude frequency response

图10 ADC差分驱动电路原理图Fig.10 ADC differential drive circuit schematics

图11 ADC AD7352原理图Fig.11 ADC AD7352 schematic

3 IQ解调器测试

测试的主要内容是测试各模块的输出特性.测试主要使用的仪器有Agilent N5182B MXG X系列射频矢量信号发生器、固伟GDS3354示波器、英数SA1030D数字频率特性分析仪、Agilent E4402B频谱分析仪和AgilentE5070B网络分析仪、Agilent 16801A逻辑分析仪.

差分滤波器主要工作在837.5MHz处,用网络分析仪测得的七阶单端滤波器传输特性S21如图12所示.

图12 七阶单端滤波器的幅频响应Fig.12 S21 of seventh-order single-ended filter

由图12可见,在837.5 MHz其输出特性S21的幅值为-2.034 7 dB,由于测试导线等设备误差,测试出结果与真实值稍微偏大.阻带衰减全部在-35 dB以下.

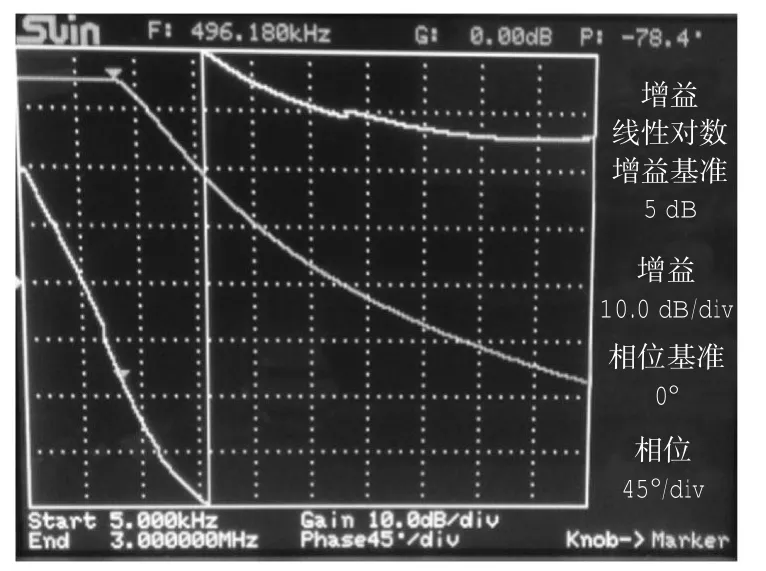

四阶有源低通滤波器用数字频率特性分析仪测得的幅频响应与相频响应如图13所示.

图13 低通滤波器的幅频和相频响应Fig.13 Low-pass filter amplitude and phase frequency response

由图13可知,在通带499.76kHz处其幅值为0.0 dB,阻带1 MHz处其幅值为,-21.60 dB.从相频特性可以看出,在通带内其相位基本成线性,群延时基本一样.可知滤波器设计的满足需求.

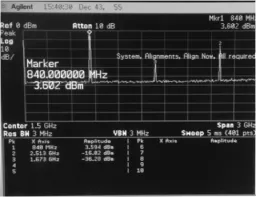

用频谱分析仪测得ADF4350 PLL未滤波前和滤波后的输出频谱如图14、图15所示.

图14 PLL未滤波前频谱特性Fig.14 PLL spectrum before filtered

图15 PLL滤波后频谱特性Fig.15 PLL spectrum after filtered

未滤波前其有明显的二次谐波-6.28 dBm、三次谐波-16.02 dBm.滤波后二次三次谐波已经没有,837.5 MHz处的输出功率为2.9 dBm,由于测试仪器的扫频分辨率,只能观察到838 MHz的频点.

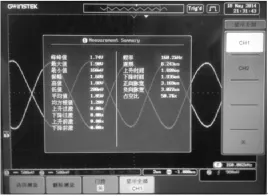

用示波器观察IQ解调后的信号经过低通滤波并经过差分驱动后输入ADC的波形如图16所示.

图16 输入到ADC的波形Fig.16 Waveform of input to the ADC

由图16可看出,其电压峰峰值为1.74 V,最小值160 mV,最大值1.98 V,满足ADC需要的电压范围0~ 2.048 V.

当输入高电平时,给ADC的SCK引脚16 M的时钟信号时,用逻辑分析仪测得ADC输出的其中一路信号如图17所示.

图17 ADC输出的数字信号Fig.17 Digital signal from ADC output

在CS为低电平时,每个时钟的下降沿时开始输出一位二进制数据.每一次采样需要16个时钟,其中前后各有两位 0补充,由图 17可知二进制为111010110010,对应该的十进制为3 762,计算出的模拟电平为1.881 V,与输入的一致即高电平.

4 结束语

IQ解调技术是一种抗干扰性强,适用性广的解调方法,可以大大减少误码率.本文主要完成了UHF RFID阅读器接收机中的IQ解调器的设计和调试。通过测试,在中心频率837.5 MHz的10 M带宽内,本设计可以实现-35 dBm灵敏度、500 k的奈奎斯特带宽及3 M的最大采样速率,可以很好的实现IQ解调的功能,同时其符合ISO18000-6C(EPC Gen2)标准.

[1]金荣洪,耿军平.无线通信中的智能天线[M].北京:北京邮电大学出版社,2006.

[2]FINKENZELLER K.RFID Handbook,Radio-Frequency Identi cation FundamentalsandApplications[M].2nded.NewYork:Wiley,2003.

[3]徐新.数字接收机中I/Q解调算法的研究[D].成都:电子科技大学,2005.

[4]张涛,陈亮.电荷泵锁相环环路滤波器参数设计与分析[J].现代电子技术,2008(9):87-90.

[5]高佩艳,丁恩杰.锁相环环路滤波器部分设计分析[C]//中国煤炭学会煤矿自动化委员会.中国煤炭学会自动化专业委员会学术会议论文集.中国江苏,2006.

[6] CHAN Ken.Design of Differential Filters for High-Speed SignalChains.[2007-01-01].http://www.ti.com/lit/an/slwa053b/ slwa053b.pdf.

[7] MOSCHYTZ G S.Low-sensitivity,low-power active-RC allpolefiltersusingimpedancetapering[J].CircuitsandSystemsII:Analog and Digital Signal Processing,IEEE Transactions on,1999,46(8):1009-1026.

[8]WILLIAMS Arthur B,TAYLOR Fred J.电子滤波器设计[M].北京:科学出版社,2008.

Design and implementation ofIQ demodulatorin UHF RFID receiversbased on smart antenna

LI Jian-xiong1,LIU Chong1,FAN Chao1,SHI Wei-guang1,XIONG Hai-qing2

(1.School of Electronics and Information Engineering,Tianjin Polytechnic University,Tianjin,300387,China;2.Xiamen Institute of Software Technology,Xiamen 361024,China)

The theory and implementation of the IQ demodulator in the RFID receivers based on the smart antenna is described.The IQ baseband signal is obtained from ADL 5380 by mixing the local oscillator signal generated by the PLL with the modulated signal.After a series of processes,such as filtering,the baseband signal is digitized in the ADC AD7352.The test result shows that the designed circuit can accomplish the IQ demodulation in the RFID receivers in 10 M bandwidth at the center frequency 837.5 MHz.

RFID;UHF RFID reader;power programmable;anti-collision

TP311

A

1671-024X(2014)05-0063-06

2014-07-02

国家自然科学基金项目(61372011)

李建雄(1969—),男,副教授,硕士生导师.E-mail:lijianxiong@tjpu.edu.cn