CMOS兼容高Q值微机电系统悬浮片上螺旋电感

卢冲赢,徐立新,李建华,,付博,欧修龙

(1.北京理工大学机电动态控制重点实验室,北京 100081;2.淮海工业集团有限公司,山西长治 046012)

CMOS兼容高Q值微机电系统悬浮片上螺旋电感

卢冲赢1,徐立新1,李建华1,2,付博2,欧修龙2

(1.北京理工大学机电动态控制重点实验室,北京 100081;2.淮海工业集团有限公司,山西长治 046012)

利用微机电系统(MEMS)表面微加工技术设计并制作了一种应用于无线电引信射频前端的CMOS兼容高Q值悬浮片上螺旋电感。电感的制作工艺在热预算和材料选择上均具有良好的CMOS兼容特性。通过采用铜金属悬浮线圈结构减小了片上螺旋电感损耗因素,显著提高了片上螺旋电感Q值。采用电磁场有限元分析软件HFSS对该电感模型进行了仿真研究,完成了悬浮片上螺旋电感的制备并进行了测量。测量结果表明:所设计的CMOS兼容MEMS悬浮片上螺旋电感Q值在1~7.6GHz测量频段均大于20,在7.4 GHz频段最大值达到了38.

兵器科学与技术;微机电系统;CMOS兼容工艺;悬浮片上螺旋电感;Q值;无线电引信

0 引言

微小型化的无线电引信可以在有限空间内使用更多元器件,使引信功能更加完善[1],CMOS射频集成电路(RFIC)将电感等无源器件集成在芯片上,可以有效减小引信射频前端电路体积和功耗,实现无线电引信的微小型化。但是基于传统CMOS工艺制作的片上螺旋电感的品质因数Q值很低,难以满足无线电引信的性能要求。由于低阻硅衬底和金属的固有损耗特性,当RFIC的工作频率达到109Hz或更高时,基于传统CMOS工艺制作的片上螺旋电感Q值通常不大于10,虽然公开发表的文献表明采用模块化接地保护结构[2-3]和多层金属互连[4]等方案可提高片上螺旋电感Q值,但是其效果并不明显,难以满足高性能RFIC的需求。

影响片上螺旋电感Q值的主要因素包括CMOS级低阻硅的衬底损耗和金属的欧姆损耗。采用微机电系统(MEMS)技术可以很好地消除上述2种损耗因素,提高片上螺旋电感Q值。现有的低阻硅衬底损耗的抑制途径主要有采用具有高电阻率的衬底[5-6]、增大氧化层厚度[7]、刻蚀低阻硅衬底[8-9]和采用表面悬浮线圈[6,10]等。而对于金属欧姆损耗通常的办法是采用比铝电阻率更低的铜制作线圈,并通过增大金属层的厚度以进一步减小欧姆损耗[7,11]。上述几种改进途径中,采用高电阻率衬底与现有的主流CMOS工艺不兼容;制作厚氧化层工艺难度大且成本较高;低阻硅衬底刻蚀会造成衬底机械性能薄弱,同时该方法并不能明显改善基于CMOS工艺的电感的欧姆损耗;基于表面微加工技术的表面悬浮线圈片上电感在已知报道中Q值性能最好,但现有悬浮电感制作工艺较为复杂[6], Yoon等[10]开发的多次曝光单次显影工艺简化了制作流程,但该方法需精确地设定曝光剂量、控制曝光时间,工艺参数控制较为困难。

针对上述问题,本文设计并制作了一种高Q值MEMS悬浮片上螺旋电感。电感的制作工艺基于后CMOS方法,在热预算和材料选择上均保证了良好的CMOS兼容特性,且工艺流程十分简洁。设计采用铜金属悬浮线圈结构以减小电感的衬底损耗和欧姆损耗,显著提高了片上螺旋电感Q值。

1 悬浮片上螺旋电感设计

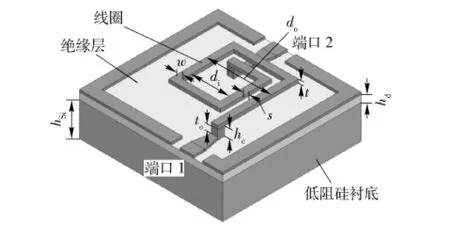

悬浮片上螺旋电感(以下简称为悬浮电感)结构示意图,如图1所示。电感由低阻硅衬底、绝缘层和线圈3部分组成,其中:低阻硅衬底的电阻率为10 Ω·cm,绝缘层包括了氧化层和空气层,线圈为铜金属材料。

设计得到的悬浮电感尺寸参数为:绕线宽度w为20 μm,绕线间距s为20 μm,绕线厚度t为10 μm,绕线内径di为170 μm,绕线外径do为250 μm,悬浮高度hc为20 μm,介质氧化层厚度hd为1.5 μm,硅衬底厚度hSi为500 μm,交叠间距to为10 μm.尺寸参数的设计既要考虑优化电感的射频性能,同时还要考虑实际工艺的实现能力。为了减小邻近效应导致的电流拥塞,电感采用了1.5圈的绕线,并设计了较大的绕线内径di和绕线间距s;同时为了减小线圈的串联电阻,并考虑到线圈的机械性能,设计了较大的绕线厚度t和宽度w.

图1 悬浮电感示意图Fig.1 Schematic diagram of suspended on-chip spiral inductor

为了说明悬浮线圈对电感损耗的抑制作用,建立了悬浮电感双端口集总参数模型,如图2所示。图中给出了元件:串联电感Ls,串联电阻Rs,交叠电容Cs,线圈空气层电容Ca,线圈氧化层电容Coxi,线圈低阻硅寄生电阻RSi,线圈低阻硅寄生电容CSi,端口1引线低阻硅寄生电阻Rp1-Si,端口1引线低阻硅寄生电容Cp1-Si,端口1引线氧化层电容Cp1-oxi,端口2引线低阻硅寄生电阻Rp2-Si,端口2引线低阻硅寄生电容Cp2-Si,端口2引线氧化层电容Cp2-oxi.与传统的CMOS片上螺旋电感集总参数单∏模型[11]相比,所建立的模型考虑了线圈悬浮后的Ca和非对称双端口电感的引线损耗。其中:Ca、Coxi、RSi和CSi表征了电感绕线部分的衬底损耗,Cp1-oxi、Cp1-Si、Rp1-Si和Cp2-oxi、Cp2-Si、Rp2-Si分别表征了端口1和端口2的引线衬底损耗,这些衬底损耗集总参数元件均可视为所表征对象在硅片表面所占据面积的函数,电感的欧姆损耗由Rs表征。

图2 悬浮电感集总参数模型Fig.2 Lumped parameter model of suspended on-chip spiral inductor

由图2可知,悬浮线圈和衬底之间的绝缘层电容包括Ca和Coxi,在忽略线圈厚度的前提下,Ca可近似由(1)式计算:

式中:l为线圈总长度;εa为空气介电常数。

由(1)式可知,随着hc的增大,Ca将减小,从而达到抑制线圈的衬底损耗的目的。根据微带线理论分析可知,增大线圈hc对于电感欧姆损耗同样具有抑制作用。研究表明:绕线中电流的分布与w/(hc+hd)有关。当w/(hc+hd)趋于无穷大时,电流主要集中分布在靠近低阻硅衬底的绕线底部;当w/(hc+hd)减小时,绕线两侧和远离低阻硅衬底的一侧的电流分布面积将增大,进而减小绕线的Rs[12].与增大氧化层厚度、硅衬底刻蚀等同样可以减小衬底损耗的改进途径相比,采用悬浮线圈的优势有:1)采用空气作为绝缘层对绕线和衬底间以及绕线之间的电容耦合效应的消除作用最为明显;2)悬浮线圈具有类似于空气微带线的结构,绕线四周的电力线分布较采用其他介质绝缘层要均匀,对于减小绕线串联电阻效果最好。

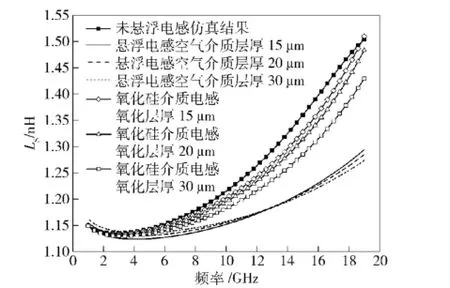

采用电磁场有限元分析软件HFSS对不同hc的悬浮电感进行仿真研究,并设计具有相同绝缘层厚度的以氧化硅作为介质的电感(以下称为氧化硅介质电感)作为对比。电感Q值和电感Ls值的仿真结果如图3和图4所示。

图3 电感Q值仿真结果Fig.3 Simulation results of Q-factor

Q值和Ls值可由(2)式和(3)式[13]计算得到:

图4 电感值Ls仿真结果Fig.4 Simulation results of Ls

式中:Y11为Y参数。

需注意的是,图3和图4中所标注的厚度尺寸均未包含厚1.5 μm的氧化层。

由图3可知,由于未悬浮电感的线圈和低阻硅之间仅有1.5 μm氧化层作为绝缘层,电感Q值峰值仅为18(1.5 GHz),之后即呈下降趋势,当频率大于6.6 GHz时Q值即小于10.与未悬浮电感相比,所有仿真的悬浮电感Q值在整个仿真频段内均大于20,电感Q值峰值达到了35以上,同时随着悬浮高度的增加,电感Q值呈现上升趋势,说明片上螺旋电感的衬底损耗和欧姆损耗因为线圈的悬浮得到了显著抑制。氧化硅介质电感Q值在1~4 GHz较低频段与悬浮电感Q值基本一致,但是在大于4 GHz后均显著小于具有相同介质层厚度的悬浮电感,由此可知采用空气作为介质对电感Q值的改善作用较采用氧化硅作为介质要明显。

由图4可知,在仿真频带内采用空气介质的电感Ls的变化率要小于采用氧化硅介质的电感,原因在于高频段空气介质电感的寄生效应要小于氧化硅介质电感的寄生效应。应说明的是,图3和图4中所得到的电感Q值和Ls值均由图1中的端口1计算得到。由于电感为非对称结构,而2个端口的引线损耗与端口的引线尺寸直接相关,由图2所示的悬浮电感集总参数模型可知,不同的端口计算得到的电感Q值并不相同。

2 CMOS兼容悬浮片上螺旋电感工艺

由于CMOS工艺对于设计规则修改和预处理硅片使用的严格限制,基于后CMOS方法设计了悬浮片上螺旋电感的CMOS兼容工艺。为了保证电感的MEMS工艺不会对已经完成铝金属化的CMOS电路性能造成损害,首先要求电感的MEMS工艺温度必须小于450℃,以免发生铝硅反应;其次要考虑所使用的工艺对CMOS电路的影响,如当采用KOH进行各向异性刻蚀体硅加工时,需对衬底间隙氧原子浓度和硼掺杂浓度进行调整,以确保足够的刻蚀腔质量和刻蚀速度,同时还需考虑铝金属互连和PSG钝化层的保护。为了保证CMOS电路与后CMOS制作工艺能够无缝衔接,还需设计合理的电路版图布局和MEMS工艺对准标记。

基于上述考虑所设计的悬浮电感制作工艺如图5所示。具体制作过程:

1)如图5(a)所示,在低阻硅衬底上利用等离子增强化学气相沉积生长一层厚1.5 μm的氧化硅作为绝缘层,而后在氧化硅上溅射一层铬/铜种子层,涂覆10 μm正胶,曝光显影后形成电感引线的电镀区域,电镀厚10 μm的铜作为电感引线。

2)如图5(b)所示,涂覆10 μm正胶,曝光显影后电镀厚10 μm的铜形成电感悬浮线圈支撑柱。

3)如图5(c)所示,溅射铜作为线圈电镀种子层,涂覆10 μm正胶,曝光显影后电镀厚10 μm的铜形成悬浮线圈结构。

4)如图5(d)所示,采用氢氧化钠溶液与丙酮溶液去除光刻胶,铬种子层采用铁氰化钾与氢氧化钠的混合溶液去除,铜种子层采用氨水与双氧水的混合溶液去除。去除所有的种子层和光刻胶后即得到所设计的悬浮电感,线圈悬浮高20 μm.

由图5可知,悬浮电感正胶表面微加工工艺避免了由于体硅加工造成的硅片机械性能薄弱和对CMOS电路的影响,多层电镀不需进行磨平工艺,所采用的空气介质不会产生CMOS工艺的材料兼容问题,同时最高工艺温度不超过350℃,不会导致已经完成铝金属化的CMOS电路发生铝硅反应,因此该工艺具有与CMOS工艺兼容的特点。与现有公开报道的悬浮电感表面微加工制作工艺[7,11]相比,该工艺具有明显的优势:1)在制作完一层结构后不需进行去胶和抛光工艺,而是在已有胶面上直接制作下一层结构,工艺非常简洁;2)制作成本较低,成品率较高,显微镜观察结果表明所制备的电感结构完好率在95%以上。电感结构尺寸测量结果表明:所设计的厚胶光刻工艺和电镀工艺均具有较高的精度,制作的电感线圈绕线宽度相对误差和绕线间距相对误差均不超过5%,绕线厚度相对误差不超过15%,说明该工艺制备的电感与设计具有优异的一致性。

3 悬浮片上螺旋电感制备与测量结果

所制备的悬浮电感的扫描电镜(SEM)图如图6所示。电感结构的设计尺寸参数同图1.

为了尽量减小损耗,电感线圈仅由2个立柱支撑,牺牲了部分机械性能。应用于引信的MEMS器件必须具备足够的抗过载性能,引信用MEMS开关等器件在过载作用下的响应已进行了相关研究[14],但对MEMS悬浮螺旋电感在高过载作用下的响应研究还较少。图6所制作的悬浮电感线圈在常规工艺过程中并未出现明显的结构变形或是线圈脱落现象,对于悬浮线圈进一步的可靠性测试正在进行。由于实际电路中应用的片上螺旋电感并不包括图6中所示的共面波导(CPW)端口部分,因此需采用去嵌入测量方法去除CPW端口的寄生效应。CPW端口的寄生效应包括寄生电容、寄生电阻和寄生电感。其中,寄生电容可采用开路去嵌入结构去除,寄生电感和寄生电阻则需采用短路去嵌入结构去除。为了简化测量与数据处理,图6设计了尺寸较大的端口,且减小了线圈到端口的引线长度,使得端口的寄生电感与寄生电阻很小,从而电感的去嵌入处理只需要去除端口的寄生电容即可。所设计的开路去嵌入结构如图6(a)所示,进行去嵌入处理后得到如图6(b)虚线框内所示结构的射频性能。虚线内结构包括了线圈、支撑柱和下层的引线,因此测量结果很好地表征了实际的应用情况。悬浮电感的测量结果如图7和图8所示。

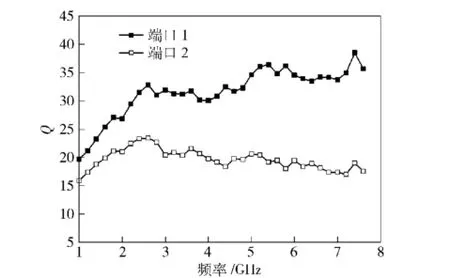

图7 悬浮电感Q值测量结果与仿真结果Fig.7 Measured and simulated Q-factors of the suspended on-chip spiral inductor

由图7可知,在进行了去嵌入处理后,悬浮电感测量得到的Q值在整个测量频段内均大于20,在7.4 GHz左右电感Q值最大值达到了38左右。与传统的CMOS片上螺旋电感Q值仅为5~10相比,悬浮电感Q值得到了极大提高,说明由于采用了厚铜金属和悬浮线圈结构,电感的衬底损耗和欧姆损耗都得到了显著抑制。测量得到的Q值较HFSS仿真结果稍小一些,主要原因在于MEMS工艺中存在的固有误差造成的实际结构尺寸和模型结构尺寸存在差异,这些固有的误差包括曝光误差、显影误差、电镀误差等,但总体而言,测量与仿真结果吻合良好,说明该设计方案和工艺是可行的。同样由图7可知,在未进行去嵌入处理时,由于电感测量结果包含了CPW端口的寄生电容效应,所得Q值较进行了去嵌入处理所得Q值要低得多,在整个测量频段内Q值随频率增加呈下降的趋势,在6 GHz以后Q值仅5左右。为了简化电感的制备、测量及数据处理过程,在版图设计时适当增大了端口信号线的宽度以减小端口的寄生电感和寄生串联电阻,这样只需进行开路去嵌入测量以去除端口的寄生电容。这种简化测量方法通常应用于相对端口而言尺寸较大的MEMS结构测量,而对于更小的MEMS结构,应该设计相应的短路去嵌入结构以去除测量端口的寄生电感和寄生串联电阻。

图8 端口1与端口2的Q值测量结果Fig.8 Measured Q-factors of port 1 and port 2

由于悬浮电感为非对称结构,由图2悬浮电感集总参数模型可知仅由端口1得到的测量结果并不能完整表示所设计的电感的双端口性能。由图8可知,基于端口2得到的Q值比基于端口1得到的Q值要小很多,基于端口2得到的Q值峰值仅为20左右,且在频率大于2.5 GHz后即随着频率的增大而减小。产生这种差异的主要原因在于悬浮电感的端口2包含了一段引线部分,而该引线部分会显著增大电感的衬底损耗和欧姆损耗。因此在实际的应用中,以电感的内圈引出线(即端口2方向)为接地端可获得更好的电路性能。

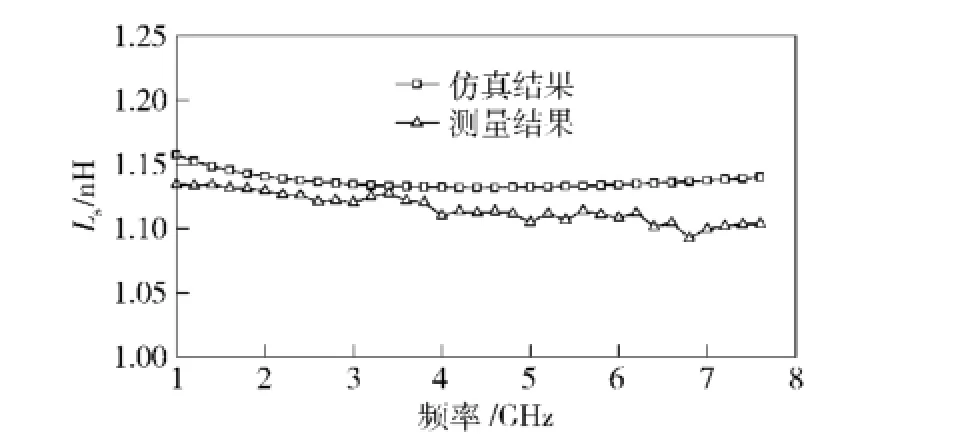

图9所示为电感值Ls的测量结果与仿真结果。由图9可知,在测量频段内测量结果与仿真结果吻合较好,说明所制作的电感结构与尺寸与设计要求相符,即该设计方案与工艺可行。

图9 悬浮电感值Ls测量结果与仿真结果Fig.9 Measured and simulated Lsof the suspended on-chip spiral inductor

4 结论

本文设计了一种应用于无线电引信射频前端、与CMOS工艺相兼容的高Q值MEMS悬浮片上螺旋电感,并对悬浮电感的设计理论进行了研究,采用CMOS兼容的MEMS工艺制作了电感。仿真结果和测量结果均表明:所设计的电感具有优异的Q值性能,在1~7.6 GHz测量频段内,电感Q值均大于20,峰值达到了38左右,较传统的CMOS片上螺旋电感有很大提高。同时,讨论了去嵌入测量方法和非对称结构电感双端口性能的差异,并认为在实际的应用中,采用内圈引出线作为接地端可获得更好的电感Q值性能。

References)

[1] 崔占忠.引信发展若干问题[J].探测与控制学报,2008, 30(2):1-4. CUI Zhan-zhong.Some issues on the fuze development[J].Journal of Detection&Control,2008,30(2):1-4.(in Chinese)

[2] Yue C P,Wong S S.On-chip spiral inductors with patterned ground shields for Si-based RF ICs[J].IEEE Journal of Solid-State Circuits,1998,33(5):743-752.

[3] Lin Y S,Chen C Z,Liang H B,et al.High performance on-chip transformers with partial polysilicon patterned ground shields (PGS)[J].IEEE Transactions on Electron Devices.2007, 54(1):157-160.

[4] Xu X M,Li P L,Cai M,et al.Design of novel high-Q-factor multipath stacked on-chip spiral inductors[J].IEEE Transactions on Electron Devices,2012,59(8):2011-2018.

[5] 王建卫,蔡坚,窦新玉,等.陶瓷基板上的集成微电感模型与制作[J].半导体技术,2009,34(11):1074-1077.

WANG Jian-wei,CAI Jian,DOU Xin-yu,et al.Model and fabrication of integrated micro-inductors based on ceramic substrate[J]. Semiconductor Technology,2009,34(11):1074-1077.(in Chinese)

[6] 赵小林,王西宁,周勇,等.双层悬空结构射频微电感制作研究[J].微纳电子技术,2005(1):30-32.

ZHAO Xiao-lin,WANG Xi-ning,ZHOU Yong,et al.Fabrication and performance of double layer suspended spiral inductor[J].Micronanoelectronic Technology,2005(1):30-32.(in Chinese)

[7] Raieszadeh M,Monajemi P,Yoon S W,et al.High-Q integrated inductors on trenched silicon island[C]∥Proceedings of the 18th IEEE International Conference on Micro Electro Mechanical Systems.Atlanta:IEEE,2005:199-202.

[8] Ozrur M,Zaghloul M E,Gaitan M.Optimization of backside micromachined CMOS inductors for RF applications[C]∥IEEE International Symposium on Circuits and Systems.Geneva:IEEE, 2000:V185-V188.

[9] Lin J W,Chen C C,Cheng Y T,et al.A robust high-Q micromachined RF inductor for RFIC applications[J].IEEE Transactions on Electron Devices,2005,52(7):1489-1496.

[10] Yoon J B,Choi Y S,Kim B I,et al.CMOS-compatible surface-micromachined suspended-spiral inductors for multi-GHz silicon RF ICs[J].IEEE Electron Devices Letters,2002,23(10):591-593.

[11] Yue C P,Wong S S.Physical modeling of spiral inductors on silicon[J].IEEE Transactions on Electron Devices,2000,47(3): 560-568.

[12] Faraji-Deza R,Chow Y L.The current distribution and AC resistance of a microstrip structure[J].IEEE Transactions on Microwave Theory and Techniques,1990,38(9):1268-1277.

[13] Tai C M,Liao C N.Multilevel suspended thin-film inductors on silicon wafers[J].IEEE Transactions on Electron Devices,2007, 54(6):1510-1514.

[14] NIE Wei-rong,XI Zhan-wen,XUE Wei-qing,et al.Study on inertial response performance of a micro electrical switch for fuze [J].Defence Technology,2013,9(4):187-192.

CMOS-compatible High-Q Micro-electro-mechanical System Suspended on-chip Spiral Inductor

LU Chong-ying1,XU Li-xin1,LI Jian-hua1,2,FU Bo2,OU Xiu-long2

(1.National Key Laboratory of Science and Technology on Electromechanical Dynamic Control,Beijing Institute of Technology, Beijing 100081,China;2.Huaihai Industries Group Co.Ltd,Changzhi 046012,Shanxi,China)

A COMS-compatible high Q-factor suspended on-chip spiral inductor used in the radio frequency front-end of radio fuze is designed and fabricated using the micro-electro-mechanical system (MEMS)surface-micromachining technology.The fabrication process of inductor is compatible with CMOS in the aspects of both thermal budget and materials.The loss factors of on-chip spiral inductor are reduced by using a suspended copper coil,and the Q-factor is significantly improved.The improved inductor model is analyzed by the electromagnetic finite element analysis software HFSS.The MEMS suspended on-chip inductor is measured.The measurement results show that the Q-factor of inductor is more than 20 in the frequency range of 1~7.6 GHz and reaches 38 at 7.4 GHz.

ordnance science and technology;micro-electro-mechanical system;COMS-compatible process;suspended on-chip spiral inductor;Q-factor;radio fuze

TN 40;TN405

:A

1000-1093(2014)05-0634-06

10.3969/j.issn.1000-1093.2014.05.009

2013-06-18

卢冲赢(1986—),男,博士研究生。E-mail:lcylyr@bit.edu.cn;

徐立新(1969—),男,研究员,博士生导师。E-mail:lxxu@bit.edu.cn