JESD204B接口协议中的加扰电路设计

霍兴华,姚亚峰,贾茜茜,陈 登

(中国地质大学(武汉)机械与电子信息学院,湖北武汉430074)

JESD204B接口协议中的加扰电路设计

霍兴华,姚亚峰,贾茜茜,陈 登

(中国地质大学(武汉)机械与电子信息学院,湖北武汉430074)

数据加扰有助于避免在高速串行传输中出现频谱杂散,对JESD204B协议规定的加扰电路进行了具体设计和实现。首先详细描述了协议要求,以8位并行加扰为例阐述了自同步加扰和解扰的电路原理,最后根据解扰器输出状态与初始状态值有关这一问题提出了改进的电路结构以及关键设计代码。仿真结果表明,该改进电路完全满足协议要求,可应用于JESD204B规范的高速串行接口电路设计。

JESD204B;Serdes接口;自同步扰码与解扰;并行扰码与解扰

JESD204B协议是2011年修订的一种用于数据转换器和逻辑器件内部互连的行业新标准,可同时支持多通道同步和串行传输,最高传输速率可达12.5 Gbit/s。该协议提供了一组先进功能,为整个电子行业的高速数据采集提供了一种新的设计方法[1]。

协议规定的扰码与解扰电路位于数据传输层与数据链路层之间。在传输层数据成帧之后,则可以对数据进行扰码。扰码可以有效防止连续的相同字节之间的相关性,防止在模拟域出现相关杂散频谱。杂散频谱会引起电磁干扰,易导致数据产生误码,影响数据传输的有效性。同时扰码还有利于锁相环从比特流中顺利提取时钟信号,以及抑制信号传输时的直流分量等。

本文根据JESD204B协议规范,在详细分析加扰电路原理的基础上,具体设计和实现了一种自同步的并行扰码与解扰电路。该设计通过添加使能信号,可以有效解决解扰电路最初的一些输出值与线性反馈移位寄存器的初始状态值有关的问题,方便收发两端的同步。最后还给出了电路的关键设计代码,仿真结果表明了该电路功能正确性和电路的可综合性。

由于JESD204B是最近几年才提出的一种高速串行接口电路规范,还没有看到该协议所规定的加扰电路实现的相关文献,因此本文对高速串行接口的加扰电路设计应具有一定参考作用。

1 设计原理

1.1 扰码和解扰原理

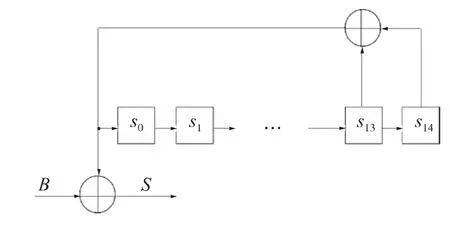

扰码通常是通过移位寄存器产生,而移位寄存器的阶数由扰码多项式决定。JESD204B协议规定扰码多项式为1+x14+x15,故需采用15阶移位寄存器。串行扰码可分为同步扰码和自同步扰码[2],两者区别在于输入到线性反馈移位寄存器的序列不同。同步扰码的实质是让输入比特与随机数产生器所产生的一位随机比特进行异或来产生扰码的输出比特,其原理如图1所示。

图1 同步串行扰码原理框图

JESD204B协议规定的扰码方式需采用自同步扰码方式,自同步的扰码与解扰电路结构如图2所示。

可见,对于自同步串行扰码,每次扰码输出都是由移位寄存器第13位和第14位比特进行异或,得到的结果再与输入比特值进行异或而得到的。

图2 自同步串行扰码与解扰原理图

由于传输层数据成帧之后,往往是以8位或16位数据进行并行传输的,所以必须在串行扰码的基础上,设计8位并行或16位并行的扰码与解扰电路。下面将在串行扰码表达式的基础上推导并行扰码的逻辑表达式。

串行扰码每次只处理一个比特。在每个时钟周期,移位寄存器只移一位[3]。对于串行扰码,假设此刻输入比特是bn,输出比特是an,则移位寄存器s0中存储的比特是 an-1,依此类推移位寄存器 s14中存储的比特是an-15,因此an=bn+an-14+an-15。则下一个时刻的输入比特是bn+1,输出比特是an+1,此时移位寄存器s14中存储的比特是an-14,因此an+1=bn+1+an-13+an-14。

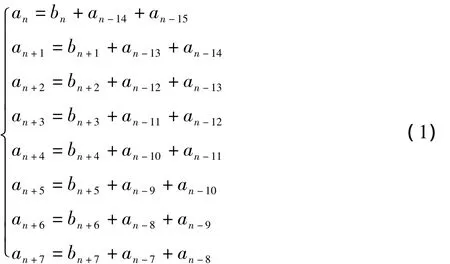

对于处理宽度为8的并行扰码过程,每次需处理8个比特。在每个时钟周期,移位寄存器需移8位。假设此刻输入8个比特bn+7,…,bn,利用上面的串行扰码的推导,则有

式中:加号均为模二加。

下一个时刻,15阶的移位寄存器状态将由an-1,…,an-15变为an+7,…,anan-1,…,an-7,移动了8位。可以看出输入的8比特bn+7,…,bn,经并行扰码之后变为an+7,…,an并行输出。

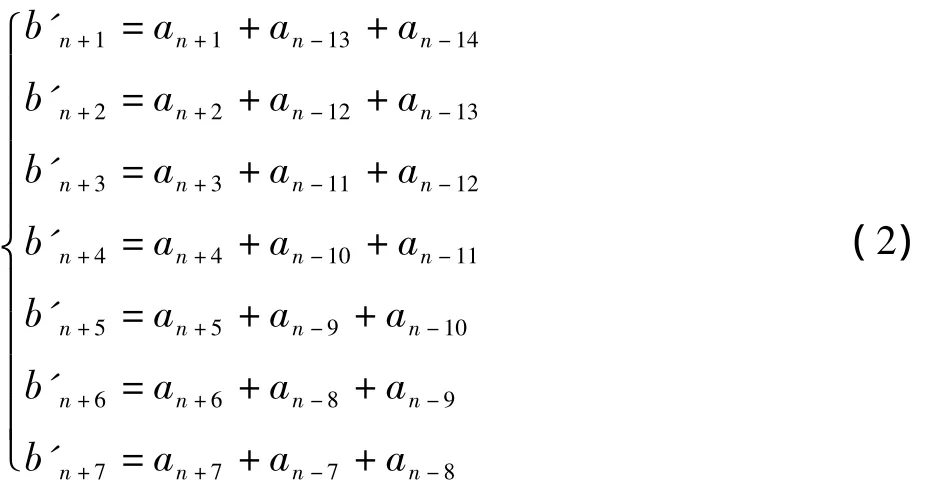

对于解扰器来说,输入的8比特就是扰码之后的an+7,…,an,当an到达时,b'n=an+an-14+an-15。

依此类推

解扰是扰码的逆过程,所以解扰结果必须与输入数据相同才证明解扰是正确的,即b'n+7,…,b'n与bn+7,…,bn必须相同。

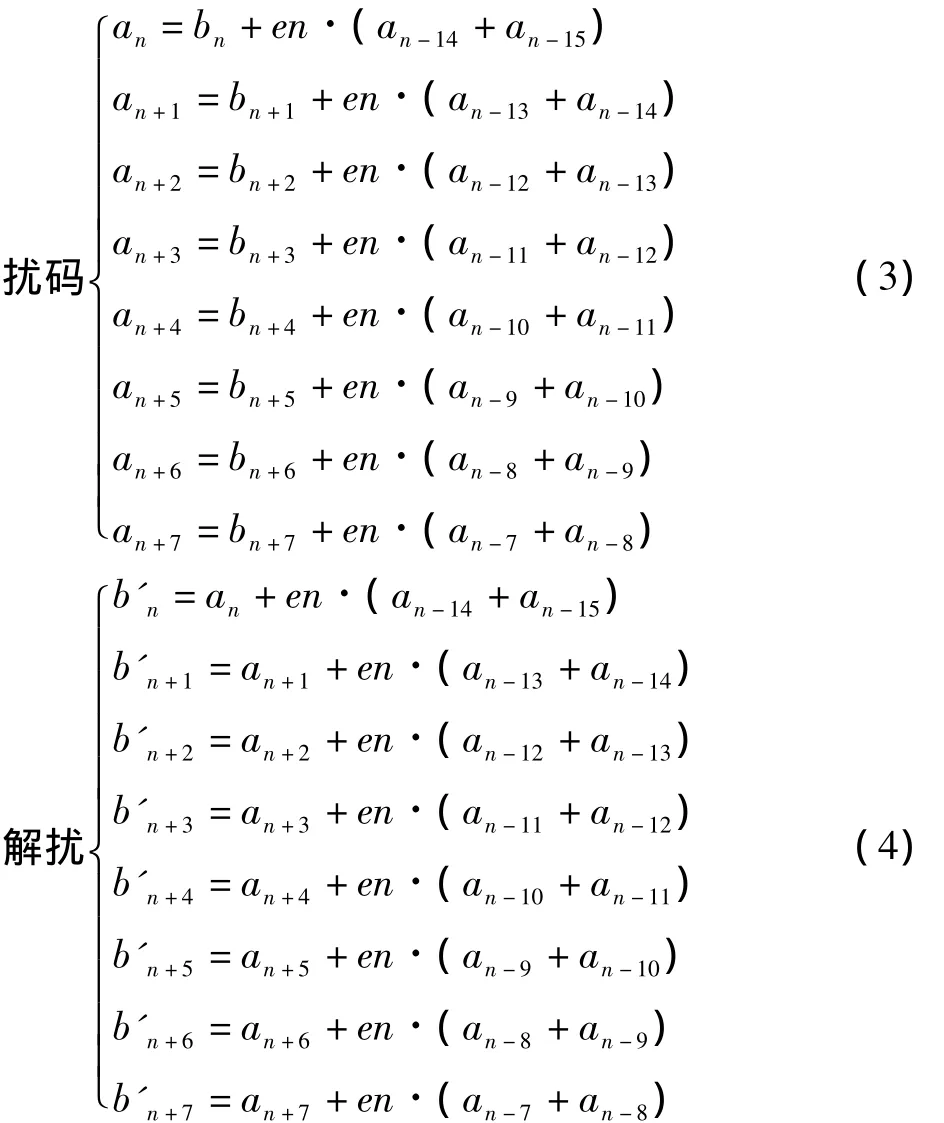

由上面两组公式可以看出,只要保证扰码器和解扰器中对应的各个移位寄存器中的值相同即可,即扰码器的移位寄存器状态与解扰器的移位寄存器状态必须达到同步。由于协议中并没有规定移位寄存器的初始值,所以要解决解扰器输出与移位寄存器初始状态值有关的问题。为了不让解扰电路的输出与初始状态值有关,便于收发两端的同步,下面给出一种改进的并行扰码与解扰电路结构。

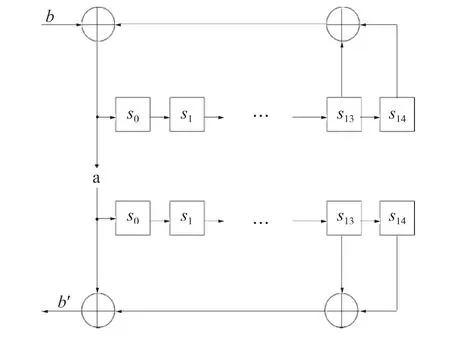

1.2 改进的并行扰码与解扰电路

前面已经提到,协议规定的扰码与解扰模块位于数据传输层和数据链路层之间,在传输层数据成帧的过程中,发射器为了与接收器之间达到同步会在用户数据前发送编码数据同步序列和初始通道校准序列,协议要求在这两种序列发送的过程中是不能进行扰码的,在此过程中扰码器和解扰器处于非工作状态。另一方面,在用户数据到达后,扰码器和解扰器要开始工作,如果此时扰码器与解扰器中移位寄存器的初始状态值不同,会导致接收端不能正确恢复用户数据前两个字节值[4]。

为了避免前两个字节值的丢失,在扰码器与解扰器的移位寄存器同步之前,用户数据前两个字节可以在无扰码操作的情况下传输,两个字节之后,扰码器与解扰器移位寄存器的状态就会由用户数据的前两个字节所确定,这时能够保证达到同步状态。

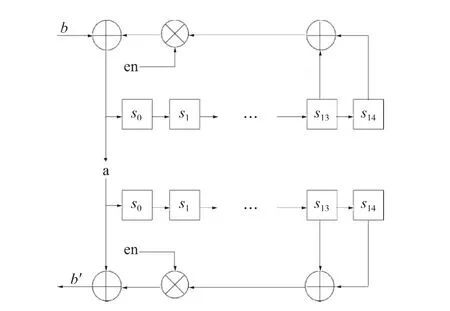

基于以上考虑,提出一种带使能信号的改进扰码与解扰电路结构[4],如图3所示。

此时扰码器和解扰器都加入了一个使能控制信号。当en信号为低电平时,输入不经扰码直接输出;同理在接收端也不用解扰。两个字节之后,扰码器和解扰器移位寄存器中的状态都是由输入决定的确定值,此时可将en信号电平拉高,进行正常的扰码与解扰操作。改进之后的扰码与解扰公式为

图3 带使能信号的扰码和解扰电路

2 设计实现

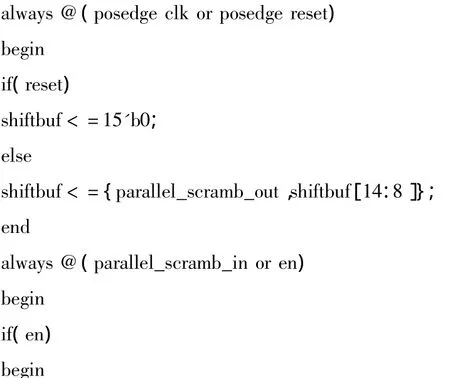

基于以上分析,以8位并行的改进扰码和解扰为例,给出电路的关键Verilog设计代码。

扰码电路的关键Verilog代码为

解码电路的关键Verilog代码为

3 仿真结果

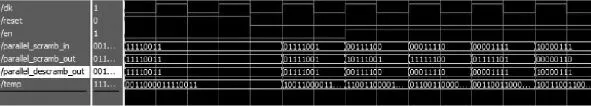

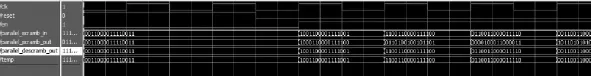

用MODELSIM软件对设计的并行扰码和解扰电路进行了功能仿真。把扰码电路和解扰电路串联起来进行了仿真,仿真结果如图4和图5所示。

图4 8位并行扰码与解扰结果(截图)

图5 16位并行扰码与解扰结果(截图)

由仿真结果看出,无论是8位并行扰码还是16位并行扰码,前两个字节都没有被扰码,当然也没有被解扰,此时扰码器的输出和解扰器的输出是相同的。从第3个字节开始,扰码器和解扰器就进行了正常的扰码与解扰。这样的输出结果正是协议的规范和要求。而解扰器的输出与扰码器的输入是完全相同的,从而证明了电路扰码和解扰功能的正确性。

用Design Compiler软件对设计进行综合,得到电路在面积、动态功耗、弛豫时间等方面的结果,如表1所示。

表1 电路综合结果

由以上综合结果可以看出,该电路功耗很低,至少可以运行于较高频率,满足协议对加扰电路的速度要求。

4 总结

根据JESD204B协议详细分析了串、并行扰码与解扰原理。针对解扰电路的输出与移位寄存器的初始状态值有关,提出了一种带使能信号的改进的扰码与解扰电路设计,并进行了Verilog实现。MODELSIM仿真和Design Compiler综合表明了电路功能的正确性,电路性能指标也达到了协议要求。本文对JESD204B协议中的扰码和解扰电路设计有一定参考作用。

[1]恩智半导体.JESD204A数据转换器接口技术分析[R].北京:NXPB.V.,2010.

[2]张立鹏,朱清新,青华平.100G以太网自同步并行扰码算法实现[J].通信技术,2010,43(5):135-137.

[3]陈序,杨龙,孟勇,等.基于SATA接口的并行扰码实现[J].电视技术,2013,37(19):71-73.

[4]JESD204B(Revision of JESD204A,April 2008),Serial interface for data converters[S].2011.

霍兴华(1991-),硕士生,主研高速SerDes接口电路设计、VLSI设计等;

姚亚峰(1970-),博士,副教授,主研通信系统设计、VLSI设计等;

贾茜茜(1991-),女,硕士生,主研数字信号处理、数字电路设计等;

陈 登(1990-),硕士生,主研高速SerDes接口电路设计等。

Im plementation of Scrambler Circuit Based on JESD204B Interface Protocol

HUO Xinghua,YAO Yafeng,JIA Xixi,CHEN Deng

(Faculty of Mechanical&Electronic Information,CUG,Wuhan 430074,China)

Data scrambling contributes to avoid spurious spectral in high-speed serial transmission.A scrambler circuit is designed and implemented in this article tomeet the JESD204B protocol.Firstly,a detailed description of the protocol requirements is given and the self-synchronizing scrambling and descrambling circuit principle is described by the example of eight parallel scrambling.At last,an improved circuit structure is proposed on the issue descrambler output relating to the initial state value and the key design code.Simulation results show that the circuit fullymeets requirements in the protocol and can be applied in high-speed interface circuit design specified in JESD204B.

JESD204B;Serdes interface;self-synchronous scrambling and descrambling;parallel scrambling and descrambling

TN919.3

A

�� 薇

2014-04-03

【本文献信息】霍兴华,姚亚峰,贾茜茜,等.JESD204B接口协议中的加扰电路设计[J].电视技术,2014,38(23).