基于DTMB中LDPC码与BCH码的乘积码构造

陈为刚,冯秀川,梁晨驰,邵亚东

(天津大学电子信息工程学院,天津300072)

衡量通信系统的指标之一是系统的可靠性,而信道编码是保证数据传输可靠性的一项标准技术。通过信道编码可降低系统的误比特率(Bit Error Rate,BER),满足一些通信系统对低BER的要求,例如数字广播中所要求的BER至少要低至10-11。

传统的高效编码技术,如Turbo码和低密度奇偶校验(Low-Density Parity-Check,LDPC)码都可获得非常低的译码门限性能,但设计的大多数高效纠错码都存在误码平层现象[1-2]。而设计基于LDPC码的高效级联码是解决纠错码误码平层问题的一个有效方法。例如,中国地面数字电视传输(DTMB)标准采用的LDPC码与BCH码的级联码使得系统 BER 低至10-12~10-11[3]。欧洲第二代卫星数字电视广播(DVB-S2)标准也采用LDPC码与BCH码的级联码作为信道编码方案[4]。由P Elias提出的乘积码[5]也是一种通过短码构造长码用以提高性能的有效方法。目前基于LDPC码的乘积码构造已取得有价值的研究成果,文献[6]中基于IEEE802.16e标准中LDPC码构造了一种低复杂度的乘积码;文献[7]针对移动数字电视提出一种基于LDPC码的乘积码。

本文基于DTMB标准中的LDPC码与BCH码构造乘积码,而且构造了不同码长的乘积码。与DTMB标准中的级联码相比,构造的乘积码也可有效降低LDPC码的误码平层,并且乘积码的编译码运算复杂度没有增加,只是延时与存储量增加。

1 DTMB中的级联码方案

LDPC码具有良好的性能,但由于误码平层问题的存在,使得LDPC码很难实现极低的误比特率。为解决LDPC码的误码平层问题,DTMB标准采用了以BCH码为外码,LDPC码为内码的级联码方案[8]。级联码中出现的错误主要由LDPC码纠正,而BCH码的作用主要是降低LDPC码的误码平层,使得DTMB系统的误码平层低于10-12。

DTMB标准中采用的BCH(762,752,t=1)码是BCH(1 023,1 013,t=1)码的缩短码。DTMB标准提供了等效码率为0.4,0.6和0.8的3种LDPC 码。3种码率的LDPC 码为 LDPC(7 493,3 048)码、LDPC(7 493,4 572)码和LDPC(7 493,6 096)码。LDPC码对应的生成矩阵中的小矩阵 Gi,j为循环矩阵,大小为b×b,0≤i≤k-1,0≤j≤c-1。3种码率的LDPC码与BCH 码级联得到的3种前向纠错码结构分别为:

1)FEC(7 488,3 008)码:首先 BCH 码进行编码,得到的4个BCH(762,752)码字作为LDPC码的信息位比特,然后LDPC码编码得到LDPC(7 493,3 048)码,再将LDPC(7 493,3 048)码前面的5个校验位删除。其中,LDPC(7 493,3 048)码的生成矩阵参数为k=24,c=35,b=127。

2)FEC(7 488,4 512)码:首先BCH码进行编码,得到的6个BCH(762,752)码字作为LDPC码的信息位比特,然后LDPC码编码得到LDPC(7 493,4 572)码,再将LDPC(7 493,4 572)码前面的5个校验位删除。其中,LDPC(7 493,4 572)码的生成矩阵参数为k=36,c=23,b=127。

3)FEC(7 488,6 016)码:首先BCH码进行编码,得到的8个BCH(762,752)码字作为LDPC码的信息位比特,然后LDPC码编码得到LDPC(7 493,6 096)码,再将LDPC(7 493,6 096)码前面的5个校验位删除。其中,LDPC(7 493,6 096)码的生成矩阵参数为k=48,c=11,b=127。

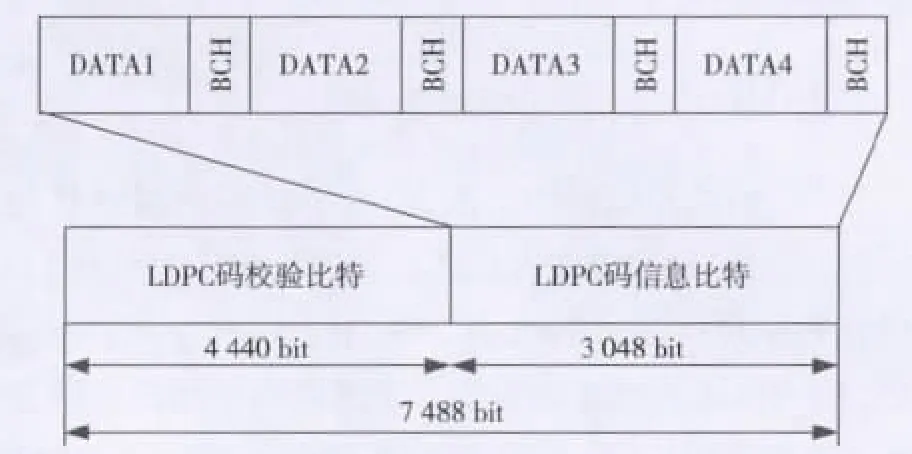

LDPC码编码器输出的码字,校验比特在前,信息比特在后。例如,等效码率为0.4的编码器输出信号中输入信息、BCH码校验比特、LDPC码校验比特的关系如图1所示。图1 中,DATA1、DATA2、DATA3、DATA4 表示每个 BCH 码字的信息比特,标志“BCH”表示BCH码的校验比特。

图1 码率为0.4的LDPC码编码器输出信号示意图

2 乘积码的构造

基于上述DTMB中的级联码方案,本文提出基于DTMB标准中LDPC码与BCH码构造更高性能的乘积码的方法。构造的乘积码中BCH(n1,k1)码和LDPC(n2,k2)码的参数为:n1=762,k1=752,n2=7 488。不同码率的LDPC码k2不同。码率为0.4的LDPC码与BCH码构造的乘积码码字结构如图2所示。由图2可得,每一行为一个LDPC码码字,除右边阴影部分外的剩余部分中每a列为一个BCH码码字,也即每个LDPC码包含的每个BCH码中的比特数目为a,a为762的因子。由此可知该乘积码中,BCH码码字数目为LDPC码的信息比特数目除以a,即k2/a,LDPC码码字的数目为缩短的BCH码码长除以a,即n1/a。若a=762,该乘积码就退化为DTMB中的级联码,成为这里提出方法的特例。表1给出3种码率的LDPC码构造的乘积码中BCH码与LDPC码的数目,在该表中a的取值分别为1、2和3。不同的a值构造的乘积码的码长不同。

图2 码率为0.4的LDPC码与BCH码构造的乘积码

表1 基于LDPC码与BCH码的乘积码的构成

以下介绍乘积码的编译码过程。乘积码编码过程:首先进行BCH码编码,一个乘积码中的所有BCH码编码完成后再进行LDPC码编码,LDPC码编码完成也即整个乘积码的编码过程结束。乘积码具体编码过程如下:

1)BCH码编码

图2所示的乘积码结构中,输入的信息比特序列(图2中无阴影部分所示)按列划分为k2/a列,每一列又包含a列且包含的比特数目为k1,每一列的k1个比特为一个BCH码码字的信息比特。k1个比特利用循环码的编码方式进行编码。由于BCH(n1,k1)码为缩短BCH码,所以在BCH码编码前需要添加261 bit的0,编码完成后将261 bit的0舍弃,不进行传输。BCH码编码完成后共有k2/a个BCH码码字。

2)LDPC码编码

BCH码编码完成后,(k2/a)×n1个比特划分为n1/a行,每一行包含k2个比特,每一行的k2个比特为一个LDPC码码字的信息比特。由于DTMB中的LDPC码为准循环LDPC码,生成矩阵为准循环矩阵,所以LDPC码的编码可采用移位寄存器编码实现[9]。根据不同LDPC码码率对应的生成矩阵完成LDPC码编码。编码完成后得到n1/a个码率为R2=k2/n2的LDPC码码字,得到的乘积码码长为(n1/a)×n2bit。

编码完成后对码字进行发送,信道模型为加性高斯白噪声信道。接收端根据信道接收值进行译码,乘积码的译码过程为:先对LDPC码进行译码,n1/a个LDPC码译码完成后,再对k2/a个BCH码进行译码。乘积码译码过程具体实现如下:

1)根据信道接收值计算出每个LDPC码码字的先验概率信息,从而实现LDPC码的迭代译码。LDPC码译码采用偏移修正最小和(Offset Min -Sum,OMS)译码算法[10],在一个乘积码中需要对n1/a个LDPC码码字进行译码。

2)n1/a个LDPC码译码完成后,BCH码采用循环码的捕错译码算法或者是Berlekamp-Massey(BM)译码算法进行译码,需要分别对k2/a个BCH码进行译码。

与级联码相比,本文构造的性能优越的乘积码的编译码复杂度并没有增加,且码长明显增大,从而性能有一定的改善。但由于码长变长,编译码过程中所需的存储量增加,延时也会增大。

3 仿真结果与分析

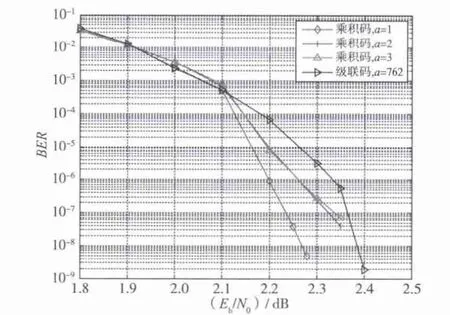

DTMB中3种码率的LDPC码与BCH码构造出3种不同的乘积码,而通过设置不同的a值可得到不同码长的乘积码。本文对3种码率和3种a值的乘积码在加性高斯白噪声(Additive White Gaussian Noise,AWGN)信道下进行仿真,调制方式为二进制相移键控(Binary Phase Shift Keying,BPSK)。将仿真得到的乘积码的性能与对应码率的级联码的性能进行对比,仿真结果如图3~图5所示。其中,BCH(1 023,1 013)码的生成多项式为g(x)=1+x3+x10,LDPC码OMS译码算法中采用的偏移量修正因子为0.6[11],LDPC 码的最大迭代译码次数为30 次。

3 LDPC码码率为0.4时对应的级联码与乘积码的性能对比

图5 LDPC码码率为0.8时对应的级联码与乘积码的性能对比

由图3中级联码与乘积码的性能对比曲线可看出,当误比特率低于5×10-4时,乘积码的性能优于级联码的性能。在误比特率为1×10-8时,a=1对应的乘积码相比于级联码有约为0.12 dB的编码增益,a=2,a=3所对应的乘积码的编码增益约为0.03 dB。由图4可得,在误比特率为1×10-7时,与级联码相比,a=1对应的乘积码的编码增益约为0.11 dB,a=2和a=3对应的乘积码的编码增益约为0.02 dB。图5中,误比特率低于1×10-3时,乘积码性能优于级联码的性能。在误比特率为1×10-7时,与级联码相比,a=1对应的乘积码的编码增益约为0.12 dB,a=2和a=3对应的乘积码的编码增益约为0.05 dB。综合图3~图5,a=1时,乘积码较级联码有一定的编码增益,不足是译码需要的存储量和译码延时增加。由于本文的性能对比采用计算机仿真,仅测试到BER为1×10-7,随着错误率的降低,乘积码的性能将进一步改善,这将在硬件平台上进行更低误比特率下的编码增益的验证。

4 小结

基于DTMB中LDPC码与BCH码,本文实现了与级联码编译码复杂度相当的乘积码的构造。仿真结果表明,与级联码相比,在误比特率为1×10-7且码率相同时,构造的不同码长的乘积码均能获得编码增益,有一定的应用价值;每个LDPC码中包含的每个BCH码的比特数目为2和3时的乘积码较级联码的增益非常有限。未来的研究中将在硬件平台上验证对比级联码与乘积码的性能。

[1] GALLAGER R G.Low -density parity- check codes[J].IRE Trans.Information Theory,1962,8(1):21-28.

[2] RICHARDSON T.Error floors of LDPC codes[C]//Proc.41st Annual Allerton Conference on Communication,Control and Computing.Monticello,USA:IEEE Press,2003:1426-1435.

[3]GB 20600—2006,数字电视地面广播传输系统帧结构、信道编码和调制[S].2006.

[4] YADAV M K,PARHIK K.Design and implementation of LDPC codes for DVB-S2[C]//Proc.39th Asilomar Conference on Signals,Systems and Computers.Pacific Grove,California,USA:IEEE Press,2005:723-728.

[5] ELIASP.Error-free coding[J].IRE Trans.Information Theory,1954,IT-4(4):29-37.

[6] CHEN W G,DONG T X.Low complexity product codes with LDPC codes achieving ultra low BER[C]//Proc.14th International Conference on Communication Technology.Chengdu,China:IEEE Press,2012:1312-1316.

[7] LIY Q,LIU B,RONGB,etal.On the performance of LDPC-RSproduct codes formobile DTV[C]//Proc.International Symposium on Broadband Multimedia and Broadcasting.Seoul,Korea:IEEE Press,2012:1-5.

[8]潘长勇,王军,宋健,等.中国地面数字电视广播传输标准概要[J].电视技术,2006,30(10):45-47.

[9] LIZW,CHEN L,ZENG L Q,et al.Efficientencoding of quasi-cyclic low-density parity-check codes[J].IEEE Trans.Communications,2006,54(1):71-81.

[10] CHEN J,FOSSORIERM PC.Density evolution for two improved BP-based decoding algorithms of LDPC codes[J].IEEE Communications Letters,2002,6(5):208-210.

[11]冯林浩.基于DTMB的纠错码译码译码器的研究与设计[D].成都:电子科技大学,2010.