TD-LTE预编码与资源映射的VLSI设计与实现*

孙 璐,张瑞齐,吴 斌

(中国科学院微电子研究所,北京 100029)

TD-LTE预编码与资源映射的VLSI设计与实现*

孙 璐,张瑞齐,吴 斌

(中国科学院微电子研究所,北京 100029)

针对双码字、双天线的TD-LTE下行链路串行结构设计了一种新型的空间复用预编码和资源映射模块。传统的空间复用预编码模块无法对串行结构中两个码字进行分时串行处理,导致在预编码之前需要添加缓存模块,增加了系统的存储器开销。通过对空间复用预编码系数矩阵进行矩阵变换,剥离出两个码字间的加法操作,从而实现对两个码字进行分时串行处理。同时,结合资源映射模块的特点,移植了空间复用预编码模块对两个码字间的加法操作,并提出了一种新的存储器复用方式,从而节省了缓存模块,将两个模块中存储器的资源开销降低 16.4%。实验结果表明,本文提出的新型空间复用预编码和资源映射模块相比于同类型设计具有控制简单、硬件资源开销小等优势。

预编码;资源映射;空间复用;TD-LTE

0 引言

相对于单码字、单天线传输,双码字、双天线的TDLTE下行链路中的 MIMO系统通过采用适当的预编码技术对两个码字的数据流进行空间复用,能够显著提高频谱利用率[1]。同时,LTE系统下行链路采用OFDM多址方式,能够在整个时域和频域上进行灵活的资源分配和调度[3]。资源映射将物理信号和预编码处理后的各个物理信道,根据规则映射在时、频域资源上,实现用户资源分配的灵活性和高效性[3]。

双码字、双天线的TD-LTE下行链路串行实现结构需对两个码字进行分时串行处理,而传统的空间复用预编码模块无法实现两个码字的串行分时处理,导致在预编码之前需要添加缓存模块,增加了系统的存储器开销。

本文针对双码字、双天线的TD-LTE下行链路串行实现结构设计了一种新型的空间复用预编码和资源映射模块。本设计解决了传统的预编码模块无法对两个码字进行分时处理的问题,同时改进资源映射模块并对其存储器进行复用,节省了传统实现结构中的额外缓存,降低了系统的存储器开销。

1 预编码和资源映射

1.1 空间复用预编码算法

空间复用预编码分为开环空间复用和闭环空间复用[4-6]。

1.1.1 闭环空间复用

闭环空间复用在发射端利用反馈的信道状态信息,然后根据一定的最优化准则对传输信息进行预编码[8]。对于无循环延迟情况,双码字、双天线的闭环空间复用预编码定义为:

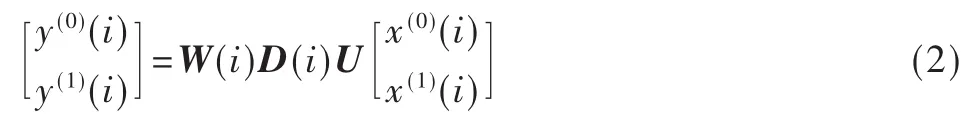

其中,y(0)(i)和 y(1)(i)表示预编码处理后天线端口 0和 1上的数据,x(0)(i)和 x(1)(i)表示层映射输出的层 0和1上的数据。预编码矩阵W(i)的大小为2×2,i=0,1,…,为天线端口上数据的个数,为层数据的个数。在双天线模式下,eNodeB根据反馈回得预编码矩阵指示从参考文献[4]中选择中选取W(i)。

1.1.2 开环空间复用

如果发射端不需要信道反馈的信道状态信息,这种空间复用称为开环空间复用。对于长延时的循环延迟分集的情况,双码字、双天线的开环空间复用预编码被定义为:

其中,W(i)是预编码矩阵,大小为 2×2,i=0,1,…,。D(i)表示循环延迟分集,为 2×2的对角阵,U的大小也是2×2。D(i)和U从参考文献[4]表6.3.4.2.2-1中选择。在双天线模式下,开环空间复用只能从参考文献[4]表6.3.4.2.3-1中选择索引为0的W(i)。1.2资源映射

TD-LTE下行链路基于OFDM技术,其帧结构是一个时、频二维资源格。该时、频二维资源格的定义可参照参考文献[4]。

资源映射将物理信号和预编码输出的不同天线端口上的物理信道按照各自的规则及时有效地映射在上述时、频二维资源格上[4]。各个物理信道和物理信号的映射地址算法见参考文献[4]。

2 预编码与资源映射的设计与实现

2.1 TD-LTE下行链路串行结构

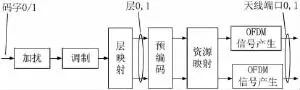

双码字、双天线的TD-LTE下行链路的串行结构如图1所示。

图1 TD-LTE下行链路串行结构

码字0和码字1依次分时经过加扰和调制模块,生成调制符号,层映射模块分别将码字0和码字1的调制符号映射到层0和层1上,预编码模块选用合适的空间复用方式将层0和层1的数据变换到天线端口0和天线端口1上,接下来资源映射模块将不同天线端口上的数据根据规则映射在OFDM时、频资源块上,最后形成OFDM信号输出。

2.2 预编码的实现

对于双码字、双天线的情况,统一式(1)和式(2),空间复用预编码算法可以表示如下:

其中,N为2×2的矩阵,当表示开环空间复用时,N=W(i)D(i)U;当表示闭环空间复用时,N=W(i)。

对于双码字、双天线的情况,经过层映射处理后的数据与码字对应的关系为:

将式(4)、式(5)带入式(3)可得:

从式(7)可以看出,天线端口 0上的数据 y(0)需要同时得到码字 0的数据 d(0)和码字 1的数据 d(1),进行系数相乘后做加法操作;同理,天线端口 1上的数据 y(1)也一样。

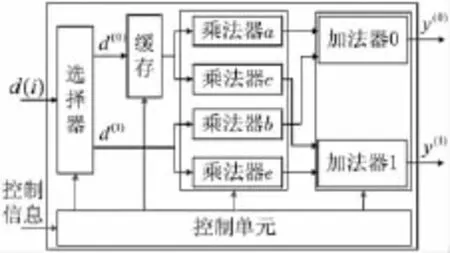

根据式(7),可以设计出传统的空间复用预编码模块实现结构框图,如图2所示。传统的预编码模块将经过调制之后串行而来的码字 d(i)通过选择器进行分配,如果是码字0,则将其存入缓存中;如果是码字 1,则直接将其送入乘法器与系数b和e相乘,同时将缓存中的码字0取出送入乘法器与系数a和c相乘。最后将结果按照式(7)所示分别送入加法器0和 1进行加法操作,最终输出得到天线端口0和1上的数据。其中控制单元作为主控制器,控制各个模块的工作方式。

图2 传统预编码模块实现结构框图

但是,传统的空间复用预编码模块并不能对码字0和码字1进行分时处理,2.1节中串行结构的预编码模块需要增加缓存用以存储先期到达的码字0。在TDLTE下行链路中,经过调制之后的单个码字包含的最大数据量可以达到 1 200×12个调制符号[4],本设计中采用调制符号位宽为 16位,数据为 I/Q两路,因此预编码模块中增加的缓存大小为 2×1 200×12×16=0.460 8 Mb,显著增加了该模块的存储器开销。

为了解决额外存储器开销的问题,对空间复用预编码算法进行改进。将式(7)进行矩阵变换得到:

通过变换后,预编码将码字0与码字1的处理分开,剥离出两者的加法操作,这样便不需要两个码字的数据同时到达,可以实现对两个码字的分时串行处理。令:

将式(7)~式(10)代入式(6)得到:

根据式(8)~式(13)并剥离加法操作,可以设计出改进后的新型空间复用预编码模块,其实现结构框图如图3所示。

图3 新型预编码模块实现结构框图

相对于传统预编码模块,改进后的新型预编码模块去掉了缓存单元和最终的加法器。串行而来的码字0、码字1经过选择器分别乘以系数a、c和b、e,得到天线端口0和1上的中间变量和,然后再经过选择器输出。码字间的加法操作将会被移植在随后的资源映射模块进行。

2.3 资源映射的实现

根据资源映射的算法,可以设计出传统的资源映射模块的实现结构框图,如图4所示。

资源映射模块用一块存储器作为OFDM时、频资源的实体,其包含四块同等大小的缓存0-4,每两块对应一个天线端口的时、频资源格,在写入、读取时做乒乓操作以让帧数据流水处理[9]。控制单元按照各个物理信道和信号的映射地址算法在写地址生成模块生成相应写地址,将天线端口0和1的数据写入对应缓存中,完成资源映射,最后控制单元按要求控制读地址生成模块生成读地址,将缓存中两个天线端口上的数据读出并输出。

传统的资源映射模块并不能进行分时串行处理,但是注意到其特有的存储器资源可以作为分时串行处理两个码字所需的缓存。因此,根据新型空间复用预编码模块的工作特性,通过复用资源映射模块的存储器资源,设计了改进后的新型资源映射模块,其实现结构框图如图5所示。

图4 传统资源映射模块实现结构框图

图5 新型资源映射模块实现结构框图

新型资源映射模块增加了加法模块,其输入是新型空间复用预编码模块输出的天线端口0和1上的中间变量。当中间变量是由码字0产生时,将其直接写入对应天线的缓存;当中间变量为码字1时,将缓存中码字0的中间变量取出,与码字1的中间变量对应相加,此时的相加结果即为预编码的完整输出,完成预编码的操作,最后将此结果写入对应缓存,完成资源映射操作。这样,新型预编码模块不仅实现了对两个码字的分时串行处理,同时节省了传统预编码模块的额外存储器开销。

3 仿真与验证

3.1 仿真结果

本设计采用基于Altera StratixIV系列的 EP4SGX530-KH40C3 FPGA芯片平台进行综合。系统采用的工作时钟频率为122.88 MHz,调制符号位宽为 16位,分别对传统和新型的空间复用预编码、资源映射模块进行综合并将其资源开销进行比较,结果如表1所示。

从表中可以看出,改进后的新型实现结构相较传统实现结构在组合逻辑和寄存器逻辑开销上有略微减小,而存储器开销显著降低了16.4%。

表1 改进前、后串行结构资源开销比较

3.2 系统验证

本设计中的新型空间复用预编码模块和资源映射模块已应用到图1所示的双码字、双天线的TD-LTE下行链路的VLSI系统架构中。

为验证设计的功能与性能,搭建了如图6的硬件验证平台,采用了 Altera公司 Stratix IV系列的 FPGA芯片EP4SGX230KF40C3,同时为TD-LTE下行链路设计了基于AD9361芯片的射频系统,并设计了整体系统的测试软件,通过 TD-LTE协议框架下多种业务层面的系统级测试项,完成了对该TD-LTE下行链路系统的功能和性能的验证,系统指标完全满足协议 36.141的测试指标要求。

图6 硬件验证平台

4 结束语

本文针对双码字、双天线的TD-LTE下行链路串行结构设计了一种新型空间复用预编码和资源映射模块。该设计解决了传统实现结构无法对两个码字进行分时串行处理的问题,同时节省了实现中的额外缓存,将模块中存储器开销降低16.4%。

[1]张振东.MIMO-OFDM基带收发机关键模块研究与VLSI实现[D].北京:中国科学院大学,2012.

[2]ABBAS S S A,SHEEBA P A J,THIRUVENGADAM S J. Design of downlink PDSCH architecture for LTE using FPGA[C].IEEE-International Conference on Recent Trends in Information Technology,2011:947-952.

[3]张乐,张玉艳.基于通用处理器的 TD-LTE资源映射的设计与实现[J].软件,2011,32(10).

[4]3GPP TS 36.211,Evolved Universal Terrestrial Radio Access(E-URRA):Physical channels and modulation[S].2009.

[5]3GPP TS 36.212,Evolved Universal Terrestrial Radio Access(E-URRA):Multiplexing and channel coding[S].2009.

[6]3GPP TS 36.213,Evolved Universal Terrestrial Radio Access(E-URRA):Physical layer procedures[S].2009.

[7]朱瑞茂.TD-LTE下行链路预编码技术研究[D].北京:北京邮电大学,2010.

[8]王映民,孙韶辉等.TD-LTE技术原理与系统设计[M].北京:人民邮电出版社,2010.

[9]钱黄生,夏忠玲.基于 FPGA双 RAM乒乓操作的数据存储系统的研究[J].科技信息,2010(21).

VLSI design and implementation of pre-coding and resource mapping for TD-LTE system

Sun Lu,Zhang Ruiqi,Wu Bin

(Institute of Microelectronics of Chinese Academy of Science,Beijing 100029,China)

In this paper,a novel spatial multiplexing pre-coding and resource mapping module is designed for serial implementation architecture of downlink TD-LTE system with double code words and dual-antenna.The traditional spatial multiplexing pre-coding module can't process two code words in different time serially.Therefore,a buffer is needed before pre-coding processing,which leads to extra memory overhead of the system.By transferring the coefficient matrix of the spatial multiplexing pre-coding,the addition operation of two code words is removed in order to make the pre-coding module capable to process two code words in different time serially.Besides,according to the features of resource mapping module,the addition operation of two code words is transplanted from the spatial multiplexing pre-coding module and a new way to multiplexing memory is put forward,which can save the buffer mentioned before and reduce the memory overhead in the two modules by 16.4%.The experimental results show that,compared to the same type of design,the novel spatial multiplexing pre-coding and resource mapping module in this paper have the advantages of simple control and low hardware cost.

pre-coding;resource mapping;spatial multiplexing;TD-LTE

TP492

A

10.16157/j.issn.0258-7998.2015.11.017

孙璐,张瑞齐,吴斌.TD-LTE预编码与资源映射的VLSI设计与实现[J].电子技术应用,2015,41(11):61-64.

英文引用格式:Sun Lu,Zhang Ruiqi,Wu Bin.VLSI design and implementation of pre-coding and resource mapping for TD-LTE system[J].Application of Electronic Technique,2015,41(11):61-64.

2015-05-08)

孙璐(1989-),男,硕士研究生,主要研究方向:宽带通信基带算法研究与实现。

国家科技重大专项(Y4GZ342001)

张瑞齐(1979-),男,高级工程师,主要研究方向:移动通信算法研究和设计,实时信号处理VLSI体系架构。

吴斌(1976-),博士,研究员,主要研究方向:宽带通信SoC体系架构,实时信号处理 VLSI体系架构。