捷变频频率合成器的研究和设计

贵州航天计量测试技术研究所 刘 兴 杜 勇

0 引言

捷变频率源在雷达、通信、电子对抗等领域中的应用十分广泛,是决定电子系统性能的关键设备。随着现代军事、国防及无线通信事业的不断发展,电子系统对频率合成器的换频时间、杂散、相位噪声等指标提出了越来越高的要求。

传统的间接频率合成技术通常由锁相环电路实现,由于锁相环中的锁相反馈环路固有的延时特性使其频率变换时间较慢,无法满足快捷变的要求;而直接频率合成技术虽然输出信号相噪好、变频速度快,但是此类频率源的体积大、功耗高,且成本难以控制[1]。

本文采用直接数字频率合成(DDS)与直接频率合成相结合的方案来实现捷变频频率合成器。即采用DDS输出的中频信号和步进为50MHz的4个点频本振信号分别进行下混频,并通过小型化滤波器开关组件滤除杂散。该频率源的分辨率为1kHz、频率带宽200MHz、相位噪声优于-120dBc/Hz@10KHz、跳频时间不超过1μs,满足频率捷变的要求,并且该频率合成器较传统的频率合成器明显的优势就是体积小,便于工程应用。

1 捷变频频率合成器设计方案

1.1 设计指标要求

本设计的具体设计指标如下所示:

a)跳频时间:<1μs;

b)频率分辨率:1kHz;

c)频率范围:600MHz~800MHz;

d)相位噪声:≤-120dBc/Hz@10KHz;

e)杂散抑制:≤-60dBc。

1.2 频率捷变方案

捷变频频率合成器的原理图如图1所示。

图1 捷变频率合成器的原理图

本设计采用FPGA作为整个系统的CPU,控制DDS工作在并行数据端口调制模式下,产生带宽为50MHz的中频信号,DDS产生的信号与不同的本振信号进行下混频。在混频器输出端,FPGA控制微波开关选择不同的输出通道,将输出信号带宽扩展为600MHz~800MHz,从而实现频率范围指标要求。

本设计中的本振信号采用直接频率合成方式实现,并通过微波开关进行频率切换。其相位噪声优于-132dBc/Hz@10kHz。

2 关键指标分析

2.1 跳频时间的分析

本文采用直接数字频率合成(DDS)与直接频率合成相结合的方案来设计捷变频率合成器。本文选用的DDS为AD9910,该芯片支持高达1GHz的采样速率,内置14位DAC,能够产生频率高达400MHz的正弦波信号,频率分辨率可达0.23Hz。该芯片在并行数据端口调制模式下,频率控制字输入DDS至其DAC输出需要的时间为103个参考时钟周期[2]。本设计的DDS芯片的参考时钟周期为1GHz。理论上,DDS接收到频率控制字到DDS芯片输出信号的时间为103ns。

由图1可知,捷变频频率合成器频率切换的时间还与微波开关切换时间和滤波器的延时有关,微波开关由FPGA并行控制的,本设计选用的微波开关切换时间约为150ns,滤波器延时约300ns。由于微波开关和滤波器并行工作,因此频率切换时间取决于滤波器的延时,理论上,频率合成器的跳频时间为DDS芯片输出信号所需时间与滤波器延时之和,即403ns。

通过上述分析,频率合成器的频率切换时间满足技术指标要求。

2.2 杂散抑制分析

由DDS工作原理可知,当参考时钟为1GHz时,AD9910的输出带宽可达400MHz。理论上,单片DDS就可以实现带宽400MHz的频率跳变,但在实际当中,DDS存在大量的杂散信号分量,这些杂散信号主要有3个来源,一是波形存储器ROM的量化误差;二是相位截断误差;三是DAC的非理想特性。这些误差在DDS中是无法避免的,因此杂散也是时刻伴随主信号的产生而存在的[3]。

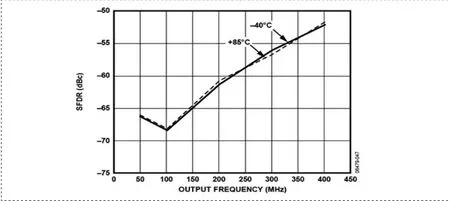

AD9910的宽带不失真动态范围(SFDR)如图2所示。

图2 AD9910宽带SFDR与输出频率和温度的关系

由图2可知,在温度恒定的情况下,AD9910的宽带不失真动态范围(SFDR)在输出频率在50MHz~100MHz范围内呈递减趋势,输出频率在100MHz~450MHz范围内,宽带SFDR随输出频率的增高呈不断恶化的趋势[4],在0~230MHz范围内AD9910的宽带SFDR<-60dB,满足指标要求,若选择0~230MHz带宽作为输出信号,其二次谐波为0MHz~460MHz,二次谐波和主信号在信号带内产生混叠,并且会有交调产物出现,无法将二次谐波滤除。本设计选择100MHz~150MHz作为AD9910的输出频段,并使用带通滤波器将其谐波滤除。

DDS产生的信号频率范围为100MHz~150MHz,为了防止谐波和混频产生的高阶交调信号(主要是三阶交调信号)落入带通滤波器的通带内,本设计选取了频率为750MHz~900MHz,步进为50MHz的4个点频本振与AD9910产生的信号进行下混频,产生频率范围为600MHz~800MHz的信号。对应不同的混频本振,选取合适的带通滤波器可以滤掉谐波和三阶混频产物,如表1所示。

表1 不同本振下的滤波器带宽与三阶混频产物带宽

3 软件设计

本文的软件设计流程图如图3所示。

图3 捷变频率合成器的软件流程图

由图3可知,本设计中FPGA先通过单频调制模式产生变频的底限频率,再通并行数据端口调制模式更新DDS的频率控制字,完成在设定频率范围内的捷变。

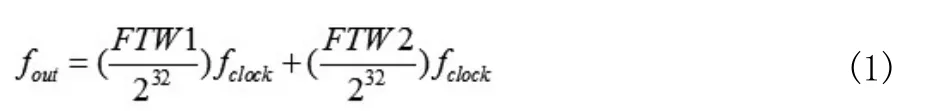

故DDS的输出频率可用式(1)表示:

式中:fclock为AD9910的输入时钟,FTW1为串口输入的32位频率控制字,FTW2为并口输入的16位捷变频率控制字[5]。DDS在进行频率捷变时,FTW1为一定值,控制频率跳变的底限频率,FTW2为作为频率捷变控制字,通过FM增益字即FTW2与FTW1的对齐方式来控制频率跳变的范围[6]。

本设计中DDS的输入时钟信号为1GHz,考虑到动态不失真范围(SFDR)的影响和频率分辨率的要求,设置FM为1100,即式(1)中FTW2的最低位与FTW1的第12位对齐,经计算其频率分辨率为(212/232)×109Hz=953.7Hz,故其频率分辨率为1kHz、频率允许误差为±477Hz,满足设计指标要求。

经3.2中分析,本文选择DDS的捷变频段为100MHz~150MHz,即DDS输出信号的跳变频率底限为100MHz,变频带宽为50MHz,故本文设置FTW1为0x19999999,经以上设置,DDS的输出频率跳变范围100MHz~162.5MHz,但本设计只需要50MHz带宽的DDS输出信号即100MHz~150MHz,其二次谐波200~300MHz与主频未发生混叠,可用带通滤波器滤除。

4 试验验证

捷变频率跳变时间测试如图4所示。

图4 系统测试图

4.1 输出信号跳频时间测试

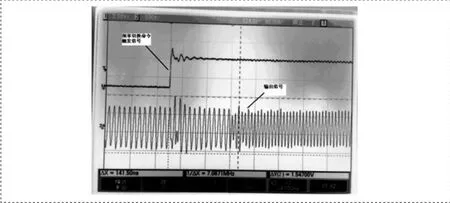

捷变频率跳变时间测试如图5所示。

图5 输出信号调频时间测试

图5 中标识1为频率切换命令触发信号,标识2为输出信号,图中可以看出,切换频率在同一滤波器带宽内(几组高速微波开关未动作),频率切换触发信号到输出信号从一个频率切换到另一频率需要的时间t 1为142ns左右,满足频率跳变时间小于500ns的指标要求。

由3.1节的分析可知,捷变频率在整个带宽200MHz内跳变,其跳变时间还要加上滤波器的延时时间t 2,约为300ns,在这种情况下的频率切换时间为t 1与t2的和(449ns),满足频率跳变时间小于1μs的指标要求。

4.2 相位噪声测试

在8个滤波器通带内任取一个点作为测试点,其相位噪声测试数据如表2所示。

表2 捷变频频率合成器相噪测试

4.3 杂散抑制测试

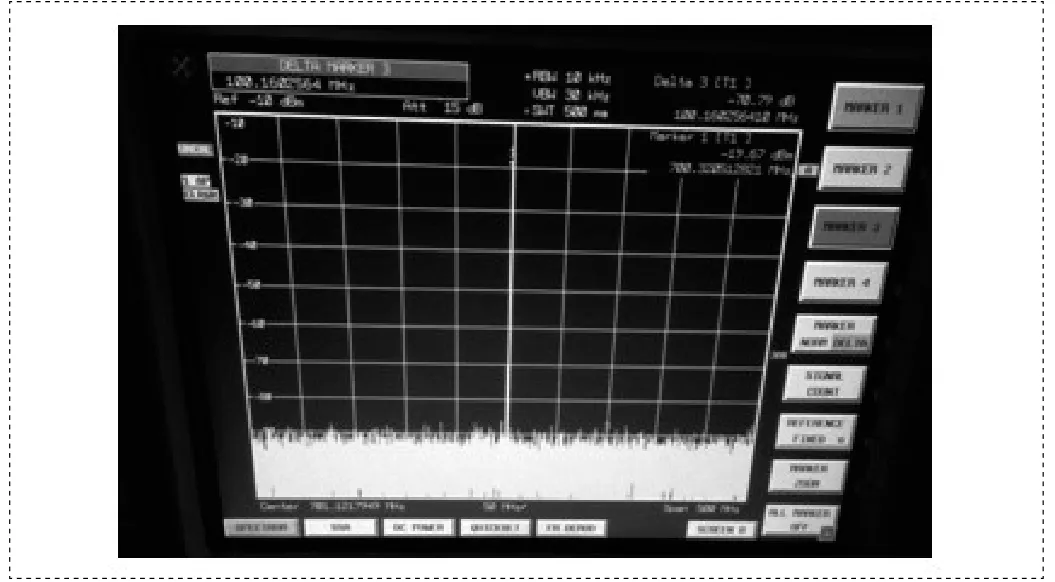

取700MHz输出信号的杂散测试如图6所示。

图6 700MHz信号杂散测试

图6 中可以看出,信号频率为700MHz,宽带杂散优于-70dBc,满足设计指标要求。

5 结论

本文设计了一种采用FPGA作为系统CPU,利用DDS并行数据端口调制模式实现系统输出频率的捷变,时序控制简单,可以将频率跳变时间控制在1μs内,跳变速度远高于利用DDS单频调制模式实现跳变的速度。本设计还通过对DDS宽带SFDR的分析,考虑到混频受谐波和混频产物的影响,利用DDS信号和50MHz步进本振混频的方法,将捷变频段扩展到了200MHz,经实际测试,方案达到了指标要求,有较好的工程实践价值。

[1]刘林,田进军.基于DDS和直接频率合成技术的超宽带捷变频率源设计与实现[J].兵工学报,2010.

[2]直接数字频率合成器AD9910芯片资料.

[3]陈科,叶建芳,马三涵.基于DDS+PLL频率合成器的设计与实现[J].电子测量技术,2009.

[4]徐晓东,王西峰.基于高速DDS芯片的宽带低杂散信号产生器的实际与实现[J].雷达与对抗,2008.

[5]夏允祥,郭德淳,余军.基于AD9858的快速捷变频频率合成器的设计[J].现代雷达,2005.

[6]段疑康.基于FPGA的伪随机序列发生器设计[M].电子元器件引用,2010.