基于FPGA和CY7C68013A的数据采集系统

陶庭兴

摘 要:为了解决计算机和基于FPGA的数据采集系统的数据传输速率的问题,本文设计一种基于CY7C68013A芯片的USB2.0接口方案,设计采用FPGA为主控芯片,实现对USB芯片的控制。介绍了该系统的硬件设计以及软件工作流程。实验表明:FPGA通过USB接口实现了高速可靠的数据传输。

关键词:FPGA;USB2.0;CY7C68013A;数据传输

由于USB接口的高速、即插即用,易于扩展等特点其得到广泛应用。USB2.0高速模式下,数据传输速率可达480Mbps[1-2],是目前电脑中的标准扩展接口。本系统设计的目的在于基于FPGA控制多路数据采集系统和计算机之间提供一个高速通信接口。

1 系统硬件设计

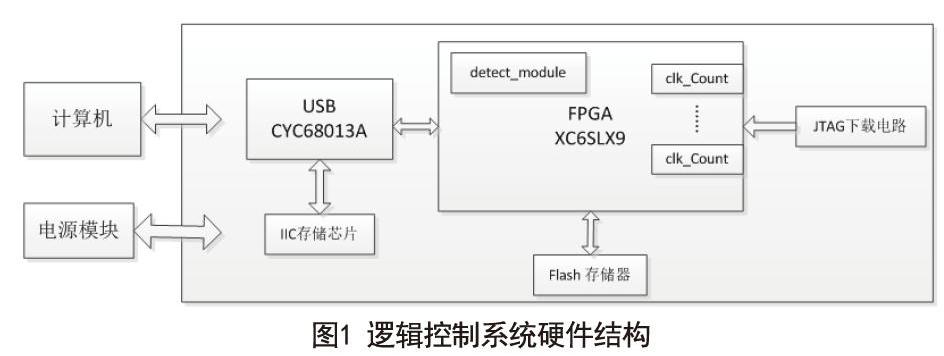

1.1 逻辑控制系统硬件结构

逻辑控制系统的硬件结构如图1所示,其中电源模块负责电压的转换以及给整个系统各部分供电。FPGA控制模块包括FPGA最小系统板构成的主控板控制的多达10路的数据采集系统。控制系统完成多路高速数据采集、数据处理、数据通信等功能。其中detec_module 用来读取DMD输出的同步信号,clk_Count 读取探测器的电脉冲信号。其外围设备有程序烧写电路的设计,储存程序的外部Flash芯片的电路设计以及逻辑电平的输出以及逻辑电平的检测。

USB控制器用来实现FPGA和计算机之间的高速数据传输。USB接收到计算机发送的指令后,执行相应的操作[3],并将采集到的数据通过USB上传到上位机进行存储。其中IIC存储芯片用来存储程序,避免因掉电而丢失。

1.2 FPGA和USB控制器

本系统所使用的FPGA芯片是Xilinx公司的Spartan6系列的FPGA,型号为XC6SLX9[4-5]。XC6SLX9具有2个时钟单元,多达9152个逻辑单元,可配置逻辑块90Kb,具有576Kb块存储RAM,能够满足本系统的要求。

USB控制器则使用的是Cypress公司的EZ-USB FX2LP系列的CYC68013A。CY7C68013A 是一款集成增强型的 8051 内核、USB 2.0 收发器和 SIE(智能串行接口引擎)的芯片。通用可编程接口GPIF和Slave FIFO是CY7C68013A与外设的两种接口方式,本系统采用得是Slave FIFO模式[6]。外部逻辑在Slave FIFO模式下可以对CY7C68013A内部多个缓冲区进行读操作或写操作而不需要CY7C68013A 的CPU干预,因而可以达到很高的传输速率。

2 系统软件设计

2.1 CYC68013A固件设计

固件是固化在USB接口芯片里面的一段程序,其作用是控制硬件来完成预期的设备功能。Cypress公司为用户提供了一套功能十分强大的开发包,整个固件的编译和调试都是在Keil uVision4环境中进行的[7-10]。

其中固件里TD_Init()主要完成对CY7C68013A的初始化,USB启动以后会调用一次。程序里对TD_Init()函数中相关寄存器进行配置,使其工作与同步Slave FIFO模式下即可。此时时钟仍然由USB外部晶振提供,上电后系统还需要进行状态切换才能使之工作在外部时钟模式下,具体操作在TD_Poll()函数中完成。程序编写完成后,对工程进行编译链接,最终生成对应的.IIC文件,通过官方固件开发软件下载到CY7C68013A芯片的外部IIC存储芯片。

2.2 Verilog 程序设计

该FPGA系统包含两个功能性的子模块,如下图所示:

DMD每输出一个上升沿,TTL_P 电平拉高一个时钟周期,然后拉低。Start_Countx 为模块启动信号。当 Start_Countx 为 1 时。探测器每来一个脉冲,Countx_Data 加 1;当 Start_Countx 为 0 时,Countx_Data 为 始终为0。

上电之后系统处于接收指令的状态,当USB接收到相应的指令并且FPGA读取完毕之后,

当检测到TTL_P的高电平,读取Countx_Data的值先存入缓冲区当中,等待发送。随后拉低 Start_Countx,清空 Countx_Data。接着拉高 Start_Countx,重新计数。接着开始发送缓冲区中的数据,发送完毕之后,再次处于检测TTL_P的电平。

USB时钟由FPGA提供,FPGA的50MHz时钟分频而出的25MHz的时钟。在slave FIFO模式下,每2个时钟周期即可完成一个字节数据的写入。USB接收的数据格式为Cx(2)+标号(4)+脉冲个数(4)(括号里为字节数),其中标号在TTL_P为高电平时会自动加 1。每个clk_Count模块上传的数据总个数为10个字节,USB可以传输在DMD脉冲信号的最短周期内(100us)传输2500 Bytes的数据,理论上可以外接250路clk_Count模块,考虑到模块之间的延迟、FPGA外部引脚数的限制以及实际项目中的需求,本系统只做10路即可。

3 结束语

本系统最终实现了通过FPGA和USB 2.0接口芯片CY7C68013A来完成脉冲个数的采集以及传输,实现了预期的目标。实际测试表明,本系统的通信接口最高速率达到了100Mbps,并且数据高速稳定可靠。不足之处在于CY7C68013A 的同步Slave FIFO 模式下进行数据传输,一共有 16 根数据总线,所以USB的通信速率可进一步提高。

参考文献

[1]关云飞. 基于FPGA的差动像散离焦信号的检测和处理技术[D].哈尔滨工程大学,2012.

[2]关珊珊. 基于FPGA的图像显示技术研究[D].南京航空航天大学,2012.

[3]温新民. 基于ARM的伺服控制器在竹节纱装置中的应用研究[D].上海交通大学,2010.

[4]张丹红,潘锋. 基于USB2.0总线的高速数据采集系统设计[J]. 传感器世界,2009,04:42-45.

[5]鲁林,刘文怡,王浩. 基于FPGA的微型数字存储系统设计[J]. 电子设计工程,2009,09:1-2+5.

[6]罗进. FPGA在高速多通道光纤光栅解调仪表中的应用[D].武汉邮电科学研究院,2012.

[8]罗向东. 基于FPGA与CY7C68013A的USB接口系统设计[J]. 科技广场,2010,06:96-98.

[9]张聪,张涛. 基于USB3.0设备控制器的固件设计[J]. 电子器件,2013,03:383-388.

[10]张惠民. 基于GY7C68013A芯片的数据采集装置研究[D].太原科技大学,2008.

[11]韦伟. 基于USB2.0的CCD相机系统的设计与实现[D].南京理工大学,2009.

[12]周玉龙. 基于FPGA的高速数据传输及存储系统设计与实现[D].电子科技大学,2010.