焊料层空洞对IGBT芯片温度分布影响分析

夏燕飞,罗毅飞,汪 波,刘宾礼

(海军工程大学 舰船综合电力技术国防科技重点实验室,武汉430033)

焊料层空洞对IGBT芯片温度分布影响分析

夏燕飞,罗毅飞,汪波,刘宾礼

(海军工程大学 舰船综合电力技术国防科技重点实验室,武汉430033)

基于IGBT七层结构,建立三维有限元模型,模拟研究焊料层空洞对芯片温度场的影响,讨论空洞对芯片结温作用机理。研究表明:焊料层空洞改变芯片散热途径,影响芯片温度分布;单个空洞越大,芯片结温越高,在中心和外边缘位置结温升高更加显著;对于多个空洞,分布越密集,结温越高。

有限元模型焊料层空洞温度分布

0 引言

IGBT具有双极型功率晶体管高耐压、导通压降低和功率MOSFET的开关速度快的特点,适用于中、大功率应用场合。随着IGBT器件电压等级的提高和芯片封装密度的提高,器件芯片工作温度升高,造成器件失效率的升高,可靠性降低。有研究表明,器件的工作温度每升高10℃,寿命降低一半[1]。在器件生产过程中,由于工艺原因,会在芯片焊料层形成空洞,而芯片焊料层处于导电、散热的主要通路上,空洞的出现会增加器件的热阻,改变芯片的温度分布,造成芯片局部热量过度集中,严重时会形成热斑[2],甚至导致器件烧毁。

已有文献大多采用模拟仿真的方法研究空洞对IGBT热特性的影响:童蕾、张建、吴煜东等[2-10]采用有限元法分析空洞对功率器件温度、应力的影响,建立不同的模型,研究内容和侧重点各有不同;D.C.Katsis、Otiaba[11-12]等人对空洞与热阻之间的关系进行了研究,得到一些定性的结论;但对于焊料层外边缘空洞和空洞分布的研究较少。文中基于具体IGBT结构,建立了三维有限元热仿真模型,研究单个空洞的大小、位置和空洞分布对芯片结温的影响,并着重讨论外边缘空洞和空洞分布对芯片温度分布的影响。

1 IGBT传热模型描述及相关参数

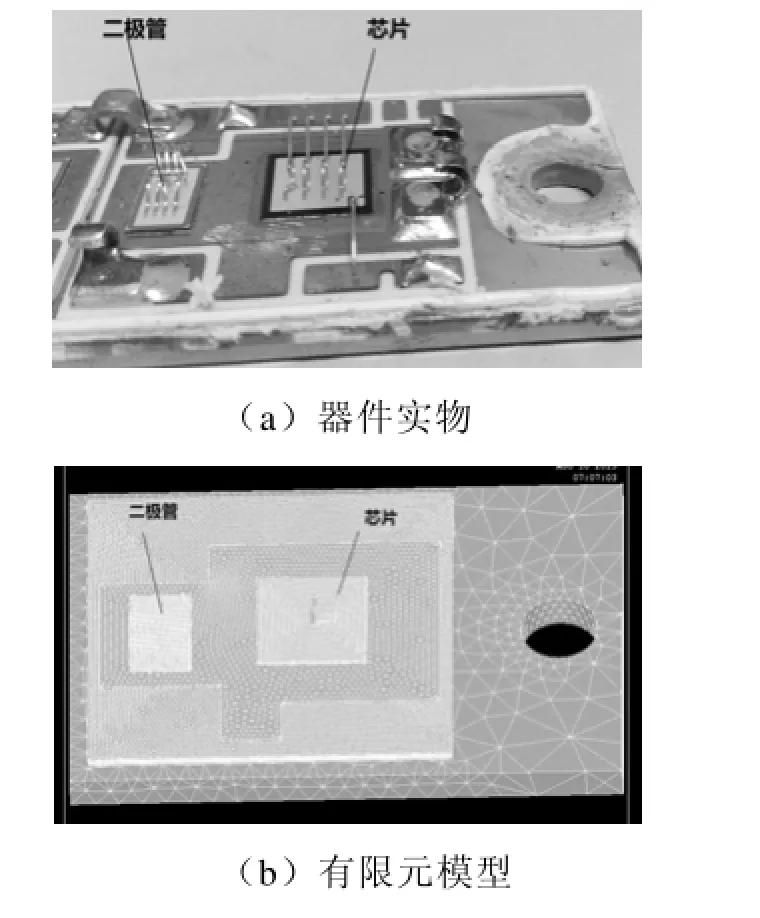

IGBT器件除去塑料外壳封装及硅胶,一般有图1所示的七层结构,从上到下依次为芯片(二极管)、芯片焊料层、DBC上铜板、DBC陶瓷层、DBC下铜板、衬底焊料层和基板,芯片、二极管焊接在DBC上铜板上,通过铝线键合工艺实现电气连接。

图1 IGBT七层封装结构示意图

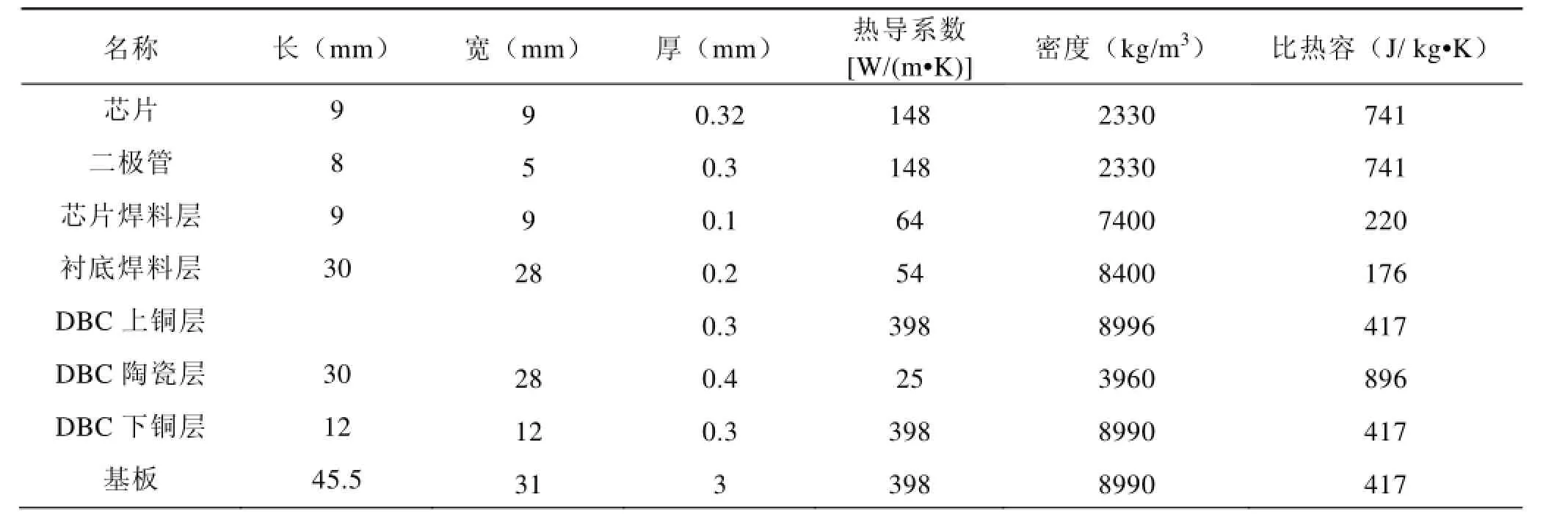

文中以某1200 V/50 A半桥IGBT模块为例,构建七层有限元热仿真模型,如图 2所示。模型中IGBT芯片设为主要热源,尺寸为9 mm×9 mm,对称的位于器件 DBC上铜板两端,考虑到尖峰和可靠性等问题,器件使用中一般留有一定余量,仿真中功率损耗(Ploss)设定为75 W。由于半桥结构有两个对称的芯片和二极管,为研究单一芯片受空洞的影响,选取模块的1/2进行建模,忽略铝线和其他接线端子,各层材料的几何尺寸及材料物理属性如表 1,其中上铜层不规则,没有给出具体的长、宽尺寸,以实际模块的封装形状和尺寸为准。

采用 ANSYS软件计算稳态热传导问题,对模型仿真条件进行如下设定:

1)芯片均匀产热,芯片体积产热率(Hgen)为2.9×109W/m3,如公式(1):

其中:Vchip为芯片体积;热量通过七层结构逐层传递,实际器件芯片上表面涂有硅胶,忽略芯片热对流,另外芯片热辐射的能量较少,也进行忽略[13]。

2)整个模块安装在水冷散热器上,接触良好,对基板面均匀散热,对流散热系数为2000 W/(m2·K)(搭建试验平台,导通功耗设为75 W,测量芯片最高结温和基板温度,利用试验数据结合仿真估算基板面对流散热系数),环境温度 25℃,基板三个侧面与空气自然对流散热,对流散热系数为 10 W/(m2·K)。

表1 IGBT模型材料参数

2 有限元分析

2.1空洞选取

将空洞引入模型前,需要选取合适的空洞形式。在垂直芯片方向,空洞有贯穿型、非贯穿性,而贯穿型空洞对器件结温影响稍大[5],也便于建模;在水平方向,焊料层中的空洞多为圆形和椭圆形[13],综合考虑选取贯穿型圆柱空洞。七层结构中有两层焊料,分别为芯片焊料层和衬底焊料层。衬底焊料层离芯片较远,中间隔着 DBC板。传热滞后,另外,相比芯片焊料层尺寸大,空洞尺寸相同时,对芯片结温影响较小。处于芯片正下方的芯片焊料层,对芯片的温度分布影响更直接、明显,故选取芯片焊料层为研究对象。

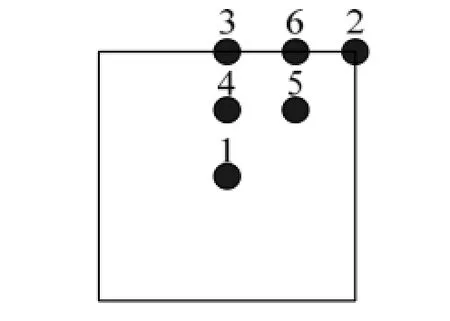

用空洞率和圆柱半径衡量空洞的尺寸,美军标MIL-STD-883H方法2030中对空洞率定义为:空洞率=空洞总体面积/焊料层总面积。为研究方便,在芯片焊料层上选取6个典型位置,进行编号,如图3所示所示:位置1、4、5位于芯焊料层内部,位置2、3、6位于焊料层外边缘。

2.2无空洞的模型

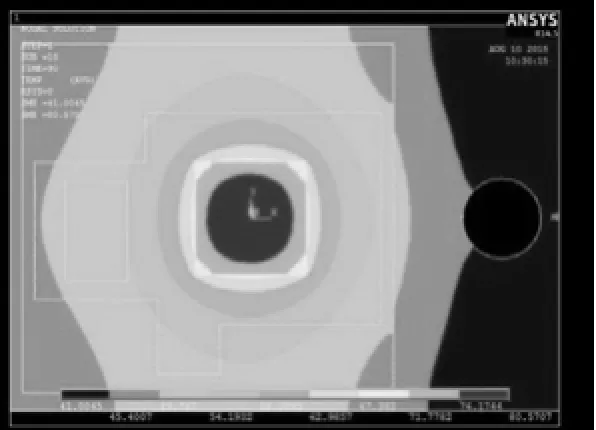

图4为无空洞时芯片温度分布,芯片中心温度最高,为80.6℃,远离中心温度逐渐降低,芯片表面等温线呈圆形规则分布,在垂直方向,由芯片到基板温度逐渐降低。

图2 IGBT器件的实物与有限元模型

图3 芯片焊料层空洞典型位置

图4 无空洞时芯片温度分布

2.3单个空洞大小对芯片最高结温影响

在如图3所示典型位置1、2、3处,分别引入不同半径的空洞并建模,仿真结果如图5所示:同一位置,半径越大,芯片最高结温越高,半径为3 mm时,温度接近125℃,接近器件承受的极限温度;相同半径下,外边缘位置2、3的空洞面积是位置1的1/4、1/2,但最高结温只是稍低于位置1,位置2与位置1最大相差6℃,并且随着空洞半径的增大,位置2、3与位置1结温差减小。空洞处于焊料层内部和外边缘对结温影响差异较大,对位置4、5和6建模,可以得到类似结论。

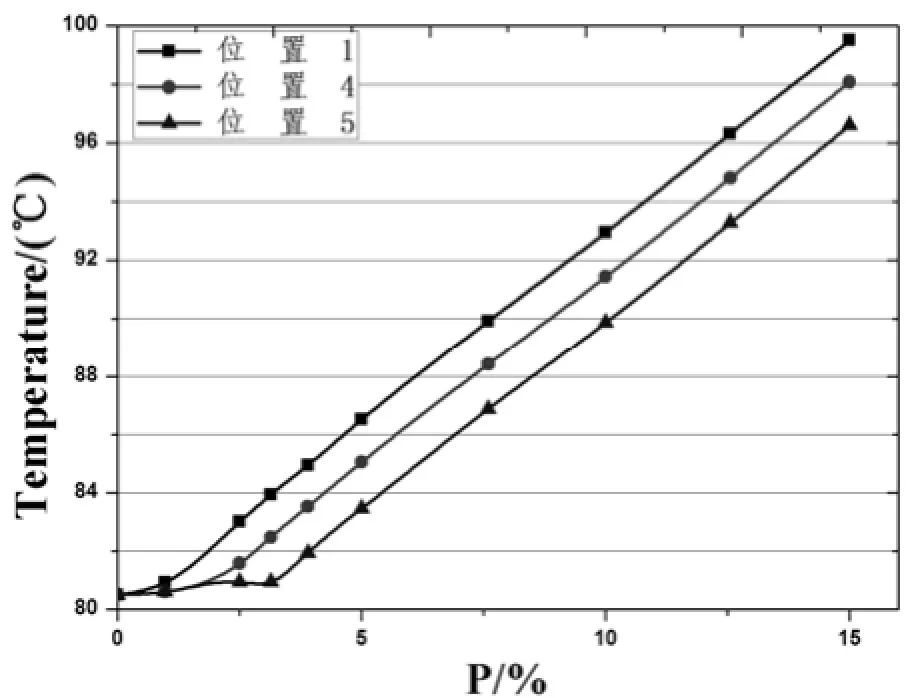

将半径与结温的关系转化成空洞率(P)和结温的关系,如图6所示,位置1、4、5在焊料层内部,空洞率与最高结温关系趋向线性,在空洞率较小时,曲线偏离线性,对芯片结温影响较小。对于外边缘位置2、3可以得到相同的结论。在空洞率相同时,外边缘(如位置2、3、6)空洞对芯片结温影响大于芯片内部(如位置1、4、5)空洞。

图5 不同位置下空洞半径对芯片最高结温的影响

为解释以上结论,可以引入传热学傅里叶定律:

其中,Q为导热传导的热量,λ为导热系数,A为垂直于热流的截面积,gradt为温度梯度,表征温度场在空间上改变的大小程度,温度增大方向为正。导热传导的热量Q与温度梯度gradt的绝对值和垂直于热流的截面积A成正比。如图4所示,在芯片的任意位置,水平和垂直方向都存在温度梯度,热量沿水平和垂直两个方向传导。芯片焊料层空洞阻碍芯片产热在垂直方向的传导,在稳态热传导的前提下,热量Q将沿水平方向传导。

公式(3)~(5)中,r为空洞半径,d为芯片厚度。空洞半径增大,空洞上方局部产热增多,温度梯度增大,促使温度升高。

空洞较小时,产热较少,温度梯度变化不大,对原温度场影响较小,对芯片结温影响小,随空洞增大,产热增多,对原温度场影响较大,对结温影响明显。对于边缘空洞,特别是位置2、3,相同半径下,空洞面积小,但温度梯度相差不大,导致空洞率相同时,外边缘位置空洞对结温影响大于内部位置空洞。因此生产制造时,尽量避免边缘空洞和大空洞的出现。

图6 不同位置下空洞率对芯片最高结温的影响

2.4单个空洞位置对芯片最高结温影响

前文对空洞大小影响进行分析,可以看出,芯片最高结温与空洞位置有关。对6个典型位置建模,结果如图7所示,空洞位置的不同改变了芯片原来的温度分布,最高结温离开中心位置,在空洞上方形成新的高温中心。

空洞由位置1沿直线分别移动到2、3,空洞半径取1.6 mm,结果如图8(D表示空洞圆心纵坐标,芯片中心为坐标系原点)。当D为2.9 mm时,空洞到达芯片焊料层边缘。在芯片内部(D < 2.9 mm),最高结温逐渐减小,沿1-2的路径,最高结温下降大约6℃,沿1-3路径,下降3℃。原因如下:半径和产热率相同时,Q/A不变,温度梯度不变,由于位置越远离中心位置,初始温度越低,导致空洞远离中心位置,结温降低。到达芯片边缘后,空洞由圆形变得不规则,热量Q和热流的截面积A变化复杂,公式(3)、(4)不再适用,Q/A变化趋势先增大后减小,结温最大值接近甚至高于中心位置,如1-2路径最大值113.3℃,1-3路径最大95.7℃。

前文表明,单个空洞大小、位置对芯片最高结温影响很大;引入三种规则的空洞分布模型,边缘分布、集中分布、均匀分布(如图9),讨论多个空洞的分布对芯片最高结温的影响。单个空洞大小相同,研究空洞率从5%到50%,三种分布对芯片最高结温的影响。

图7 典型位置的温度场(r=1.6 mm,单个空洞率为10%,功率损耗为75 W)

图8 不同位置空洞对芯片最高结温的影响

2.5空洞分布对芯片最高结温影响

图9 空洞的三种不同分布

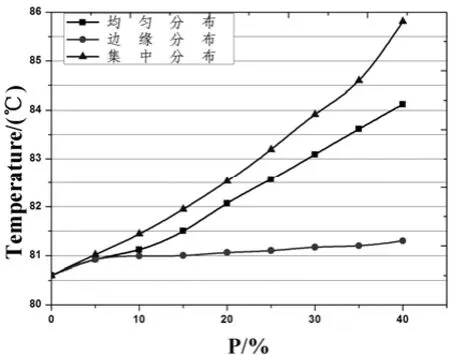

如图10所示,集中分布影响最大,均匀分布其次,边缘分布影响最小;温度分布图显示最高结温在中心位置处。对比图6可知,焊料层内部多个空洞分布对结温的影响难以达到相同空洞率单个空洞的影响效果。

由前文分析不难看出,多个空洞形成多个高温中心,每个空洞附近温度梯度远小于大空洞附近温度梯度,导致最高结温相对较小;多个空洞的分布,改变了原温度场的分布,分布越集中,空洞附近温度越高,温度梯度相同时,最高结温越高。对集中分布,调节空洞间隔进行建模,可以得到间隔越小,最高结温越高的结论,因此空洞分布越密集,结温越高。

图10 三种分布下空洞率对芯片最高结温影响

3 总结

文中选取位于芯片焊料层的贯穿型空洞,研究空洞大小、位置及分布对芯片结温的影响,重点分析外边缘空洞和空洞分布。结果表明:单个空洞越大,最高结温就越大;芯片焊料层内,远离中心位置,结温会降低;焊料层外边缘,空洞对结温影响复杂,空洞率相同时,对结温影响远大焊料层内部位置;多个空洞分布越密集,结温越高,但最高结温低于相同空洞率下单个大空洞的影响。

因此,空洞对结温、热阻等热参数的影响,不能仅靠空洞率来衡量,还需考虑空洞大小、位置、分布等因素,特别要注意边缘空洞。在芯片的焊接工艺中,应把空洞尺寸控制在合理范围,并避免芯片焊料层外边缘出现较大空洞,提高器件的可靠性。

[1] Oettinger F F,Blackbum D L. Semiconductor MeasurementTechnology:ThermalResistance Measurement [M]. Washington DC,US Department of Commerce,1990.

[2] 张小玲,张健,谢雪松,吕长志. IGBT热特性的仿真及焊料层分析[J]. 功能材料与器件科学,2011,17 (6): 555-558.

[3] 章蕾,郭好文,何伦文,汪礼康,张卫. 贴片焊料层厚度对功率器件热可靠性影响的研究[J].半导体技术,2007,32(11): 933-937.

[4] 张健,张小玲,吕长志,佘烁杰. IGBT焊料层中的空洞对器件热可靠性的影响[J]. 硅微电子学,2011,31(5): 517-521.

[5] 吴昊,陈铭,高立明,李明. 粘结层空洞对功率器件封装热阻的影响[J]. 半导体光电,2013,32(2): 226-230.

[6] 吴煜东,常桂钦,彭勇殿等. 焊层空洞对 IGBT 模块热应力的影响[J]. 大功率变流技术,2014,(1): 17-23.

[7] 谢鑫鹏,毕向东,胡俊. 空洞对功率芯片粘贴焊料层热可靠性影响的分析[J]. 半导体技术,2009,34 (10): 1026-1031.

[8] 田蕴杰,张小玲,谢雪松,佘烁杰,吕长志,王任卿. IGBT热疲劳工作对焊料层可靠性的影响[J].硅微电子学,2014,34(3):288-292.

[9] 郑钢涛,陈素鹏,胡俊,李国元. 焊料层空洞面积对功率器件电阻和热阻的影响[J]. 半导体技术,2010,35(11): 1059-1064.

[10] 徐玲,周洋,张泽峰,陈明祥,刘胜. IGBT模块焊料层空洞对模块温度影响的研究[J]. 中国电子科学研究院学报,2014,9(2):125-129.

[11] D. C. Katsis,Jacobus Daniel vanWyk.A Thermal Mechanical and Electrical Study of Voiding in the Solder Die-Attach of Power MOSFETs [J].IEEE TransactionsonComponentsandPackaging Technologies,2006 ,29,(1): 127-136.

[12] Otiaba K C,Bhatti R S,Ekere,et al.Numerical study on thermal impacts of different void patterns on performance of chip-scale packaged power device [J]. Microelectronic Reliability,2012,52:14049-1419.

[13] Jin Onki,Yasunori Chonan,etal.A new void free soldering process in large area,high power IGBT modules [C]// ISPSO`2000,2000,Toulousse,France: 367-370.

The Effect of Voiding in the Solder Die on the Temperature Distribution of IGBT Chips

Xia Yanfei,Luo Yifei,Wang Bo,Liu Binli

(National Key Laboratory of Science and Technology on Vessel Integrated Power System,Naval University of Engineering,Wuhan 430033,China)

Based on the IGBT seven-layer structure,a three dimensional finite element model is established to simulate the effect of voiding in the solder die on the temperature field of the chip,and the mechanism of the effect of voiding on the chip junction temperature is discussed. The results show that: voiding in the solder die change the cooling path and the temperature distribution of the chip,the larger the single hole,the higher the chip junction temperature,and the temperature rise is more significant in the center and outer edge location than other position in the chip,for multiple holes,the more concentrated the distribution,the higher the junction temperature.

finite element model; solder die voiding; temperature distribution

TM46

A

1003-4862(2015)12-0001-05

2015-09-11

国家自然科学基金重大项目(51490681)、国家重点基础研究发展计划(973计划)(2015CB251004)

夏燕飞(1989-),男,硕士研究生。主要研究方向:大功率半导体器件尽限应用及可靠性。

罗毅飞(1980-),男,副研究员。主要研究方向:大功率半导体器件尽限应用及可靠性。