基于FPGA的循环冗余校验码设计

成都理工大学信息科学与技术学院 周 亮 余小平

基于FPGA的循环冗余校验码设计

成都理工大学信息科学与技术学院 周 亮 余小平

本文主要介绍了循环冗余校验码的模块设计及其基本原理,并利用Verilog HDL设计循环冗余校验码,给出了基于FPGA的可编程逻辑器件的实现方法及其仿真结果.同时阐述了循环冗余校验码的应用前景。

循环冗余校验码;Verilog;FPGA

在现代数字通信中,要求信息在传输过程中所造成的数字差错必须足够低。但由于通信信道里存在的噪声和通信信道不理想的传输特性造成了信号的码间串扰,从而导致了信息在传输过程产生了差错。所以为了最大限度的保证通信过程中信息的完整性,就需要采用信道编码技术对可能发生的差错进行有效的控制,而循环冗余校验码就是其中一个最有效的编码技术。

1 循环冗余校验码基本思想

循环冗余校验码是一种校错能力很强且使用非常广泛的差错检验方法。其通用的构成可以描述为:K位的有效信息数据串和R位的循环冗余校验码并在一起传输。

1.1 循环冗余校验码生成基本原理

循环冗余校验码在通信信号校错里广泛使用。其基本原理是在发送端:将要发送的数据串序列当作一个多项式T(x)的系数(比如,多项式为T(x)=x5+x3+x+1,则此多项式的系数就为101011,同时可以自定义一个k次幂的称为生成多项式的多项式G(x),为了使原来的数据串序列在后面加入校验码,就必须使其向左移,所以用Xk乘以T(x),根据对二进制乘法的理解,得到的T(x)Xk,就是起到把T(x)原有数据串序列向左移动k位之后的结果。为了得到校验码,用G(x)去作除数,T(x)Xk作被除数,相除得到一个余数多项式R(x).然后将余数多项式R(x)并在数据串序列后面,把这串新的数据串序列作为发送序列发送。在接收端:再次使用自定义的生成多项式G(x)去除接收到的数据串序列多项式,如果相除所得到的余数多项式和在发送端计算得到的余数多项式相同,则表示信号传输正常,没有出现差错;反之,就表明信号传输错误。为了更直观的说明循环冗余校验码的生成过程、校验过程,以8位的有效信息数据串和4位的循环冗余校验码并在一起传输为例。

生成过程:

(1)假设要发送的数据串序列为11011101。自定义的生成多项式G(x)=x4+x3+x+1,其中k=4,相对应的序列为11011。

(2)把待发送的数据串序列向左移动4位,后面补0,从而得到新的数据串序列为110111010000。

(3)使用模2除法,用生成多项式序列去除新生成的数据串序列。即:

这样得到了余数多项式R(x)对应序列为1010。

(4)将余数多项式R(x)对应序列并到新数据串序列后面,得到带有循环冗余校验码的数据串序列:110111011010。

校验过程:

假如信息传输正常,接收到的带有循环冗余校验码的数据串序列必定可以被在发送端所自定义的生成多项式整除,也就是:

2 Verilog HDL核心程序

2.1 Verilog HDL实现循环冗余校验码的生成代码

其中polynomial表示生成多项式

if(dtemp[11]) dtemp[11:6] = dtemp[11:6]ˆpolynomial;

if(dtemp[10]) dtemp[10:5] = dtemp[10:5]ˆpolynomial;

if(dtemp[9]) dtemp[9:4] = dtemp[9:4]ˆpolynomial;

if(dtemp[8]) dtemp[8:3] = dtemp[8:3]ˆpolynomial;

if(dtemp[7]) dtemp[7:2] = dtemp[7:2]ˆpolynomial;

if(dtemp[6]) dtemp[6:1] = dtemp[6:1]ˆpolynomial;

图1

2.2 循环冗余校验码的校验代码

对循环冗余校验码的生成和校验进行了功能仿真,结果如图1所示。

3 循环冗余校验码的应用

由于循环冗余校验码强大的校验能力,在不同领域,循环冗余校验码的生成多项式位数也不同,根据IEEE官方文件显示,为了更好地保证校验可靠度,现在的位数越来越大,目前最长的己达到160位的循环冗余校验码。下面简单介绍几种常见的循环冗余校验码及其应用领域。

(1)USB接口用CRC5。

对应的标准生成多项式:

P(x) = x5+ x2+ 1

(2)ATM协议等用CRC8。

对应的标准生成多项式:

P(x) = x8+ x2+ x + 1

(3)文件传输通信协议,X25协议等用CRC16。

对应的标准生成多项式:

P(x) = x16+ x12+ x5+ 1

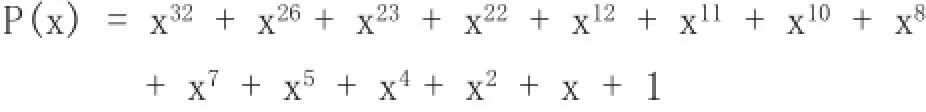

(4)IEEE802.3标准用CRC32。

对应的标准生成多项式:

4 结语

循环冗余校验码己经成为各行各业通信校验中最普遍的校验方式。本设计将循环冗余校验码的生成与校验过程进行细致的分析,最终采用Altera公司开发的FPFA芯片EP1C12Q240C8进行结果验证。实验表明FPGA在实现循环冗余校验码方面有着简单高效优势。在未来实现更多位的循环冗余校验有着更深远的用途。

[1]樊昌信,曹丽娜.通信原理[M].北京:国防工业出版社,2008.

[2]Volnei A.Pedroni.Circuit Design with VHDL[M].BeiJing:Publishing House of Electronics Industry,2005.

[3]蒋立平.数字逻辑电路与系统设计[M].北京:电子工业出版社,2008.

[4]阎石.数字电子技术基础(第四版)[M].北京:高等教育出版社,2008.

[5]花汉兵,付文红.EDA技术与实验(第2版)[M].北京:机械工业出版社,2013.

[6]周立功.EDA实验与实践[M].北京:北京航空航天大学出版社,2006.

余小平(1970—),四川邻水人,成都理工大学副教授,主要从事测试计量技术及仪器科研与教学工作。

周亮(1990—),江苏沭阳人,硕士研究生,研究方向:电子技术及通信。