基于FPGA的雷达目标模拟

邢依依,陈 伟

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室,陕西 西安 710071)

基于FPGA的雷达目标模拟

邢依依,陈伟

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室,陕西 西安710071)

摘要目标模拟在雷达的研制和生产中,不仅能加快项目开发的进度,还可降低研制成本。文中研究了基于FPGA实现雷达目标模拟系统的方法,搭建了以Xilinx公司Virtex-6系列芯片为核心的硬件平台。该系统可实时模拟点目标回波,能适应复杂调制波形。此外,文中还结合基于线性调频信号的验证,通过脉冲压缩等方法对系统的性能进行了测试,分析了雷达回波的信息。仿真结果表明,在理论的距离为1 200 m,延迟时间8 μs的条件下距离误差仅为11 m,延迟时间误差0.07 μs,在本项目允许范围内。系统可较好地实现雷达目标模拟。

关键词FPGA;雷达目标模拟;脉冲压缩

雷达发射的信号本身不包含任何信息,只有当发射信号遇到目标反射回波后才可包含目标的信息。若全部采用外场试飞,将会耗费大量的财力、物力和人力,其研制周期也相对较长,甚至在一些环境恶劣、极端天气的条件下实验难以进行,因此雷达目标模拟对雷达的性能和指标测试是一个关键部分,在现代雷达系统的研制和调试过程中,常采用目标模拟技术。

本文搭建了基于FPGA的硬件平台并采用Xilinx的ISE可编程开发软件平台实现雷达目标模拟。一方面FPGA有丰富内部资源,集成度高,功耗低等优点,使得整体系统有着高精度和稳定度,另一方面。结合Matlab进行仿真,将发射信号和回波信号的数据导出以验证系统,对系统的性能进行有效的评估。

1雷达目标模拟的基本理论

雷达的距离分辨力与信号带宽有关,带宽越宽,距离分辨力越好。信号在时域上的持续宽度越大,在频域上的分辨能力就越好,即速度分辨力越好。通过发射宽脉宽的信号以保证足够大的作用距离,且将接收到的回波信号通过脉冲压缩的方法获得窄脉冲信号,以提高距离的分辨力,解决作用距离和分辨力之间的矛盾。因此,为保证一定的信噪比的情况下,也为了解决检测能力、距离分辨力和测距精度之间的矛盾,应采用大时宽带宽积信号。而线性调频信号(LFM)就是其中一种应用最广的信号形式。

2雷达目标模拟的FPGA实现

2.1系统的整体结构

本文基于在FPGA中实现目标模拟的信号处理,将信号处理部分的设计框图如图1所示。

图1 信号处理部分设计框图

2.2系统的硬件设计

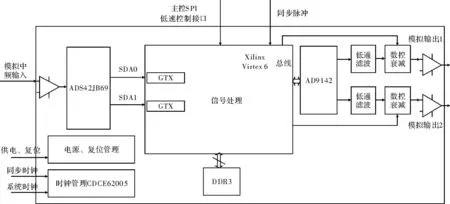

系统硬件部分由时钟芯片、A/D采样芯片、FPGA、外接的DDR3芯片、D/A芯片组成。硬件设计框图如图2所示。

图2 目标模拟硬件实现设计框图

时钟发生器选取TI公司的CDCE62005,可为ADC、FPGA、DAC提供高质量的时钟输入信号。晶振提供板上工作时钟,通过FPGA配置时钟发生器产生时钟。A/D采样芯片型号为ADS42JB69,是带有高速串行协议JESD204B的A/D转换器,16位分辨率,最大时钟速率250 MSample·s-1,采用高速串行接口和FPGA中的GTX连接。完成的是将采样到的信号通过其自带的高速串行接口发送给FPGA,而FPGA芯片采用Xilinx公司的Virtex-6系列,具体型号为XC6VLX240TFF1156。根据要求,目标模拟存储资源,时宽最大20 ms,按照250 MHz采样率,存储位宽16位,需10 MB容量,因此采用的为FPGA片外存储,本文中采用DDR3作为波形的存贮介质以实现片外存储,进而实现回波信号的时延功能。D/A芯片的型号为AD9142,16位分辨率,最大数据率为250 MSample·s-1,内插可到1 000 MSample·s-1,DAC输出的模拟信号再经过滤波器输出。

3系统的性能测试及评估

3.1检测原理

本文选用LFM信号,因其具备突出的特点是匹配滤波器对多普勒频移不敏感[4],即使回波信号有较大的多普勒频移,匹配滤波器仍能起到压缩的作用。LFM信号的数学表达式[5]

(1)

(3)

式中,td是信号回波的延迟时间。

在接收回波信号的同时不可避免的会接收到噪声以及各种干扰信号,为使信噪比最大、波形失真最小、鉴别出有用的目标,使用匹配滤波器以实现脉冲压缩。设发射信号为s(t),其频谱为S(w),则匹配滤波器在频率域的特性为

H(w)=kS*(w)exp(-jwt0)

(4)

脉冲响应函数为

h(t)=ks*(t0-t)

(5)

U0(w)=S(w)H(w)

(6)

代入式(3)可得输出信号[7]u0(t)为

(7)

3.2仿真测试结果

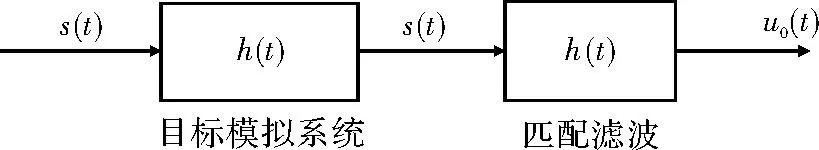

本文结合仿真完成了对系统回波的测试。将模拟后从D/A输出的回波信号导出。由于本文中D/A输出的是基带信号,故此处将信号发生器送入的发射信号先导入Matlab并在该环境下进行数字正交下变频,产生理论上的基带发射信号,再与D/A输出的基带回波信号匹配滤波,以评估系统的性能[10-11]。

图3 系统测试模型

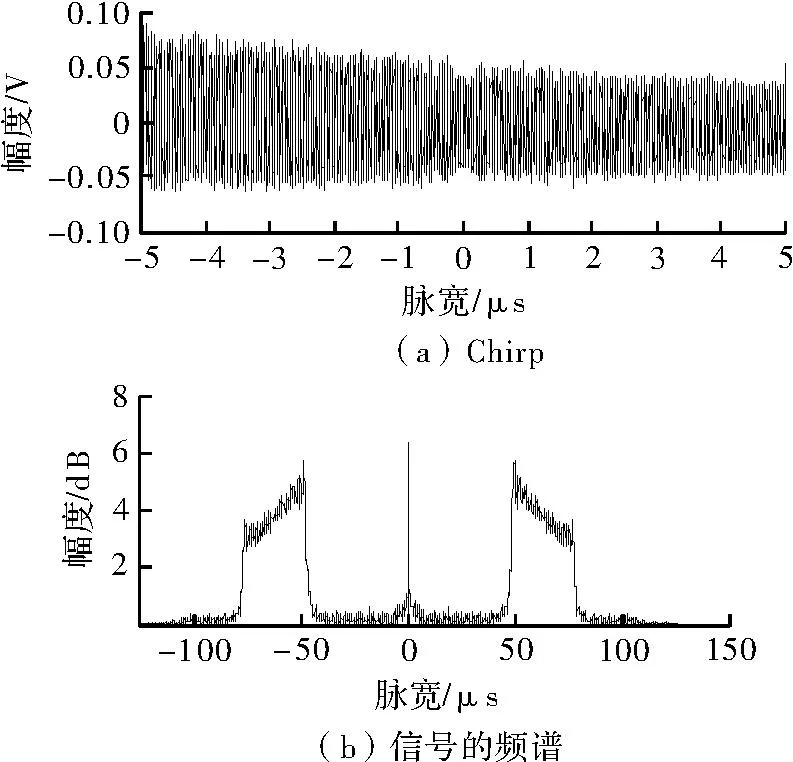

发射信号指标:信号载频f0=62.5MHz;带宽B=30MHz;脉宽τ=10μs。

图4 Matlab产生LFM信号的时域波形和幅频特性

经ArbExpress Application软件导入信号源后的发射信号波形和频谱如图5所示。

图5 示波器导出的发射信号时域波形和幅频特性

发射信号导入Matlab并在该环境下进行数字正交下变频,产生理论上的基带信号如图6所示。

图6 发射信号经下变频后的基带信号

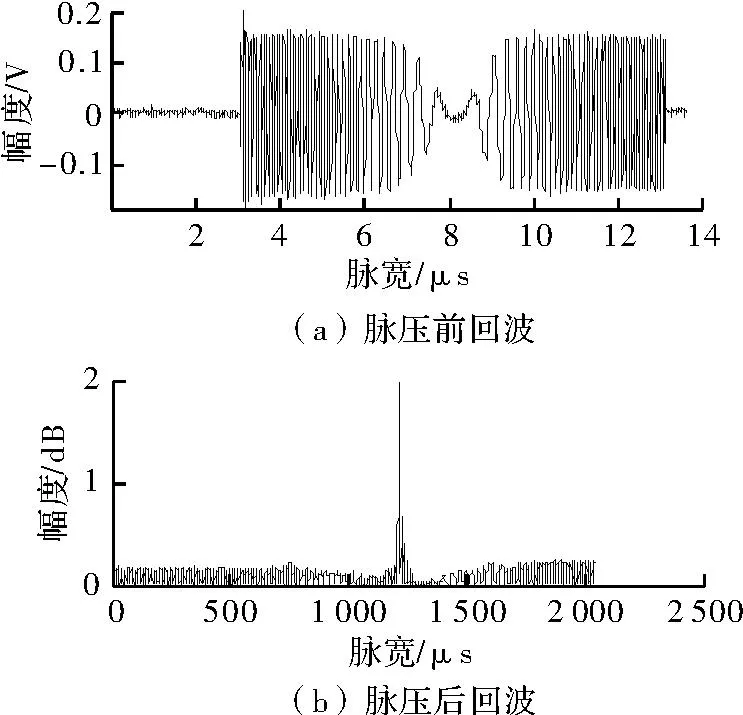

经过脉冲压缩后可得

图7 示波器导出的发射信号与回波信号匹配滤波的结果

图7(a)为I路回波信号,图7(b)为发射信号正交下变频后的I路和I路回波匹配滤波的结果。由图7可看出回波信号的延迟时间是8.07 μs,即目标和雷达间的距离是1 211 m。,而理论距离是1 200 m,延迟时间8 μs,即误差为11 m。经验证,回波延迟的误差在本项目允许范围内。

4结束语

本文通过提出基于FPGA的目标模拟的设计方法,论述了雷达目标模拟的基本原理,给出了硬件设计的思路、实现硬件平台的方法以及本文实现的器件和参数要求。结合Matlab,通过将电路板的输出信号经示波器导出数据与原始输入的发射信号数据进行脉冲压缩,以验证系统的性能。从仿真结果可以看出系统能够满足设计要求。

参考文献

[1]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,1995.

[2]Mark A Richards.雷达信号处理基础[M].邢孟道,王彤,李真芳,译.北京:电子工业出版社,2008.

[3]楼才义,徐建良,杨小牛,等.软件无线电原理与应用[M].2版.北京:电子工业出版社,2014.

[4]王菲.雷达中频数字接收与脉冲压缩模块实现技术[D].成都:电子科技大学,2007.

[5]廖建国,李永,李继杰.线性调频脉冲压缩雷达仿真研究[J].空间电子技术,2010(2):59-62.

[6]丁玉美,高西全.数字信号处理[M].西安:西安电子科技大学出版社,2005.

[7]张斌.中频采样数字脉冲压缩实现技术[D].成都:电子科技大学,2006.

[8]张明友,汪学刚.雷达系统[M].4版.北京:电子工业出版社,2013.

[9]陈志伟.基于FPGA的线性调频脉冲压缩雷达目标视频信号模拟[D].南京:南京理工大学,2007.

[10]肖开健,井伟,肖战牛,等.基于DDS的单脉冲体制雷达目标模拟的实现[J].电子科技,2011,24(11):13-15.

[11]刘明,王伟,杨英科,等.中频段雷达目标的实时模拟方法研究与实现[J].电子科技,2010,23(3):68-70,80.

Radar Target Simulation Based on FPGA

XING Yiyi,CHEN Wei

(Key Laboratory of Electronic Information Countermeasure and Simulation,Xidian University,Xi’an 710071,China)

AbstractTarget simulation both speeds up project development and reduces the costs in radar development and production.In this paper,the method of radar target simulation based on FPGA is studied and the hardware platform is built with the Virtex-6 series chips of the Xilinx Company as the core.The system is capable of real-time simulation of the point target echo and adaptation to complex modulation waveforms.System performance is tested by pulse compression methods combing the authentication with chirp signals,and the radar echo information is analyzed.Simulation results show that at a theoretical distance of 1 200 m and a lower latency of 8 μs,the actual distance error is only 11 m with a delay time error of 0.07 μs,within the allowable range in this project.

KeywordsFPGA;radar target simulation;pulse compression

中图分类号TN955+.2

文献标识码A

文章编号1007-7820(2016)04-161-04

doi:10.16180/j.cnki.issn1007-7820.2016.04.043

作者简介:邢依依(1989—),女,硕士研究生。研究方向:目标模拟。

收稿日期:2015- 09- 08