基于FPGA的模块化联网实验箱系统的设计与实现*

许逸波++郝慧杰++周润++肖建

文章编号:2095-6835(2016)13-0008-03

摘 要:由于传统电工电子实验箱平台存在陈旧落后、结构固定的情况,已经脱离了物联网革命的潮流,实验教学信息化改革迫在眉睫。在分析物联网原理的基础上,使用模块化设计,通过网口模块进行网络通信,采用单片机与FPGA协同处理控制,通过IIC总线驱动单元电路组合,完成了实验箱硬件结构和基于ARM和FPGA的IIC驱动程序、网络通信程序和系统控制程序,实现实验箱系统与控制终端远程互联,完成了13个基本实验,并可以通过更新实验模块拓展实验箱功能。实践证明,实验箱系统系统性价比高,可以突破时间与空间的限制,提高学生的实验效率,增强教学质量。

关键词:物联网;实验箱;模块化;单片机

中图分类号:TP368.1 文献标识码:A DOI:10.15913/j.cnki.kjycx.2016.13.008

随着各大高校对学生实践能力的重视,实验教学逐渐被提升到一个较高的地位。而目前,许多高校的实验平台都是从教仪企业采购的。该类平台的结构往往固定,而且采用的导线连接直插式电子元器件方式,存在分立元件过多导致电路结构杂乱无章、错误频现的弊端,造成实验内容更新慢、实际利用率低,难以满足学生日益增长的创新性实验需求。这在很大程度上制约着学生专业能力的巩固和提高。

此外,随着近年来物联网的兴起,实验室物联信息化已成为实验教学改革的必然趋势。从提高实验教学效率、实现信息化改革的角度出发,本文设计实现了一种具备物联特性的基于FPGA的模块化联网实验箱系统。它依托可编程器件和IIC总线通信技术,采用模块化设计,兼容多种实验电路单元,与互联网结合形成一个巨大的网络,提供功能可变、远程可控、虚实结合的实验平台,提升设备的通用性和更新速度,提高学生的实验效率,提高教学质量。

1 实验箱系统的总体设计

在实验教学物联化改革的趋势中,基于FPGA的模块化联网实验箱系统首先要解决的问题是设备通信。对于实验箱系统与测量仪器及客户端之间的通信,采用网口通信的方式更加合适,以ARM单片机为通信核心,通过串口转网口模块,实现实验箱系统的网络接入,便于用户对实验箱的操作以及波形数据测量;对于实验箱系统内部的通信,在众多的通信方式中,IIC总线作为一种出色的通信方式,资源成本极低,而且信息传输速率相对较高,具备多从机挂载能力。因此,采用IIC总线进行系统内部通信,便于FPGA对于实验电路模块的管理和控制。

另外一个需要解决的问题是实验内容的更新。基于FPGA的模块化联网实验箱系统采用模块化设计,依托IIC总线连接多个可插拔的电路模块,在无需改动控制单元的情况下,灵活动态地搭建实验电路。此外,可以根据学生在不同阶段不同层次的学习需求,采用更换电路模块的方式进行实验内容的更新,充分满足创新性实验需要。

当然,实验箱系统还需要包括处理模块、电源模块、编程下载口模块和信号输入/输出模块,加上之前的通信模块、总线控制模块和电路模块三个模块,共七个部分。系统采用星形拓扑结构,通过电源模块提供功能保障,以单片机和FPGA协同的处理模块为核心,向周边辐射展开各功能模块,实现实验箱系统的物联与重构功能。实验箱系统结构如图1所示。

2 单元模块设计

根据系统总体设计,基于FPGA的模块化联网实验箱系统集成多种功能,采用双层结构,下层为实验箱底板,上层为各功能模块,包括处理模块、电源模块、通信模块、总线控制模块、编程下载口模块、信号输入/输出模块和电路模块。图2为实验箱示意图。

2.1 处理模块设计

实验箱系统借鉴片上系统(System on Chip,SOC)的思想,采用单片机与FPGA协同工作的方式,充分发挥FPGA的资源优势以及ARM微处理器的低成本、低功耗和高性能,用 ARM单片机实现实验箱系统与网络的信息通信,用FPGA完整控制内部系统,两者之间采用一组I/O口进行并行数据通信。其中,FPGA处理单元采用Xilinx的Spartan XC3S50,作为5万门级

的可编程芯片,加上144个I/O口,其性价比高、处理速度快,完全可以满足电工电子实验教学的基本需求以及学生的创新性实验需求;单片机处理单元采用的是STM32F103VE,其采用的ARM CORTEX-M3的内核和32位精简指令集,成本低,性能优异,在72M的工作频率下,具备较高的处理速度和较强的处理能力,可以进行较高速的数据通信和处理。

2.2 电源模块设计

实验箱系统主要用到的是+1.2 V、+3.3 V和±5 V,其中,+1.2 V和+3.3 V分别为FPGA芯片的内核与I/O口供电,使用±5 V给各模块器件供电。1.2 V电源电路如图3所示。

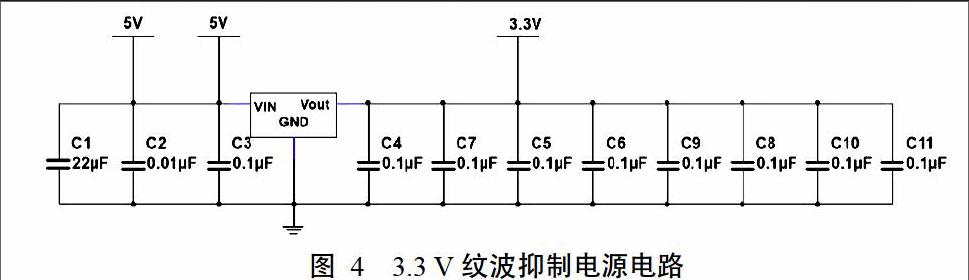

具体做法如下:①采用XL2576S降压型开关稳压器,将由外部输入的12~40 V电压信号进行降压并稳定输出5 V;②将5 V电压作为输入信号,通过AMS1117-3.3电源芯片降压至所需的3.3 V;③以3.3 V电压作为输入信号,通过AMS1117-1.2电源芯片来获取1.2 V的目标电压。此外,考虑到电源正负极反接的可能,在信号输入端采用最大反相电压为45 V的1N5817二极管——超过了学生直流电源的最大输出电压,充分保护电源模块及实验箱系统。3.3 V纹波抑制电源电路如图4所示。

由于系统中的各功能模块对电压值具有较高的要求,因此,如图4所示,可以在输出端外接成排接地电容,有效地滤除纹波,提高电源质量,给整个物联化实验箱系统提供纹波较小的工作电压。

2.3 通信模块设计

通信作为必不可少的一部分,其主要由两部分组成,分别为RS232串口单元和网口转串口单元。通信模块与处理模块连接,其中主要是采用ARM处理核心来进行数据的传输和处理的。RS232串口单元用于终端客户机与实验箱进行有线数据传输,在9 600波特率的速率下进行信息交互。网口单元主要由串口转以太网模块构成,模块集成 10/100M 自适应以太网接口,最高波特率256 Kbps。将终端客户配置为TCP Client工作模式,实验箱配置为TCP Server,采用用户/服务器的工作方式,实现实验箱与客户终端之间的数据传输,同时以串口数据的形式将数据发送至处理模块。由于串口工作电平不同,在串口和控制电路之间还需要RS-232线路驱动器/接收器——ADM3202RN,通过升压转换器加上电压电平转化发射/接收器,实现通信单元与单片机的隔离,保护电路,防止发生高电压损坏电路的情况。

2.4 总线控制模块设计

基于FPGA的模块化联网实验箱系统的核心内容是实验电路的构成,总线控制模块是建立在IIC总线和网络通信技术基础上的,由单片机通过网口来接收客户端数据,同时把信息返回给通信模块,实现信息的交互;然后单片机和FPGA协同处理控制命令,并主要通过FPGA来确定电路的重构方式,采用IIC总线主从应答的方式,选择所需的电路模块,通过控制命令,实现FPGA对单元电路的组合控制,确定各单元电路的动态组合,实现实验电路重构。IIC结构如图5所示。

该模块是基于FPGA的模块化联网实验箱系统的特点,由于赋予各电路模块唯一的IP地址,使得这些模块可以通过同一组IIC总线来实现数据通信,降低了产品的整体成本。此外,采用的环形布局和布设的多组接插口,不仅提高了系统的集成度,减少了导线长度,还可以降低信号衰减,提高系统的稳定性。

2.5 电路模块设计

电路模块是基于FPGA的模块化联网实验箱系统的硬件实现部分,由模拟电路模块和数字电路模块组成,负责提供构成电路的多种元器件和小规模电路模块。其中,数字电路相对简单,可以由FPGA来直接控制和生成所需电路,当然也可以采用独立的电路模块来实现;而模拟电路要复杂得多,信号不再局限于“0”和“1”。因此,只能采用模块来构成电路,通过FPGA进行模块的组合拼接,搭建实验电路。此外,实验板上保留了多个用于激励信号输入、采集和控制的管脚,进一步增加了系统的灵活性。

2.6 信号输入/输出模块

基于FPGA的模块化联网实验箱系统采用的FPGA具有144个I/O口资源,在此预留了5个输入信号端与5个信号输出端,采用标准的4 mm香蕉插头,降低信号衰减幅度,提高系统可靠性。

2.7 编程下载口模块

基于FPGA的模块化联网实验箱系统中采用的是可编程器件与单片机作为处理单元,因此需要分别设计下载模块。

(a) (b)

图 6 编程下载接口

对于单片机而言,从节约系统资源和提高下载效率的角度出发,采用SWD烧录模式,仅需GND、VCC、SWDIO和SWDCLK 4个端口就可以实现仿真器与STM32的连接。在高速模式下,它比JTAG更加可靠,烧录成功率更高,如图6(a)所示;对于FPGA而言,采用JLINK仿真下载的方式,则至少需要VCC、GND、TDO、TMS、TCK和TDI6个接口,所有接口采用标准间距2.54 mm,如图6(b)所示。

3 实验箱应用

基于FPGA的模块化联网实验箱系统的基本功能如表1所示。

与传统的基于8051的电工电子实验箱相比,该实验箱的批量生产成本约700元。尤其在实验箱网络接入之后,用户只需支付网络平台费用,成本极低,而且还能够通过网络进行真实的实验学习。表1所列举的实验内容只是最基础的一部分,可以根据学生实验需求,通过更换电路模块的方法来更新的实验内容.因此,该实验箱系统的功能更加全面,可满足学生的创新性学习。

考虑到大学生创新训练的需要,实验箱上预留了编程下载口模块和多个I/O口,提供实验箱的二次开发空间,使得该实验箱可以作为学生参加大学生电子设计竞赛、挑战杯竞赛的赛前训练之用,以学促赛,以赛促学。

4 结束语

基于FPGA的模块化联网实验箱系统包括处理模块、电源模块、通信模块、总线控制模块、编程下载口模块、信号输入/输出模块和电路模块,集成多种常用电子元器件,采用IIC总线控制的方式,根据任务要求进行单元模块的动态组合,实现不同的电路功能。以网络服务器为支撑的实验箱系统,采用客户终端控制的方式,进行网络接入、数据交互、远程控制和电路重构,摆脱了电工电子实验中时间和空间上的限制,提高了学生实验的效率,增强了实验内容的丰富性和灵活性,为实验教学提供了一个功能可变、远程可控、虚实结合的硬件平台。此外,作为教育改革中的一部分,本设备的成功研制,对实验教学的信息化改革和建设具有一定参考意义。

参考文献

[1]惠煌,赖晓晨,迟宗正,等.高校单片机教学实验设备自制模式探索[J].实验技术与管理,2012,29(5).

[2]周冠玲,冯占英,李战.“单片机原理及应用”课程教学改革的探讨[J].中国电化教育,2012,33(6).

[3]黄卫华,贾历程.“基于FPGA的EDA实验系统改革与实践”[J].实验室研究与探索,2012,31(4).

[4]部德才,张永平.基于LabVIEW的虚拟数字存储示波器的设计[J].科技与创新,2014(20).

[5]于娟,唐瑞.基于89C52单片机的LED显示器设计[J].科技与创新,2016(01).

[6]王汉森.一种智能功能集成的设计方法及实例[J].科技与创新,2016(01).

[7]贾萍,丁向荣,胡美兰.“教、学、做”一体化单片机教学实验平台的设计与应用[J].实验技术与管理,2012,29(6).

[8]胡文华,胡仁喜.Altium Designer 13电路设计[M].北京:化学工业出版社,2013.

〔编辑:胡雪飞〕