基于HDMI标准的视频数据编解码器设计

肖 剑,陈 月,郭 亮

(长安大学 电子与控制工程学院,陕西 西安 710064)

基于HDMI标准的视频数据编解码器设计

肖 剑,陈 月,郭 亮

(长安大学电子与控制工程学院,陕西 西安 710064)

介绍了HDMI收发系统的链路结构,研究和分析了HDMI接口标准中视频数据的接收方法和编解码算法,使用Verilog HDL语言设计了视频数据的编解码电路,选用Modelsim6.5e工具进行了仿真验证。仿真实验的结果表明,所设计的各模块电路均能够对视频数据进行正确的编解码,满足HDMI规范对视频数据编解码的要求。

高清晰度多媒体接口;视频数据;编解码算法;收发器

近年来,以高清晰多媒体接口(High Definition Multimedia Interface,HDMI)为代表的数字接口代替传统的模拟接口已成为趋势。HDMI接口实现了高速无压缩的视频和多声道无损音频数据传输,并向后兼容DVI标准。HDMI规范通过先进的编码算法统一并简化了用户终端接线,能够提供高达10.2 Gbps的数字化无损的音视频信号传送。选用最小化传输差分信号(T.M.D.S)技术,将8位像素数据转换为10位像素数据进行传输,实现了较远距离的高清晰度数字音视频信号传输和直流平衡的数据传输[1-4]。但是即使满足HDMI标准单链路数据传输的要求,收发系统中单个通道的数据传输速率也高达1.65 GHz,使得对高速的视频数据信号进行实时的编解码并满足HDMI准则要求成为设计难点。

本文介绍了一种实现HDMI中数字视频信号接收的方法,对其编解码算法进行了分析与研究。使用硬件描述语言Verilog HDL设计完成了满足HDMI准则要求的视频信号编解码器,选用Modelsim6.5e工具进行了仿真验证,结果表明了设计的合理性,满足HDMI规范对视频数据编解码的要求。

1 HDMI收发系统的链路结构

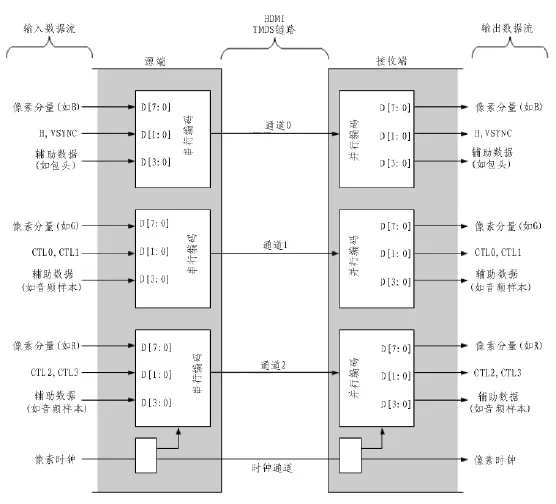

HDMI电缆和连接器中共包括4个差分线对,它们构成了T.M.D.S数据通道和T.M.D.S时钟通道,用于实现满足HDMI标准要求的视频数据、音频数据和辅助数据。在3条T.M.D.S数据通道中传输的是视频编码、音频编码和辅助数据。T.M.D.S时钟通道传送以像素时钟速率运行的T.M.D.S时钟,并作为接收端实现时钟数据恢复的参考时钟频率。发送端视频编码过程中,三路数据通道中每一路中的8位视频数据通过T.M.D.S编码转换为10位的直流平衡信号,以差分信号的模式串行输出,每T.M.D.S时钟周期传输10位数据。HDMI链路由三路T.M.D.S数据通道和一路T.M.D.S时钟通道构成。T.M.D.S的时钟通道的运行速率与被传递的视频的像素速率有一定的比例关系。每一个T.M.D.S时钟通道周期里数据通道传输10位的字数据到接收端,接收端在恢复时钟和数据的同时,还要实现字符的同步和每一位数据的相位对齐传输。完整的HDMI编解码链路结构如图1所示[6]。

HDMI信源端编码电路的输入数据流一般包含视频像素数据,数据封包和控制数据。数据封包流由音频数据、辅助数据和相关联的ECC组成。在每条T.M.D.S通道中,不管是8位的视频数据,4位的音频数据还是2位的控制数据,总共这些数据在通过众多不同的方式处理后,最终传送给T.M.D.S编码器进行编码。HDMI链路操作有3种形式,为视频数据周期、数据岛周期和控制周期。在视频数据周期中,传送的是数据通道的有效像素。在数据岛周期中,音频和辅助数据通过利用不同的数据包传递。控制周期出现在两个非控制周期之间。

2 视频编解码算法及程序设计

2.1视频编码算法及程序设计

由HDMI编码规范要求知,视频数据或控制信号通过视频数据周期与控制周期相协调来共同完成T.M.D.S编码[4]。当使能信号DE为高电平时,通过对视频数据周期的控制,将8位的视频信号通过编码转换为10位信号输出;当使能信号DE为低电平时,通过对控制周期的控制,2位控制信号经编码后输出10位码元。每条T.M.D.S通道均有两个控制信号介入编码控制,3条通道总计6位数据,每一条通道的2位数据在控制周期被编码为10位数据。视频编码过程可以分为两步来实现,首先使用同或运算或者异或运算将8位的视频信号编码为9位的中间信号,具体选择同或运算还是选择异或运算作为编码算法,是以输入的8位视频数据中 “1”的个数来作为判断条件的。当输入的数据值中“1”的个数大于4或输入的数据值中“1”的个数等于4且输入数据的D0位为0时,选择同或运算的编码算法;否则,选择异或运算的编码算法。其中,第一步编码产生的9位编码字的D8位用来表示用的是哪一种编码算法类型,即当该过程选用的编码算法是异或逻辑运算时,编码输出的D8位为逻辑高电平“1”;而当该过程选用的编码算法是同或逻辑运算时,则编码输出的D8位为逻辑低电平“0”。

图1 HDMI编解码链路结构

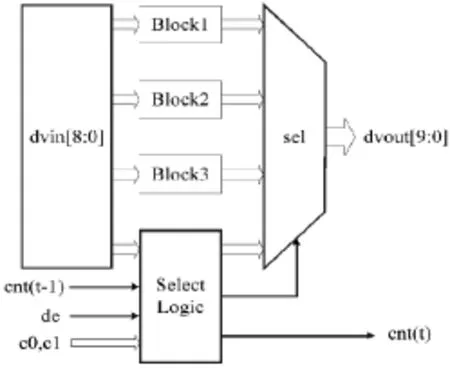

在第二步编码流程中还包含了控制信号的编码,通过寄存器参数cnt来控制编码,以保证送出的10位编码数据中的逻辑高电平“1”的个数和逻辑低电平“0”的个数尽可能相等,从而实现传输信号的直流平衡。当DE为高电平时,将对第一步编码过程中输出的9位编码数据进行下一步的编码运算,最终得到10位的T.M.D.S编码。当DE为低电平时,将对控制信号进行编码运算。因此,得出9位到10位编码电路结构如图2所示。

图2 视频信号9bit/10bit的编码电路结构

本模块的程序设计使用Verilog HDL语言,结合编码电路结构和算法流程,首先对各个接口信号进行了定义,最后得到一路T.M.D.S链路的编码程序encoder.v,通过对程序进行例化得到三路T.M.D.S链路的编码器电路。

2.2视频解码算法及程序设计

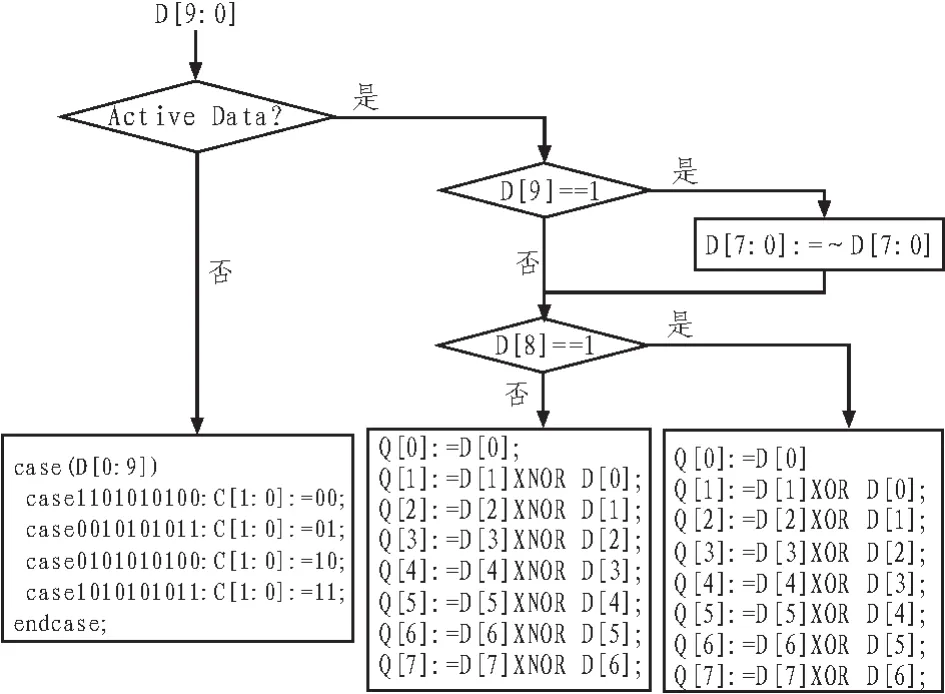

视频解码电路的算法流程如图3所示[7,8]。10位串行数据通过HDMI传输通道送入接收端后,首先是进行串行—并行转换,将串行数据转换为并行数据,10位的并行数据通过解码运算后得到恢复的8位视频信号、2位控制信号和有效视频使能信号DE。

图3 视频解码电路的算法流程

HDMI接收端的解码器能够对10位的编码信号同时进行解码。视频数据信号解码模块、控制数据信号解码模块和使能数据信号解码模块分别输出的是8位视频数据信号、2位控制数据信号和1位使能数据信号。解码输出的使能数据信号用于有效输出标志,其用来判断解码出的信号类型,当使能数据信号解码结果为逻辑高电平“1”时,视频数据信号解码模块的输出用于解码电路的有效输出,否则,控制数据信号解码模块的输出用于解码电路的有效输出。

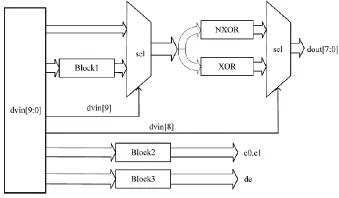

视频数据解码电路的程序设计如图4所示,Din[9:0]是数据输入的10位解码信号。Block1是对输入数据信号的Din[7: 0]位取反,在选通数据信号Din[9]的作用下,将Block1输出的低8位取反数据信号各自送给同或和异或两个解码运算模块,通过运算后根据解码信号的Din[8]位的逻辑高低电平,经二选一的选择器,选择两个逻辑运算结果中的一个作为最后解码数据输出的8位视频数据信号Dout[7:0]。Block2是控制数据信号解码模块,其解码数据输出结果仅有四种情况。Block3是对使能数据信号DE进行解码运算的模块,当解码电路输入的10位的待解码信号Din[9:0]是视频数据信号的编码结果时,使能信号数据解码模块、控制数据信号解码模块和视频数据信号解码模块均会有解码信号输出。同样的,当控制数据信号解码模块的输入数据信号作为解码电路输入时,视频数据信号解码模块和使能数据信号解码模块也有数据信号输出。即不管是视频数据信号编码还是控制数据信号编码,当这10位待解码信号作为解码电路输入时,视频数据解码电路的各模块均会有输出。此时,视频数据解码电路选择最终有效的输出结果是视频数据信号还是控制数据信号,由Block3的解码输出结果DE的逻辑电平状态决定,当DE为逻辑高电平“1”时,视频信号Dout[7:0]为有效的输出信号,而当DE为逻辑低电平“0”时,则控制信号{C1,C0}为有效的输出信号。

图4 视频解码电路程序设计

3 视频编解码器的仿真结果

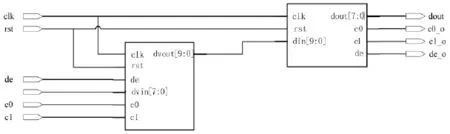

视频编码模块和解码模块分别属于HDMI发送端的发送芯片Transmitter和接收端的接收芯片Receiver,且它们之间也存在并转串电路、驱动电路、T.M.D.S链路、字符调整和多通道同步电路、时钟和数据恢复电路、串行转并行电路等一系列功能电路,通过将发送端的编码模块和接收端的解码模块直接相连进行功能仿真验证。新建top_hdmi.v文件,在此文件中对encoder和decoder进行例化,将各端口互连,编写为整体仿真提供激励信号的时序测试文件top_tf.v。连接好的顶层模块如图5所示。

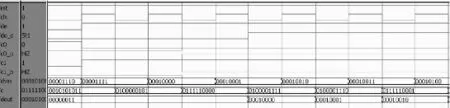

图5 编解码模块顶层连接原理

将top_hdmi.v和top_tf.v加入仿真软件Modelsim6.5e中进行编译仿真,在符合规范的基础上,输入信号激励的描写应尽量穷举所有的可能性,因此,可以根据编码模块仿真时所使用的激励文件来指定本模块的激励,仿真结果如图6所示。从编解码电路的联合仿真结果可以看出,不管是视频信号还是控制信号,当作为编码电路的输入信号时,若解码电路输出的信号与输入信号能够保持一致,那么就验证了电路设计的正确性。

图6 编解码器仿真波形

4 结束语

论文通过对HDMI接口技术的研究,设计实现了HDMI视频信号的编解码器算法,并根据算法进行了程序设计,编写完成了Verilog HDL代码。最后,以Mentor公司的仿真工具Modelsim6.5e对编写的代码进行了仿真验证,仿真结果表明了设计的正确性与合理性,满足HDMI规范对视频数据编解码的要求。

[1]HDMI Licensing,LLC.HDMI Specification 1.4[S].www.hdmi. org,2009.

[2]Martin,Michael A.Assuring interoperability of HDMI Interface standards[C]//SID Conference Record of the International Display Research Conference,2005,79-82.

[3]N.Gupta,P.Bala,V.K.Singh.Area&Power Efficient 3.4Gbps/Channel HDMI Transmitter with Single-Ended Structure[C]//VLSI Design and 12th International Conference on Embedded Systems,2013:142-146.

[4]Nair,R.ComLSI Inc.,Mesa.Enhancing Signal Integrity in Cables:DVI to HDMI and Class-B Differential Signaling[C]. IEEE International Symposium on Consumer Electronics, 2007.

[5]Hao Liu,Islam Mohammed.An HDMI Cable Equalizer with Self-Generated Energy Ratio Adaptation Scheme[J].IEEE Transactions on Circuits and Systems II:Express Briefs, 2009,56(7):595-599.

[6]Bursky,Dave.High-def interface streamlines HDTV video processor[J].Electronic Design,2005,53(3):28.

[7]肖剑,王永顺.基于DVI的时钟数据数据电路设计[J].半导体学报,2008(6):63-67.

[8]李朝锋,杜连芳,孙述桂.利用T.M.D.S均衡技术实现HDMI信号的远距离传输[J].科技创新导报,2008(14):13.

[9]戴仕勇,马潮,韦波.HDMI音频传输技术及设计要领[J].电视技术,2007(S1):65-67.

Design of video data codec based on HDMI

XIAO Jian,CHEN Yue,GUO Liang

(Institute of Electronics and Control,Chang'an University,Xi'an 710064,China)

Introduced the link structure of the HDMI transceiver system Briefly,the Codec algorithm of the video data in HDMI protocol is studied and analyzed.The encoding and decoding circuit of video data is designed with Verilog HDL language and verificated by Modelsim6.5e tools.The simulation results show that the tranciever modules can realized the encoding and decoding functions and met the HDMI specification requirements.

HDMI;video data;codec algorithm;transceiver

TN919

A

1674-6236(2016)13-0190-04

2015-07-20稿件编号:201507144

肖 剑(1975—),男,陕西西安人,副教授。研究方向:控制理论与控制工程。