隔离可修调低功耗基准电压源

杨 正

(西安电子科技大学 微电子学院,陕西 西安 710071)

隔离可修调低功耗基准电压源

杨正

(西安电子科技大学 微电子学院,陕西 西安710071)

介绍了一种新型的可修调低功耗基准电压源。为适应低功耗集成电路应用,该设计采用共源共栅结构代替传统的放大器结构,使基准电压源的功耗大大降低;为克服由模拟集成电路设计工艺波动而导致的电阻值不精确的问题,该设计引入了电阻修调电路,使该基准电压源在各个工艺角下都能有很好的基准电压输出。同时,隔离式的电阻修调改善了传统的直接熔丝修调带来的噪声影响。在SMIC 0.18μm 3.3V标准CMOS工艺下应用spectre仿真,结果表明,温度变化范围为-40℃~100℃时,温度变化1℃,电压变化量为十万分之一,室温下的参考电压输出为1.22V,3.3V电源电压下的功耗约为3.6μW。该基准电压结构适用于低功耗集成电路设计。

基准电压源;模拟集成电路;低功耗;修调;启动电路

基准电压源是一个具有特定温度特性的且与工艺和电源无关的直流电压,目的是给其他电路提供稳定的静态偏置,使其他电路能够工作在正常状态。基准电压源是许多电子设备的重要组成部分,从基本的数字电路(如动态随机存取记忆体(DRAM的)、固态存储器(E2PROM))到混合信号之间需要的模拟,到数字转换(A/D)和数字模拟转换器(D/A),以及RF电路等[1-4]。电压基准对温度及参考电压的依赖性无疑会影响这些应用程序的性能,一个稳定的参考电压相对于温度和电源电压的变化必须具有低灵敏度的特性。

大部分参考电压源为带隙参考电压,所谓能带间隙,是指硅半导体材料在热力学温度为零度(0K)时的带隙电压,其数值约为 1.205V。带隙基准源的基本原理是根据硅材料的带隙电压与温度无关的特性,利用Vt的正温度系数与双极型晶体管VBE的负温度系数相互抵消实现低温漂、高精度的基准电压[5-9],其原理如图1所示。

图1 带隙电压产生原理Fig.1 Principle of band gap voltage produced

本文介绍了一种新型的可修调低功耗基准电压源电路。为适应低功耗集成电路应用,该设计采用共源共栅结构而非传统的放大器结构,使该基准电压源的功耗大大降低。为克服由集成电路设计工艺偏差而导致的不精确的电阻值,该设计引入了电阻修调电路,使该带隙基准在各个工艺角下都能有稳定的基准输出。同时,隔离式的电阻修调改善了传统的直接熔丝修调带来的噪声影响。

1 电路结构

1.1基准电路

典型的带隙基准电路如图2所示,首先通过推导,确认正负温度系数的量,之后再按照电路连接方式,推出VBE的温度系数,已知

(1)

(2)

(3)

由式(3)可得VBE具有负的温度系数。另外,

(4)

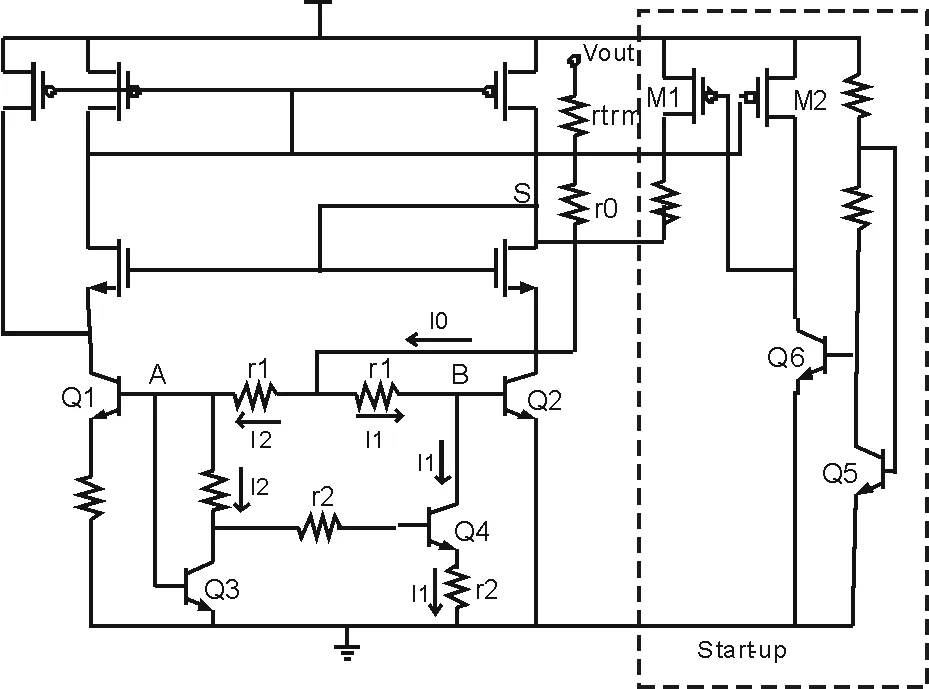

放大器结构的引入虽然保证了电路功能的实现,但流过放大器的电流没有用于形成带隙电压上,造成电流浪费,使电路的功耗大大增加。为克服传统带隙电路的缺点,提出了一种新型的基准电压源结构,如图2所示,该结构不再利用起电压钳位作用的放大器,取而代之的是共源共栅结构[12],几乎所有电流消耗都用于产生带隙电压上,因此大大节约了功耗,适用于低功耗集成电路设计中。

图2 新型基准电压源结构Fig.2 A new reference voltage source structure

在该电路中,VA≈VB,

(5)

(6)

因此

VBE3-VBE4=Vtln3。

(7)

又因为

VBE3-VBE4=I1r2+I2r1=2I1r2,

(8)

所以

Vtln3=2I1r2,

(9)

得到

(10)

因此

(11)

通过调节式(11)中电阻比例,可以实现室温下的零温漂系数。

为保证带隙正常启动,需要设计相应的启动电路,如图2中的电路启动时,Q5,Q6初始均处于关断状态,随着电压升高,Q5,Q6几乎同时打开,导致V2输出较低电平,从而开启M1,带隙启动后,M2导通,又将V2拉高,关断M1,断开带隙与启动电路的连接,完成启动过程。

电源抑制比是带隙基准源一项重要的性能参数。与其他模拟电路相同,带隙基准的输入电源上有噪声,这些电源线的噪声也会对输出信号造成影响,为保证电路性能必须适当地抑制噪声。而电源抑制比就是测量抑制这种偏差程度的性能指标,一般将其定义为:从输入到输出的增益除以从电源到输出的增益,它是一个交流量。电源抑制比越大就表示抑制能力越强,输入对于输出的影响也越小。本设计采用共源共栅结构来解决这一问题,在参考源中,电源抑制比可以表示为从电源到地的阻抗分压器,输出电压为中间节点,可以表示为如下形式[13]

(12)

式(12)中,Znm表示参考节点对地的等效阻抗,Zpm表示参考节点到电源的等效阻抗。从该式可以看出增加Zpm就可以增大PSRR的值。而共源共栅结构可以起到增加Zpm的目的。由此可见,该设计采用的共源共栅结构可以起到增大电源抑制比的作用。

1.2隔离式电阻修调

在模拟集成电路中,由于模拟集成电路设计工艺波动,一般很难保证精确的电阻值,在很多应用中为保证功能的正确性,常常需要微调电阻[14],对于电压基准更是如此。为保证带隙在各个工艺角下的良好性能,设计了相应的修调电路。传统的熔丝修调方案为:电阻值设计为二进制加权形式(如20R,21R,22R,…,2n-1R),通过控制焊盘之间熔丝的熔断与否调节电阻R0的值,使其在R0与R0+15R之间以步长R变化,从而达到调节带隙温漂系数的目的。然而传统的熔丝导线与微调电阻直接相连,容易受到噪声干扰,这里采用了隔离式的MOS开关控制电阻修调,避免了噪声干扰。

该设计的修调结构如图3所示,是隔离式的MOS开关控制电阻修调结构。MOS开关控制各个修调电阻接入与否,而各个MOS开关的控制信号与熔丝电阻完全隔离,彻底避免了熔丝过程的噪声干扰。

EN为与带隙启动同步的使能信号,带隙完全启动后为高电平。随着带隙的启动,使能信号EN逐渐升高,由于反向器的延时作用,与非门的输出信号Pro输出窗口式的低电平,在此低电平期间编程电路起作用。修调电路具体工作过程如下:

1)Pro=“0”,编程电路使能,编程电路编程信号S1~S4根据熔丝熔断或未熔断的状态,编程电路输出高电平或低电平,CCMOS此时处于求值状态,将S1~S4求值至逻辑高或逻辑低电平;

2)Pro=“1”,编程电路被隔离,编程电路的状态改变不影响CCMOS的输出,CCMOS处于锁存状态,保持MOS开关的控制信号O1-O4,其信号值不受编程电路状态改变的影响。

图3 修调电路Fig.3 Trimming circuit

2 仿真结果

在SMIC 0.18μm 3.3V标准CMOS工艺下,应用spectre仿真。其直流温度曲线如图4(a)所示。由图4(a)可知,当温度范围为-40℃~100℃时,温度变化1℃,基准输出电压变化量为十万分之一,室温下(25℃)达到零温度系数。在3.3V电源电压下,功耗约3.6μW。标准工艺角下电阻修调后((0~15)*r)的基准输出如图4(b),分析结果可知,由于电阻修调作用,使得电压基准输出在整个温度变化范围内从正温度系数到负温度可调。

图4 基准电压源温度仿真图Fig.4 The benchmark voltage source temperature simulation diagram

修调前后的不同工艺角下直流温度曲线如图5(a)与图5(b)所示,分析对比可知,经过电阻修调后,该带隙基准性能大大改善,使其在不同的工艺角下都能输出稳定的基准电压。

图5 修调前后温度仿真图Fig.5 Temperature simulation diagram before and after trimming

电源抑制比如图6,由仿真图形可得,10Hz下,电源抑制比达-70.4dB,100Hz下,电源抑制比为-69dB。

图6 电源抑制特性曲线Fig.6 Power suppression characteristic curve

3 结 语

本文介绍了一种新型的可修调低功耗基准电压电路。采用共源共栅、电阻微调等技术,并在电路中加入启动电路。在SMIC 0.18μm 3.3V标准CMOS工艺下应用spectre仿真,分析结果表明,温度变化范围为-40℃~100℃时,温度变化1℃,电压变化量为十万分之一,室温下的参考电压输出为1.22V,低频下的电源抑制比超过60dB,3.3V电源电压下的功耗约为3.6μW。电阻修调电路的引入,使该带隙基准在各个工艺角下都能输出稳定的基准电压,克服了工艺偏差对该基准电压造成的影响。该基准电压结构适用于低功耗集成电路设计中。

[1]GONG Xiao-feng,LIU Min-jie,ZHOU Bin,et al. A novel wide temperature range bandgap reference[C]∥Circuits and Systems (MWSCAS), 2012 IEEE 55th International Midwest Symposium on. IEEE, 2012: 506-509.

[2]CHUN H, SKAFIDAS S. A low-power, small-area and programmable bandgap reference[C]∥Circuits and Systems (MWSCAS), 2012 IEEE 55th International Midwest Symposium on. IEEE, 2012: 510-513.

[3]LEUNG K N, MOK P K T,LEUNG C Y.A 2-V 23-μA 5.3-ppm/℃ curvature-compensated CMOS bandgap voltage reference[J].IEEE Journal of Solid-State Circuits,2003,38(3):561-564.

[4]王晓艳,张志勇,卢照敢,等.一种Brokaw带隙电压基准的分析与设计[J].西北大学学报(自然科学版),2007,37(6):991-995.

[5]赵磊,杨银堂,朱樟明,等.一种高性能BiCMOS差分参考电压源[J].西安电子科技大学学报(自然科学版),2012,39 (4):11-16.

[6]杜永乾,靳钊,李小明,等.一种新型无源UHF RFID带隙基准电路[J].西安电子科技大学学报(自然科学版),2013,40 (2):148-152.

[7]GUANG Ge,CHENG Zhang,HOOGZAAD G.A single-trim CMOS bandgap reference with a naccuracy of 0.15% from 40℃ to 125℃[J].IEEE Journal of Solid-State Circuits,2011,46(11): 2693-2701.

[8]ADIMULAM M K,MOVVA K K. A low power CMOS current mode bandgap reference circuit with low temperature coefficient of output voltage [C]∥Microelectronics and Electronics (PrimeAsia), 2012 Asia Pacific Conference on Postgraduate Research in. IEEE, 2012: 144-149.

[9]TIMM S,WICKMANN A.A trimmable precision bandgap voltage reference on 180 nm CMOS [C]∥Semiconductor Conference Dresden-Grenoble (ISCDG), 2013 International. IEEE, 2013: 1-4.

[10] GRAY P R, HURST P,MEYER R G, et al.Analysis and design of analog integrated circuits (4th Edition) [M].New York:Wiley, 2001.

[11] TAN Xiao-yun,LIANG Chen,SHI Min.A Low Temperature Coefficient 4th-Order Curvature-Compensated CMOS Bandgap Reference [C]∥Optoelectronics and Microelectronics Technology (AISOMT), 2011 Academic International Symposium on. IEEE, 2011: 251-254.

[12] LEE E K F.A low voltage CMOS bandgap reference without using an opamp [C]∥Circuits and Systems, 2009. ISCAS 2009. IEEE International Symposium on. IEEE, 2009: 2533-2536.

[13] MARTINEZ-NIETO A,SANZ-PASCUAL M T,ROSALES-QUINTERO P,et al. A bandgap voltage reference in 0.18μm CMOS technology [C]∥Circuits and Systems (MWSCAS), 2013 IEEE 56th International Midwest Symposium on. IEEE, 2013: 97-100.

[14] HAMOUDA A,ARNOLD R,MANCK O,et al.7.72 ppm/°C, ultralow power, high PSRR CMOS bandgap reference voltage[C]∥Very Large Scale Integration (VLSI-SoC), 2013 IFIP/IEEE 21st International Conference on. IEEE, 2013: 364-367.

(编辑李静,曹大刚)

A lowpower voltage reference with isolated resistor-trimming

YANG Zheng

(School of Microelectronics, Xidian University, Xi′an 710071, China)

A novel low power low temperature-coefficient bandgap voltage reference is presented in this paper. The main advantage of the proposed design is that, without an opamp, the main current consumption of the circuit is that for generating the reference voltage. As a result, the proposed bandgap reference can achieve low power comsumption. A resistor trimming circuit is introduced to overcome the variation of the resistance caused by the floating analog integrated circuit design process, so that the reference voltage at each process corner can achieve a good voltage output. Meanwhile, the isolated resistor trimming improves the noise effects caused by the traditional direct fuse trimming. Finally the simulation results based on 0.18μm CMOS process indicate that the temperature changes 1℃, the voltage variation is one over one hundred thousand during the full temperature range (-40℃~100℃). The bandgap circuit outputs 1.22V in the typical operation condition. And the power is only 3.6 μW. The proposed voltage

tructure can be applied to the design of low-power ICs.

voltage reference; analog integrated circuits; low power; trimming; start-up circuit

2015-04-16

国家自然科学基金资助项目(61234002,61322405,61306044,61376033);国家863基金资助项目(2012AA012302,2013AA014103)

杨正,女,河北涿州人,从事低压低功耗模拟电路设计研究。

TN402

ADOI:10.16152/j.cnki.xdxbzr.2016-01-007