基于PCIE的高速图像采集卡设计

龚晓华

摘 要:本文基于Xilinx Artix-7系列FPGA的PCIe接口设计了一套高速图像采集卡方案,通过面向WinDriver的 PCIe设备驱动程序开发,在Windows7系统中实现了PC机对采集卡的读、写、DMA操作和中断处理。经测试,PCIe x1@5GHz接口单向峰值传输速率达463.14MB/s,可以满足实际应用中的高性能和可靠性要求。

关键词:PCIE;FPGA ; WinDriver 图像采集

随着图像处理走向高清化、智能化,人们对设备间数据传输速率的要求越来越高,PCIe作为计算机和外围设备间数据交互的主流接口,已被广泛的应用于图像采集卡设计中。目前,实现PCIe接口有两种方法:使用FPGA内置的PCIe专用IP,使用PCIe桥接芯片。由于FPGA应用更加灵活、成本更低,本文基于FPGA设计高速图像采集卡。

一、图像采集卡设计

(一) PCIe图像采集卡设计

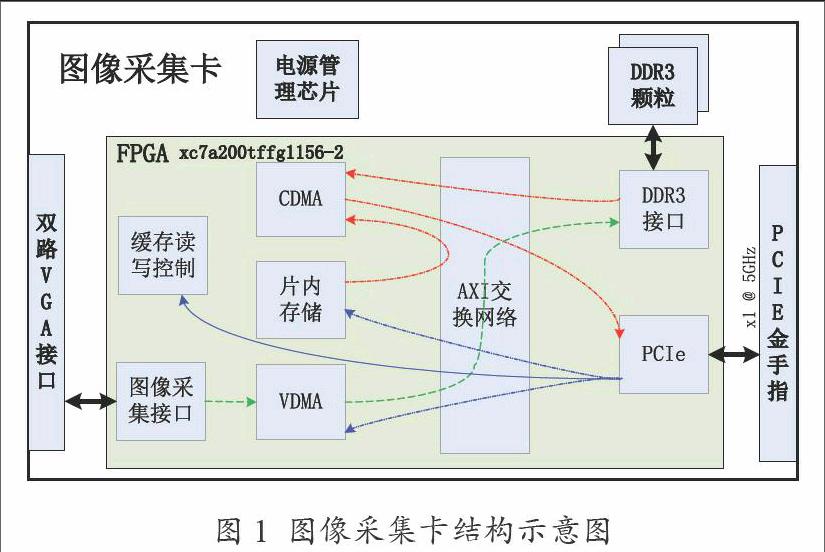

如图1所示,图像采集卡基于Xilinx公司的Artix-7系列xc7a200tffg1156-2 FPGA芯片,该型FPGA内集成有PCIe硬核,用于实现采集卡和PC间的数据交换,本设计使用x1模式,传输速率5Gbps,理论带宽500MB/s。围绕FPGA构建常用外设,如双路差分VGA接口和DDR3存储,用于图像采集和数据存储;电源管理模块实时检测采集卡上的关键电压信号。

(二)图像采集卡工作原理

数据流方面,如图1所示,图像数据通过差分VGA接口进入FPGA内部,接口适配模块实现VGA时序向AXI-Stream[1]时序的转化,VDMA模块将图像流缓存到DDR3中的循环缓冲中,并以中断方式向缓存读写控制模块报告写入情况;当缓存读写控制模块判定循环缓冲中有剩余数据时,通知CDMA模块发起PCIe写DMA,将DDR3中数据通过PCIE模块发送到PC缓存,再以消息方式告知PC DMA发送完毕,PC机最终向图像流数据缓存写特定数据报告循环缓冲读取情况。

控制流方面,PC需通过PCIe写VDMA和CDMA模块以分配板载DDR循环缓冲地址,并将PC端的缓存地址写入片内存储器中以配置CDMA模块的链式DMA功能。

二、软硬件程序开发

(一) FPGA硬件程序开发

如图1所示,FPGA中各组件通过AXI协议互联,构成了一个小型SoC网络[2]。利用vivado工具提供的Block Design设计流程,添加各标准IP,按实际访存需求进行连线,并分配全局地址。其中关键的PCIe模块参数配置如下:Endport device, Lane Width x1, Link Speed 5.0GT/s, PCIE:BAR0 Memory 64KB Translation DDR_ADDR(PC对片上DDR访问),PCIE:BAR1 Memory 64KB Translation C/VDMA_ADDR(PC对DMA控制器访问),AXI:BARS:用1个且动态可配,AXI:System:32位地址128位数据。

(二) PC端PCIe驱动开发

PCIe驱动开发使用Jungo公司的WinDriver工具。首先在图形界面下打开待测PCIe设备,并对FPGA典型地址进行读写测试,最终生成驱动代码。其次提取xxx_bsp.h和xxx_lib.c等核心文件,构建PCIe驱动动态链接库,实现DeviceFindAndOpen、DeviceClose、WDC_DMAContigBufLock、WDC_DMABufUnlock、ReadReg32、WriteReg32等基本函数。最终,按采集卡工作原理编写应用程序。

三、验证结果

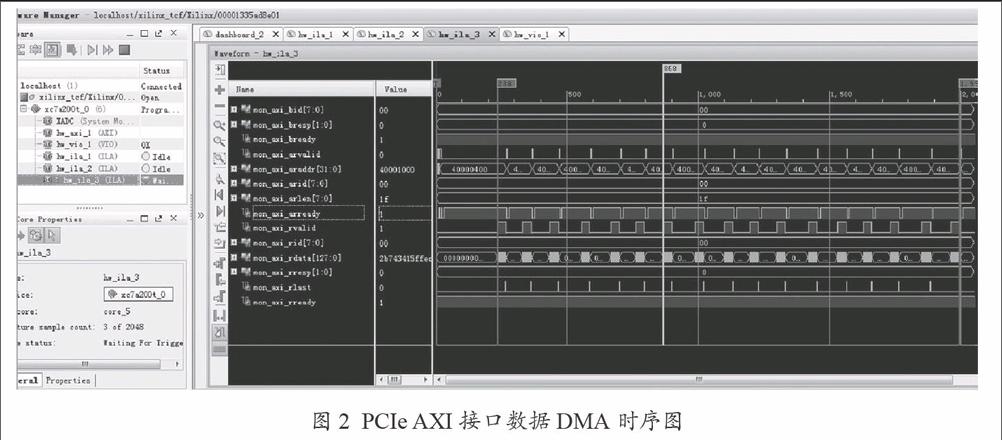

在该设计中,我们设计了基于PCIe接口的高速图像采集卡,构建了FPGA片上SoC系统,通过PC端PCIe驱动的开发,实现了完整的图像数据采集功能,在x1、5GHz传输速率条件下实现了PCIe接口实际传输带宽463.14MB/s,满足实际图像采集要求,系统运行是稳定可靠的。图2为Vivado环境下Hardware Manager工具提取的PCIe IP AXI接口数据传输时序图。

四、结论

本文设计了一款基于FPGA的PCIe高速图像采集卡,并通过FPGA实测,系统稳定可靠运行,满足实际系统应用需求。

参考文献:

[1] AXI Video Direct Memory Access v6.2. Xilinx, 2015.

[2] PCI Express Endpoint-DMA Initiator Subsystem. Xilinx, 2013.