基于嵌入式系统的JTAG驱动电路实现方法

周乐+孙大成

摘要:该文提供了一种基于嵌入式系统的JTAG驱动电路的实现方法,包括主控制单元由一个嵌入式处理器模块来完成,处理调试计算机从接口发送过来的数据包,该数据包通过处理器模块解析成一组基本的操作序列,这组操作序列进而进入下一级驱动器模块,产生的JTAG数据码流发送给目标数字信号处理器;同时将目标数字信号处理器返回的JTAG信号解码,提交给处理器模块返回上位机。

关键词:JTAG驱动电路;嵌入式处理器;驱动器

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)25-0235-04

Abstract: In this paper, we present a method which implements jtag drive circuit based on imbedded system. The main control unit achieves function by a imbedded processor,which processes data packs coming from debugging computer. The data pack is translated a group of operator by processor, then the group of operator are sent to the next drive module, resulting in jtag code to target DSP. Simultaneously, corresponding jtag code come back from target DSP, and send to host by the imbedded processor.

Key words: JTAG drive circuit;imbedded system;drive module

1 引言

目前大多数的通用数字信号处理器都采用JTAG(Joint Test Action Group,联合测试工作组)边界扫描技术作为其调试手段,而在该处理器的外侧需要一个驱动模块,用来作为调试计算机和目标处理器的桥接。该桥接电路主要对从调试计算机发送来的数据进行解析、格式转换、数据同步、数据卸载等,同时还要完成编码和解码等功能。

而很多的JTAG驱动电路主要通过单片机等CPU单纯地通过软件来控制,而JTAG驱动电路中一些编解码模块以及状态切换操作等模块用专用硬件电路来实现效率更高;还有一些JTAG驱动电路只通过FPGA的硬件逻辑来实现,这样放弃了软件开发的灵活性。以上的这些设计对实现当下功能越来越强大的JTAG调试是一种束缚。

本文涉及一种面向高性能通用数字信号处理器的基于嵌入式系统的JTAG驱动电路的实现方法。是一种基于嵌入式技术开发的电路系统可以同时兼顾软硬件的优势,通过软件开发可以丰富各种面向用户的调试功能,结合相应的硬件模块可以使JTAG驱动电路高速化、模块化。

2 系统概述

本文所要解决的技术问题在于提供一种既能满足IEEE1194.1标准,又能够通过软硬件协同处理提高JTAG驱动电路工作效率的基于嵌入式系统的JTAG驱动电路的实现方法。

本文采用以下技术方案解决上述技术问题:一种基于嵌入式系统的JTAG驱动电路的实现方法,包括以下步骤:主控制单元由一个嵌入式处理器模块来完成,处理器模块完成数据的接收、处理以及发出控制信息,处理器模块是个可编程的CPU,处理调试计算机从接口发送过来的数据包,该数据包通过处理器模块解析成一组基本的、目标数字信号处理器能够识别的操作序列,这组操作序列进而进入下一级驱动器模块,驱动器模块在处理器模块的控制下,实现各种调试操作的JTAG数据码流发送给目标数字信号处理器;同时将目标数字信号处理器返回的JTAG信号解码,提交给处理器模块,该驱动器模块同时完成了数据的串/并、并/串转换。

3 层次化设计

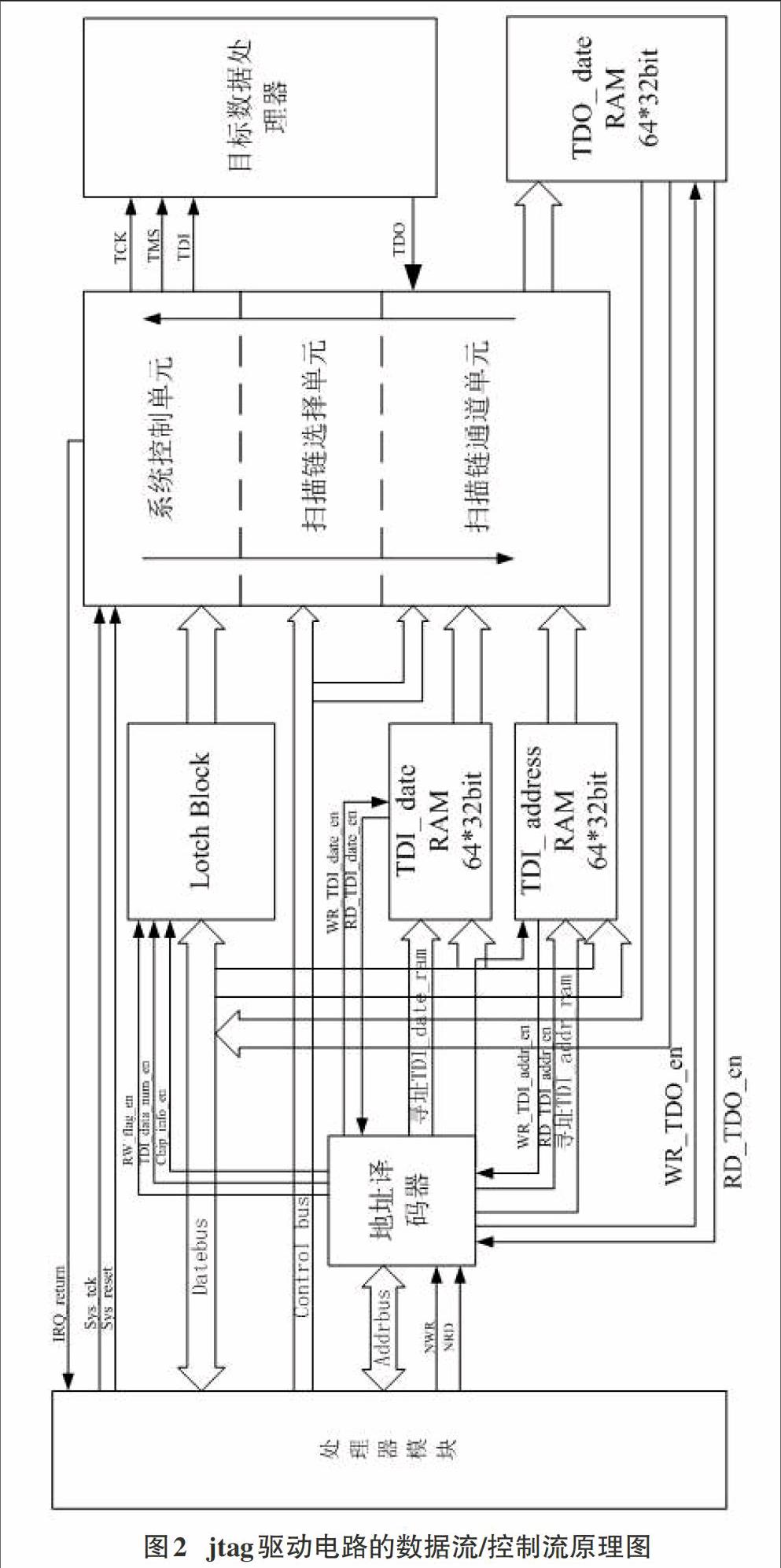

图2 是jtag驱动电路的数据流/控制流原理图。本设计是基于嵌入式系统的JTAG驱动电路,包括处理器模块(Processor)、地址译码器、锁存模块(Latch Block)、存储器(TDI_data RAM、TDI_address RAM、TDO_data RAM)、驱动器模块。

3.1 控制器模块

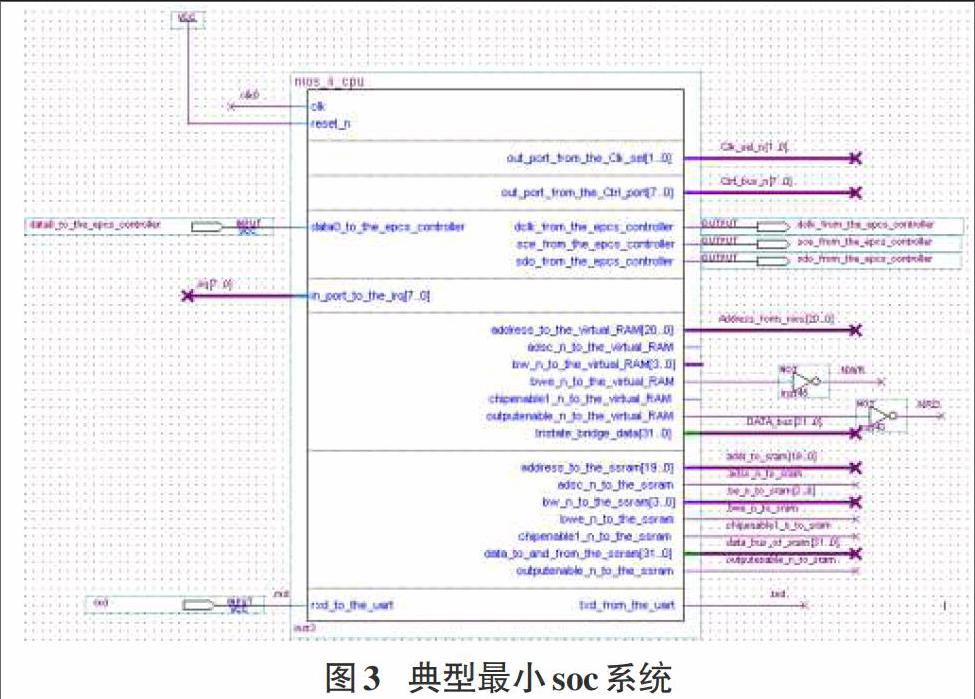

在该系统中,处理器模块是作为控制器,在该模块中,将内核(cpu core)、通信接口(interface)、闪存(flash)、控制逻辑(control logic)、JTAG接口(jtag)、锁相环(PLL)、计数器(timer)等挂载在本地总线(local bus)上形成一个典型的最小系统。内核(cpu core)起到主控制作用,完成数据的接收、处理以及发出一些控制信息;通信接口(Interface)可以是网口、USB、串口等;闪存(flash)主要存放内核(cpu core)的解析软件;控制逻辑(control logic)主要完成数据的读写使能产生以及控制类参数的配置;锁相环(PLL)主要由外接时钟生成几路系统需要的系统时钟;计数器(timer)主要用于解析软件中需要的计数功能。图3是典型最小soc系统。

3.2 锁存器和地址译码器

锁存模块(Latch Block)通过数据总线与处理器模块互联,地址译码器通过地址总线与处理器模块互联,并且与3块RAM:TDI_data RAM、TDI_address RAM、TDO_data RAM互联。

如图2所示,处理器模块主要是协议栈处理和控制信号的产生;地址译码器主要是对处理器模块地址总线进行译码,译码后的bit位再与上一级写请求/读请求(NWR/NRD),生成下一级模块的使能信号。参考图4的处理器模块地址总线定义说明:总线上的低5位用于对两块TDI RAM(测试数据输入随机存储器)的寻址:TDI_data RAM和TDI_address RAM;总线上的[7:5]用于3块RAM的读写使能信号的产生:TDI_data RAM、TDI_address RAM、TDO_data RAM;总线上的第8位为JTAG电路的复位信号;总线上的第9位为空;总线上的第10位为读写使能信号位,RW_flag_en有效时,锁存模块(Latch Block)会通过数据总线将存放到TDI RAM中每一个数据的读写信号发送给驱动器模块,表示每个数据对是读还是写;总线上的第11位是数据对数使能信号位,TDI_num_enable有效时,锁存模块(Latch Block)会通过数据总线将TDI RAM中有效的数据对数导入驱动器模块中;总线上的第12位是芯片信息导入使能位,当Chip_info_load_en有效时,锁存模块(Latch Block)会通过数据总线将目标芯片的个数、选中的目标芯片编号、链信息导入驱动器模块中。

3.3 JTAG驱动器模块

JTAG驱动器模块是一个纯硬件逻辑,驱动器模块是专门为目标数字信号处理器(Target DSP)的JTAG通信机制定制的codec硬件逻辑,它在处理器模块最小系统的控制下,实现各种调试操作的JTAG数据流编码(主要是TCK、TDI、TMS信号的产生),发送给目标数字信号处理器;同时将目标数字信号处理器返回的JTAG信号TDO解码,提交给处理器模块最小系统进行相关处理。IEEE-1149.1协议规定了驱动器模块的5个串行的JTAG信号。4个输入信号(相对于目标数字信号处理器):时钟信号(TCK)、数据信号(TDI)、控制信号(TMS)、复位信号(TRST_n),1个输出信号:数据返回信号(TDO)。除了复位信号外的3个输入信号必须满足一定的关系才能实现对目标数字信号处理器的各种操作,此外,返回信号和TMS之间也有对应关系。为了提高JTAG驱动电路的工作效率,专门用硬件逻辑来实现对3个输入信号的编码和1个输出信号的解码。根据在线调试逻辑的具体特点,扫描链的切换操作会频繁使用,而且操作由固定的基本操作序列构成,因此将扫描链的切换操作固化在驱动器模块中,由硬件高速执行,软件只需要提供相应的参数,大大简化了软件的负担。

驱动器模块由以下三部分组成:系统控制单元(System Control)、扫描链选择单元(JTAG_chain_sel)、扫描链通道单元(JTAG_Channel),系统控制单元与处理器模块发出的控制信号互联,包括时钟模块的选择、复位信号的输入等;扫描链选择单元与锁存模块(Latch Block)、处理器模块发出的控制信号互联,发出包括目标芯片的个数、选中的目标芯片编号、链编号信息、链选择使能、使能信号的关闭,而中断返回由处理器模块来响应;扫描链通道单元与RAM模块、锁存模块(Latch Block)、处理器模块发出的控制信号互联,完成数据流的通路、标示读写信号、一次性写入相应存储器的数据个数、通路的使能、通路的关闭,而中断返回由处理器模块来响应。参见表1驱动器模块源目的信号说明。

4 jtag驱动电路的软硬件协同工作

该驱动电路是实现的硬件基础,还需要嵌入式软件配合一起实现完整的功能,其工作原理如图5。

其软硬件工作流程为:

调试计算机通知通信层(Communication Layer)用户所选择的命令;通信层对该操作做出响应,注:通信层是IDE环境中的一个软件模块。根据调试操作类型(Reset、Run、StepCycle、StepInst等)做出响应,生成并行数据流,按照通信协议打包发送给驱动器模块;

调试计算机通过通信接口发送过来的一个通信包(高级调试命令)被JTAG驱动电路的cpu core解析成一组基本的、目标数据处理器可以识别的操作序列,这组操作序列进而进入驱动器模块,驱动器模块对数据进行编码并在TCK的驱动下向目标数据处理器芯片的在线调试逻辑发送TMS、TDI、TCK;

在TCK的驱动下,目标数据处理器完成一次指定的操作,并将TDO数据反馈给JTAG驱动电路;

JTAG驱动电路根据JTAG协议将TDO数据进行解码,并对返回的TDO信息进行分析,确定下一步所要进行的操作,如果有必要,则重复执行上述的步骤;解析软件在某些操作序列中会进行轮询以等待目标DSP返回指定的信息,否则不会执行下一步。

当用户命令的所有分解步骤都执行完毕之后,JTAG驱动电路会通过cpu core将所有的TDO返回信息打包发送给通信层;通信层接收到TDO应答包,并向IDE发送结束通知;IDE接到来自通信层的结束通知后,读取应答包中的信息,并根据应答包的内容做出进一步的分析、处理与判断;

5 结论

基于嵌入式系统搭建的JTAG驱动电路具有较好的系统稳定性和可靠性,该驱动电路经测试,实际工作速度稳定在50 KB/s左右,具有单步、运行、设置断点、观察点、读写寄存器、存储器、DDR2等功能,获得了用户的一致好评。

参考文献:

[1] Institute of Electrical and Electronics Engineers.IEEE 1149.1-2001IEEE Standard Test Access Port and Boundary-Scan Architecture[S].2001.

[2] 田泽.嵌入式系统开发与应用实验教程[M].北京:北京航空航天大学出版社,2004.