基于自研AFDX网络端系统芯片的模块设计与实现*

夏大鹏,辛江波,潘 彬,解亚龙

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

基于自研AFDX网络端系统芯片的模块设计与实现*

夏大鹏1,2,辛江波3,潘彬3,解亚龙3

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

国外对AFDX网络核心产品的垄断严重制约了我国AFDX网络技术的发展,难以建立完整的AFDX网络产品体系。提出了一种基于自研AFDX网络端系统芯片的模块设计方法,从软硬件设计角度阐述模块的设计与实现过程。该模块集成端系统SoC芯片,具有PMC、PCI和CPCI三类主机接口,完成AFDX网络数据通信功能。目前已成功应用于型号工程,其功耗低,功能、性能稳定可靠,国产化率高,具有较高的成熟度,打破了国外产品垄断,实现了AFDX端系统模块的自主保障、自主可控。

AFDX;端系统芯片;模块设计;PMC;PCI;CPCI

0 引言

目前,国内外研制的AFDX网络端系统模块基本是依靠FPGA逻辑与软件相结合的方式来实现协议解析和数据收发功能。由于基于FPGA实现的AFDX网络端系统产品功耗、体积以及可靠性难以满足恶劣机载环境应用需求,本文介绍了基于AFDX网络端系统芯片实现的模块设计,解决了制约AFDX网络发展的瓶颈,对我国航空电子系统的发展及自主研究具有重要的意义[1]。

基于自研AFDX网络端系统芯片的模块是一款集成HKS664ES型端系统 SoC芯片的网络传输通信设备,其端系统芯片内部集成ARM922T处理器,利用该芯片上的高性能处理器实现传输层及网络层的协议处理,从而实现AFDX网络数据帧的收发。该模块的成功研制在国内尚属首次,打破了国外在AFDX网络端系统传输卡方面的技术封锁和产品垄断,并拥有自主知识产权,解决了国内AFDX网络产品受制于人的困境,为AFDX网络在国内的应用及发展做出了重要贡献。

1 模块设计

1.1功能

基于自研AFDX网络端系统芯片的模块具有高度的灵活性,通过将高性能的AFDX网络端系统接口与主机处理器连接,实现AFDX网络数据的收发功能。该模块采用双余度的AFDX网络端口,完全符合ARINC664协议,发送支持 128个 VL,接收支持 4 096个 VL,具有流量规整、接收帧过滤等功能[2-3],并提供了 3种类型的接口:PMC接口、PCI接口和CPCI接口[4]。

本文提出的基于端系统芯片的模块设计方案采用软硬件协同设计方法,以工程化、模块化、通用化的标准进行硬件模块设计,同时以层次化结构设计,简化AFDX端系统传输卡软件体系架构,提高软件可移植性和重用性设计,使系统具有良好的维护性、通用性。

1.2硬件设计与实现

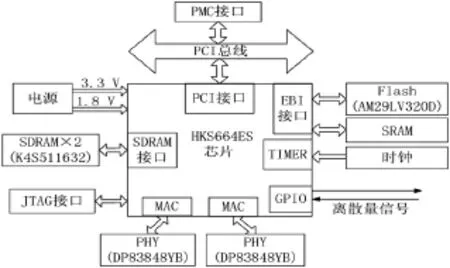

基于自研AFDX网络端系统芯片的模块架构设计灵活,通过更换连接器接口满足不同的功能需求,从而实现了一种多功能、低成本的模块设计。本模块设计原理图如图1所示,核心芯片采用 HKS664ES型芯片,实现数据的收发,外部功能单元包括时钟电路、电源转换电路、复位电路、串行接口电路、主机接口电路等[5]。

图1 模块架构原理图

1.2.1时钟电路

模块工作过程中,外部提供系统时钟、RTC时钟、PCI时钟3个时钟源。系统设计中,基于HKS664ES芯片设计需要提供一个 25MHz外部晶振作为系统时钟,一个2MHz外部晶振作为RTC输入时钟,另外PCI总线时钟需要外部主机提供33MHz输入时钟[6]。

系统集成者需要规定总线时钟振荡器的时钟质量和温度稳定性,即在某些温度下的精确度以及在整个温度范围内此精确度的变化范围。在整个温度范围内,时钟质量应确保总的漂移不超过100 ppm。

1.2.2复位电路

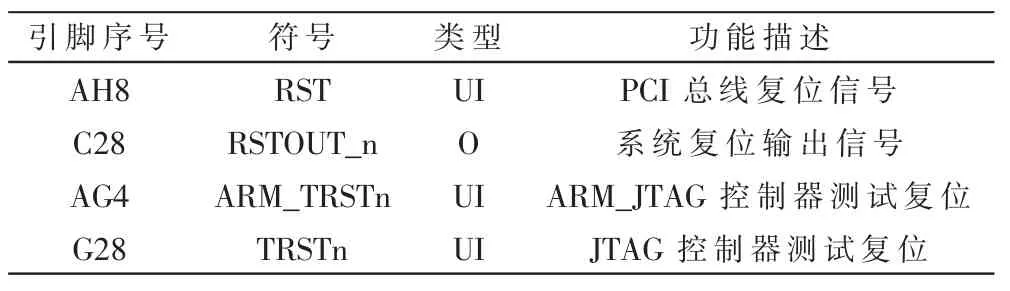

基于自研AFDX网络端系统芯片的模块提供了系统复位、JTAG复位、PCI总线复位,具体接口定义如表1所示。

系统复位信号由外部的复位芯片提供,用于启动或者重新启动主机处理器。

传统的企业生产和发展以大量资源的消耗和环境的破坏为代价,在全球资源日益匮乏和环境污染日益严重的形势下,倡导循环经济已是新时代企业生产方式变革和发展的大势所趋。“三废”的处理历来是限制企业经济效益提高与束缚企业发展的重要因素,因此,在不影响产品收率及质量的前提下,溶剂循环套用不仅可以提高企业的经济效益,而且对企业未来的发展具有举足轻重的作用。

表1 复位号定义

PCI总线接口复位信号,由PCI主机产生,用于复位包括PLL在内的所有ES逻辑。复位信号有效时,ARM922T处理器进入预定的复位状态。

调试口复位由外部调试工具产生,用于复位ARM922T处理器的调试接口[7]。

1.2.3主机接口电路

模块的主机接口符合 32位、33MHz PCI总线规范,兼容 PCI2.2版本规定,PCI总线接口电平 3.3 V。支持SLAVE和MASTER两种总线控制模式,SLAVE模式用于数据传输的管理接口,供宿主机直接访问,用来配置和查询端系统通信端口信息;MASTER模式用于数据搬运,根据通信端口信息,直接启动DMA控制器,在宿主机内存和模块内部片上存储器之间进行数据交换[8]。

1.3软件设计与实现

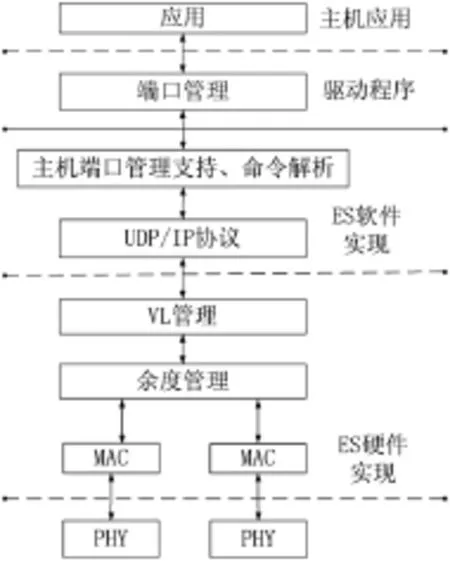

航空电子通信系统划分成五层协议:应用层、传输层、网络层、数据链路层和物理层。模块通信软件遵循航空电子通信系统软件层次结构划分,如图2,其中,物理层与数据链路层由接口模块上的硬件实现;传输层由固化于接口模块上的传输软件实现,主要负责接口模块的初始化、发送以及接收;应用软件和驱动软件驻留在主机中,其中驱动层主要实现应用层和传输层之间数据信息的传递,并为上层应用软件提供API接口函数;应用软件与特定的子系统有关,通过调用MBI驱动软件实现子系统功能要求。

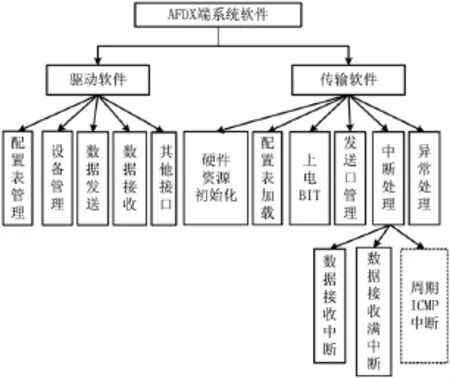

模块软件分为两个相对比较独立的部分:传输软件和驱动软件。传输软件运行在模块上,负责实现应用层以下的数据传输协议栈的处理,传输软件符合ARINC664 part7规范中定义的端系统协议层,实现UDP/IP协议,配合主机驱动进行端口管理和调度;驱动软件运行主机上,为应用程序提供标准的API接口,用户可根据提供的配置信息完成配置表的加载、端口创建,实现模块与主机应用软件之间的接口控制与数据传输,软件结构功能划分如图3所示。

图2 软件层次结构图

图3 软件架构图

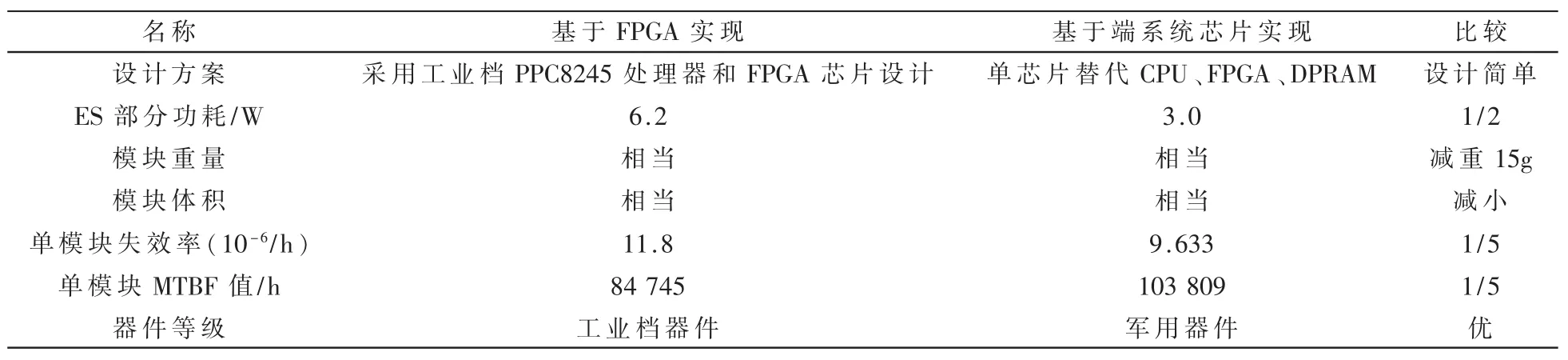

1.4技术优势

目前,国内外研制的AFDX网络端系统模块主要有两种方式:一种是基于FPGA实现的AFDX网络端系统模块,另外一种是基于自研AFDX网络端系统芯片的模块。前者在功耗、体积以及可靠性方面难以满足恶劣机载环境应用需求;后者具有功耗低、体积小、可靠性高等优势,主要对比如表2所示。

该模块采用的核心协议处理芯片是国内首款完全具有自主知识产权的核心AFDX网络端系统芯片,作为通过军用电子元器件B级鉴定的自研军用核心关键元器件,成熟度高,具有完全自主知识产权,符合国家“元器件国产化率”的要求。

表2 技术对比

2 模块验证

截止目前,基于自研AFDX网络端系统芯片的模块已通过摸底试验、板级测试、德国 AIM公司、TechSat公司AFDX网络协议符合性测试,充分验证后,表明基于自研AFDX网络端系统芯片的模块满足功能要求,并在性能、功耗、重量、成本、温度范围上具有显著优势,且满足国产化要求。

基于HKS664ES端系统芯片的模块已经在某型号任务机上使用,试用过程中经历了C阶段、S阶段的所有验证,设计、检验全部按照型号任务要求进行设计、实验、评审和质量管控,芯片配套软件严格按照GJB5000A三级要求研制。

3 结论

本文提出的基于自研AFDX网络端系统芯片的模块已经成功应用于某型号任务机,并随整机完成了首飞。经过充分的验证与广泛的应用,该模块被一致认为是一款满足AFDX网络协议、集成度高、安全可靠的端系统模块。该模块的成功研制打破了国外在AFDX网络端系统的产品垄断,对我国研发具有自主知识产权的AFDX网络具有重要意义。

[1]刘芸,王红春.AFDX端系统协议软件设计与实现研究[J].电光与控制,2012,19(11):71-76.

[2]杨峰,田泽.基于USB接口的AFDX网络TAP卡设计与实现[J].测控技术,2013,32(5):77-81.

[3]王治,田泽.一种高性能AFDX监控卡的实现技术研究[J].计算机技术与发展,2010,20(8):217-220.

[4]赵永库.新一代航空电子总线系统结构研究[J].航空计算技术,2005,35(1):99-103.

[5]刘志武,白杨.AFDX网络端系统数据接收方法研究与实现[J].微型机与应用,2013,32(21):48-54.

[6]赵永库,李贞.AFDX网络协议研究[J].计算机测量与控制,2012,20(1):8-10.

[7]张志,翟正军.基于FPGA的AFDX端系统协议芯片的设计与实现[J].计算机测量与控制,2010,18(2):422-425.

[8]张荣华,田泽.AFDX网络端系统芯片架构的研究与设计[J].计算机技术与发展,2011,21(8):165-172.

The design and implementation of the module based on AFDX network end system chip

Xia Dapeng1,2,Xin Jiangbo3,Pan Bin3,Xie Yalong3

(1.AVIC Computing Technique Research Institute,Xi′an 710068,China;2.Aviation Key Laboratory of Science and Technology on Integrated Circuit and Micro-System Design,Xi′an 710068,China;3.Xi′an Xiangteng Microelectronics Technology CO.,LTD,Xi′an 710068,China)

Because of monopolizing AFDX network core products,which seriously restricts the internal development of AFDX network technology.At the same time,the establishment of AFDX network product system integrity is a laborious effort.This paper provides the method of the module design of AFDX network end system chip.The end system module′s design and implementation process are based on combining of hardware and software.This module is embedded with end system SoC chip and provides PMC, PCI and CPCI host interface that it implements the AFDX network data communications.This product has been successfully used in the model project.It has many advantages,such as low power consumption,stable and reliable function,high domestic rate and high maturity.It breaks the monopoly of foreign products and realizes autonomous protection and autonomous control of AFDX network end system module.

AFDX;end system chips;module design;PMC;PCI;CPCI

V243.1

A

10.16157/j.issn.0258-7998.2016.04.004

航空科学基金(2015ZC51036);中国航空工业集团公司创新基金(2010BD63111)

(2016-02-26)

夏大鹏(1981-),男,硕士,工程师,主要研究方向:嵌入式软件开发。

辛江波(1989-),男,本科,主要研究方向:嵌入式软件开发与测试。

潘彬(1986-),男,本科,助理工程师,主要研究方向:集成电路设计及验证。

解亚龙(1985-),男,本科,助理工程师,主要研究方向:航空集成电路硬件设计与验证。

中文引用格式:夏大鹏,辛江波,潘彬,等.基于自研 AFDX网络端系统芯片的模块设计与实现[J].电子技术应用,2016,42 (4):15-17.

英文引用格式:Xia Dapeng,Xin Jiangbo,Pan Bin,et al.The design and implementation of the module based on AFDX network end system chip[J].Application of Electronic Technique,2016,42(4):15-17.