TD-LTE多带宽数字下变频设计与FPGA实现*

田增山,李 路

(重庆邮电大学 移动通信技术重庆市重点实验室,重庆 400065)

TD-LTE多带宽数字下变频设计与FPGA实现*

田增山,李 路**

(重庆邮电大学 移动通信技术重庆市重点实验室,重庆 400065)

分时长期演进(TD-LTE)系统为了满足各种环境的需要,支持6种不同的带宽和基带速率。为了满足TD-LTE系统多带宽和多速率的要求,设计了一种兼容TD-LTE多带宽和多速率的多带宽数字下变频方案。方案中采用了时分复用技术、抽取滤波的合理搭配和高性能滤波器实现了资源优化和输出信号的高信噪比。此外,对数字混频器和抗混叠滤波器进行改进,设计出了基于坐标旋转数字计算法(CORDIC)的流水线型混频器和高速并行可配置滤波器。软件仿真和硬件测试证明了TD-LTE多带宽数字下变频的正确性,且具有灵活性、高性能和低资源消耗的特点以及较高的工程实用价值。

分时长期演进系统;数字下变频;多带宽;数字混频器;抗混叠滤波器;现场可编程门阵列

1 引 言

随着无线通信技术的迅速发展,如今时分长期演进(Time Division-Long Term Evolution,TD-LTE)技术在全球范围内引领了一波4G的潮流,许多地区已经部署了TD-LTE系统,学术界已经放眼5G标准的制定[1]。TD-LTE采用了正交频分复用和多输入多输出为物理层关键技术,使得系统具有更高的传输速率和支持高速移动终端等优势[2-3];采用了多带宽和多速率的技术,从而适应不同的环境需求。数字下变频技术是TD-LTE系统接收机的核心模块,研究数字下变频技术有着非常重要的意义和工程实用价值。

目前,主流的数字下变频方案主要分为单模数字下变频和多模融合数字下变频。文献[4]阐述了一种常用的单模数字下变频方案,主要的模块包括数字混频器、滤波器和抽取等,设计优点是分级处理可以降低滤波器的阶数。该方案可以适用大部分单模系统,但不适用多模系统,原因是设计难度大和消耗资源多。文献[5]通过对单模数字下变频方案进行改进,提出了多模融合的数字下变频方案,通过灵活的配置实现了多模的融合与切换。为了满足各种环境的需要,TD-LTE系统支持6种不同的带宽和基带速率[6],TD-LTE数字下变频系统需要兼容6种不同的带宽和基带速率。目前的数字下变频方案都需要消耗太多的硬件资源才能满足多带宽和多速率的需求,并且设计复杂不适用于工程。

根据TD-LTE系统的特殊需求,本文设计了一种支持多带宽的数字下变频方案,巧妙地利用了信号带宽间的关系,通过灵活的开关选择与配置可以实现TD-LTE 6种不同带宽和基带速率的灵活切换,通过时分复用技术、抽取滤波的合理搭配和高性能滤波器实现了资源优化和输出信号的高信噪比。本文首先对TD-LTE系统的参数进行分析与设计,在此基础上完成了方案设计与优化,然后对数字混频器和抗混叠滤波器的设计做了改进,最后通过软件仿真和硬件测试,验证了方案的正确性与工程实用价值。

2 系统参数分析与设计

根据文献[4]中下变频的设计原理,我们需要知道TD-LTE系统的中频频率fIF、采样率fs、混频本振f0、降采样倍数。

2.1 中频频率、采样率和混频本振的设计

中频频率fIF要同时兼顾射频和基带的诉求。对射频而言,当中频频率较大时,镜像频率与载频的距离较远,前端容易滤除镜像频率干扰[7]。对基带来说,中频越低越好处理。在通信系统中,标志中频一般有70 MHz、140 MHz以及720 MHz等。综合考虑,中频频率fIF选取为140 MHz。

为了下变频的简单化和A/D采样后频谱不混叠,采样速率要求是基带信号码片速率的整数倍和满足式(1)带通采样定理:

(1)

TD-LTE系统支持最大20MHz带宽,基带速率为30.72Msample/s,fIF为140MHz,根据式(1)以及兼顾芯片的性能和硬件电路布线的难度,采样率频率fs选取为122.88MHz。

模拟中频信号以122.88MHz的频率采样后,得到中心频率为17.12MHz的数字信号,即中频频率与采样率的差。数字混频的目的是将信号搬移至零频,易得混频本振频率f0为17.12MHz。

2.2 降采样倍数

TD-LTE系统支持6种不同的带宽和基带速率,不同的基带速率、带宽以及对应的降采样倍数关系如表1所示[6]。降采样倍数取值范围为4~64,跨度较大,且15 MHz带宽时需要分数倍的降采样,这就要求TD-LTE数字下变频的输出要兼顾6种不同带宽和基带速率输出。

表1 TD-LTE不同带宽和基带速率的降采样倍数

Tab.1 Down sample rate of varying bandwidth and baseband rate in TD-LTE

采样率/MHz基带速率/(Msample·s-1)带宽/MHz降采样倍数插值率抽取率122.8830.7220414122.8823.041516/3316122.8815.3610818122.887.68516116122.883.84332132122.881.921.464164

3 多带宽数字下变频方案设计

3.1 多带宽数字下变频

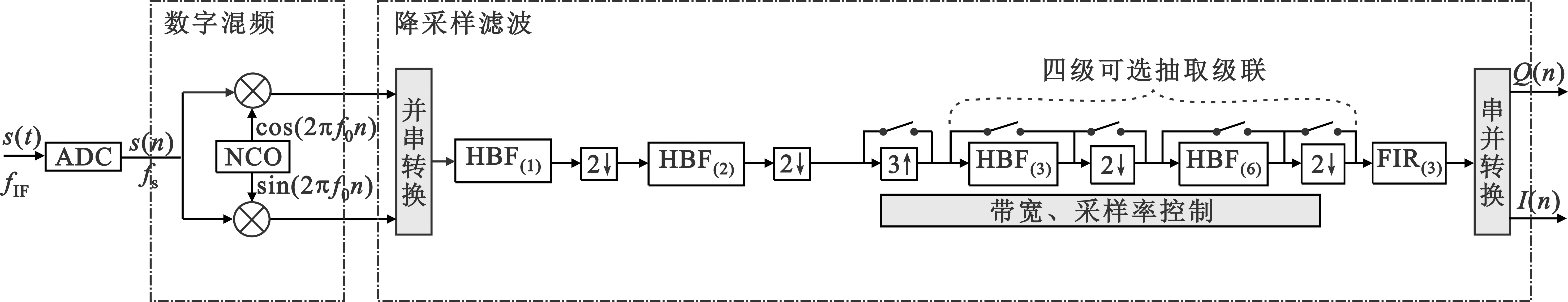

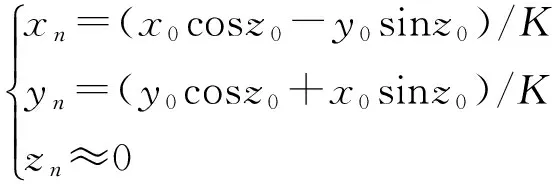

图1为本文设计的TD-LTE多带宽数字下变频架构,其核心模块包括数字混频模块、降采样滤波模块以及控制模块。数字混频模块由数控振荡器与两个乘法器构成,实现信号零中频处理。降采样滤波模块包括四级抽取滤波与一级插值滤波。由于6种带宽下都需要至少4倍的降采样处理,所以前两级抽取滤波均为固定的2倍抽取和20 MHz带宽的HBF滤波器;后面的3倍插值与两级16倍抽取滤波是可选择和参数可配置的FIR滤波器;控制模块通过对插值、抽取和滤波器的灵活选择与配置可以实现6种不同带宽和基带速率的切换。

图1 TD-LTE多带宽数字下变频架构

Fig.1 Architecture of TD-LTE multi-bandwidth digital down converter

本方案的优势:

(1)巧妙地利用了信号带宽间的关系,通过灵活的开关选择与配置可以实现TD-LTE 6种不同带宽和基带速率的灵活切换;

(2)通过3倍的插值以及16倍的抽取巧妙地实现了16/3分数倍的降采样;

(3)在数字下变频输出末端有两个系数可配置高性能滤波器FIR(I3)和FIR(Q3),其过渡带陡峭用于滤除带外噪声,保证了信号输出高信噪比。

3.2 多带宽数字下变频资源优化

图1中方案虽然可以很好地兼容TD-LTE系统,但两级可配置FIR抗混叠滤波器的阶数仍然比较大,且I/Q两路的降采样滤波在结构上是重复的,这都造成了资源的浪费。

如图2所示,对数字下变频方案进行优化:通过并串转换模块将I/Q两路的降采样滤波复用成一路,将减少近一半的资源消耗;将两级可配置FIR抽取滤波换成四级HBF抽取滤波,每级抽取率为2,且抽取滤波同样可配,将大大减少滤波器系数的阶数。以1.4 MHz的带宽下为例,方案一的两个FIR滤波器的总阶数为90,方案二中4个HBF滤波器的总阶数为52,HBF滤波器系数偶数点都为零,实际上仅用了32次乘法。因此,四级可配置的HBF滤波器要比两级可配置的FIR滤波器节省一半以上的资源。

图2 TD-LTE多带宽数字下变频资源优化架构

Fig.2 Optimized architecture of TD-LTE multi-bandwidth digital down converter

综上所述,资源优化后的方案优点是采用时分复用技术和抽取滤波的合理搭配节省了大量硬件资源,缺点是增加了时分复用上的设计难度。考虑工程实现,节约资源的设计将更具有优势。

4 多带宽数字下变频的FPGA实现

由图2可知,多带宽数字下变频主要包括数字混频器、并串与串并转换器、抽取插值模块和抗混叠滤波模块。由于并串与串并转换和抽取插值模块比较简单,下面主要对混频器模块和抗混叠滤波器模块的实现进行详细介绍。

4.1 基于CORDIC的混频器模块设计

混频器由数控振荡器与两个乘法器构成,数控振荡器采用坐标旋转数字计算法(Coordinate Rotation Digital Compute,CORDIC)。

在圆周上,向量旋转可建立关系式[8]:

(2)

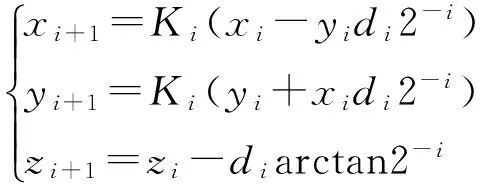

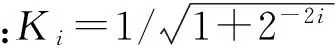

设置旋转角度θ:tanθi=di2-i,旋转角度θ可以通过N次连续旋转一系列预定的角度θi来完成。设zi为旋转角度与目标角度的偏差,当zi<0时,di=1,其他情况下di=-1,di决定下次迭代的角度旋转方向。迭代公式可表示为

(3)

(4)

为了避免在运算中增加校正运算,先去掉模校正因子,Ki的乘积可以直接作为系统处理的增益。式(3)简化后经过N次迭代得

(5)

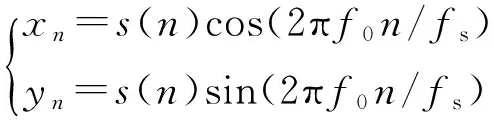

初始值x0=K·s(n),y0=0,z0=2πf0n/fs。式(5)可表示为

(6)

由式(6)可知,通过对CORDIC算法的改进,在设计数控振荡器的同时完成了数字混频的功能,节省了两个乘法器,迭代可以通过相加和移位完成,易于FPGA实现。

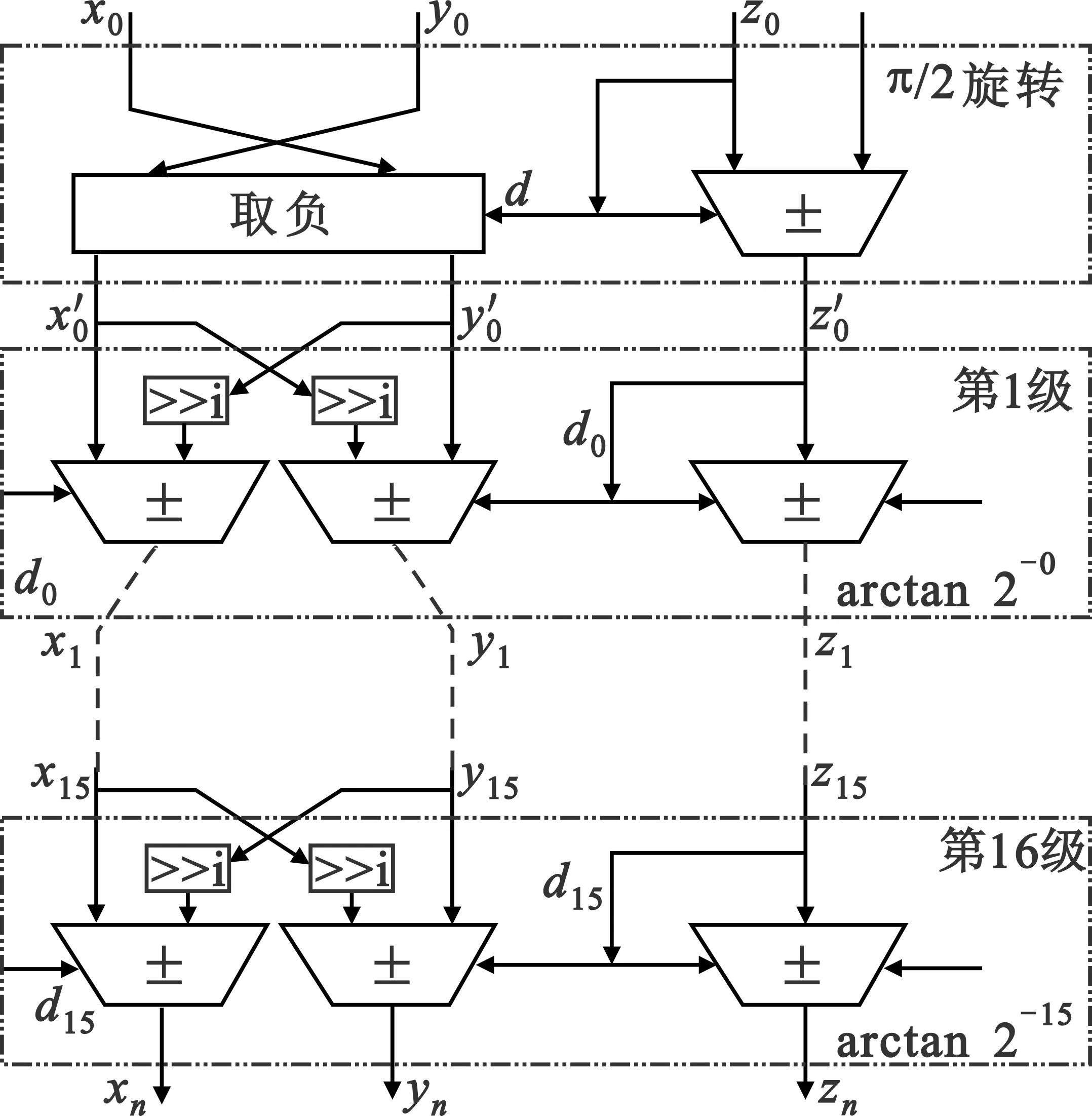

图3为本文设计的流水线型CORDIC混频器的实现结构。第一部分完成了±π/2的相位旋转,因为CORDIC算法旋转的最大角度为θ≈±99.89°,为了让θ的覆盖范围扩展到±π,当输入相位超出±π/2时,需要进行±π/2的初始化旋转。在每一级的迭代中的3个选择加法器分别完成了该级中xi、yi、zi的迭代,加/减控制信号为上一级中的di信号,i位右移实现了乘2-i运算。

图3 16级流水线CORDIC混频器的实现结构

Fig.3Implementationstructureof16-stagepipelinedCORDICmixer

流水线型CORDIC混频器主要解决了查找法需要大量存储资源的问题,在设计数控振荡器的同时完成了数字混频的功能,节省了两个乘法器。流水线型CORDIC实现了一个高速、高精度的混频器,易于FPGA实现。

4.2 抗混叠滤波器的设计

滤波器输入x(n),滤波系数h(n),输出信号y(n),则滤波器的时域卷积为

(7)

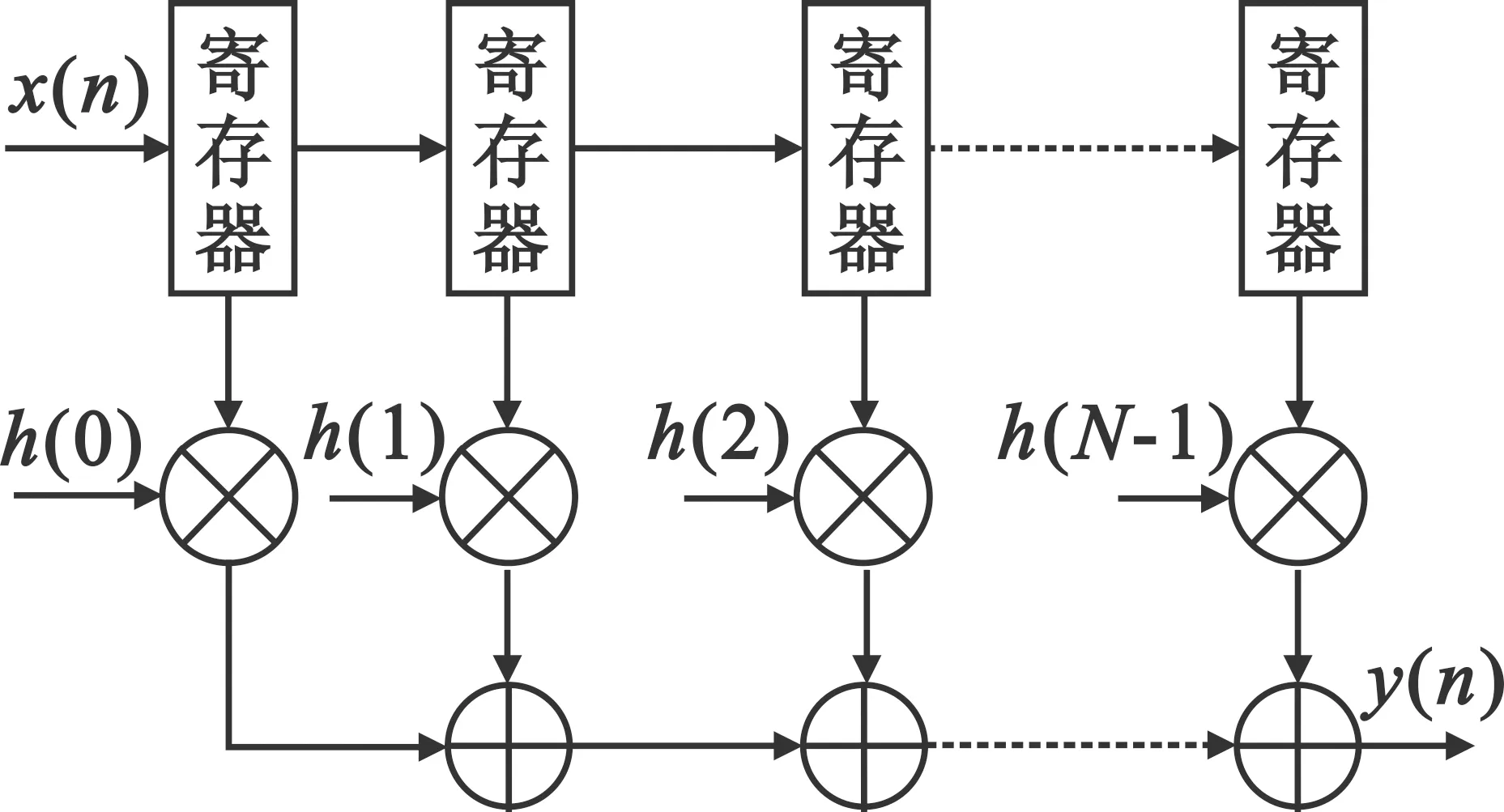

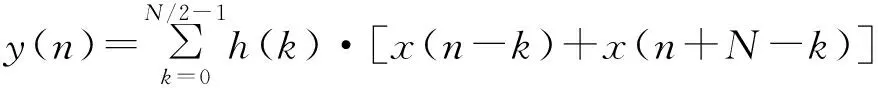

由式(7)可以设计出一般并行的FIR滤波器的实现结构,如图4所示,需要N个移位寄存器、乘法器、存储器和N-1个加法器。

图4 传统的FIR滤波器的实现结构

Fig.4 Implementation structure of the traditional FIR filter

该FIR结构不能满足可配置滤波器的需求并且会消耗太多的乘法器。由于FIR滤波器的滤波系数h(n)是关于中心对称的,式(7)转化为

(8)

由式(8)可知,可以先将对称位置的数据相加,再与抽头系数相乘,可以节约一半的乘法器和存储器。如图5所示为本文设计的可配置并行FIR滤波器实现结构,将对称系数的乘法进行结合,将节约一半的乘法器;通过添加可配置抽头系数模块,可以实现滤波器的灵活配置,改变滤波器的抽头系数,使多个滤波器共享硬件资源。

图5 可配置并行FIR滤波器实现结构

5 软件仿真与硬件测试

5.1 Matlab仿真结果

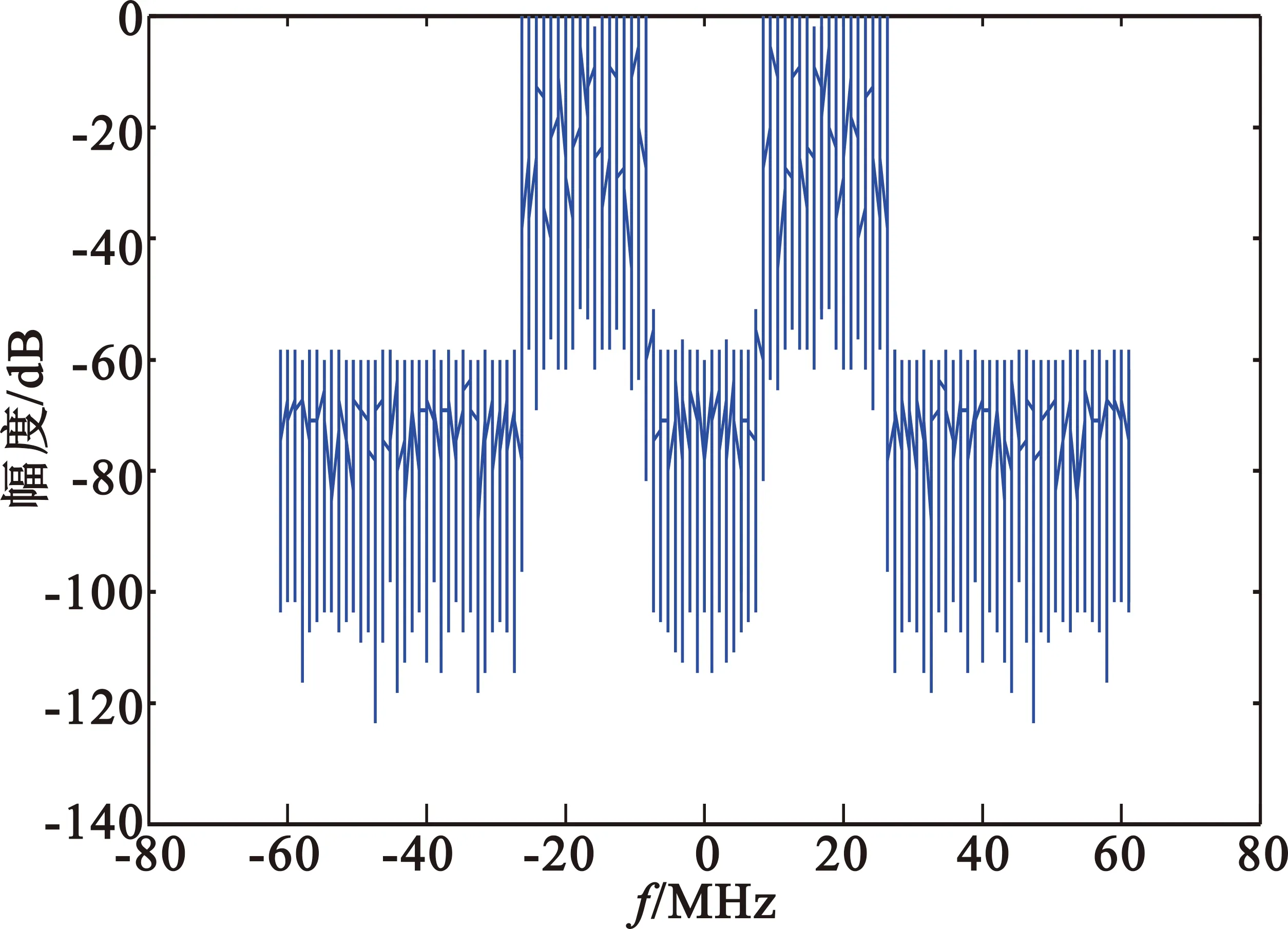

根据上文中的系统参数和下变频的Matlab算法,仿真得到图6所示的下变频功能仿真频谱图和图7所示的基带信号频谱图。图6(a)为输入的中频数据的频谱,中心频率在17.12 MHz;图6(b)为中频信号经过数字混频后被搬移到零频,在高频部分有其镜像频率;图6(c)和图6(d)分别为混频后的信号经过第一级HBF滤波和抽取后的频谱图,第一级HBF对52.44~61.44 MHz的阻带噪声进行了约40 dB的衰减,对该信号进行2倍抽取不会发生镜像混叠,如图6(d)所示。这说明HBF半带滤波器的设计达到了预期要求。

(a)中频数据的频谱图

(b)数字混频后的频谱图

(c)第一级HBF滤波后的频谱图

(d)第一级抽取后的频谱图

Fig.6 Spectrum of digital down conversion function simulation spectrum chart

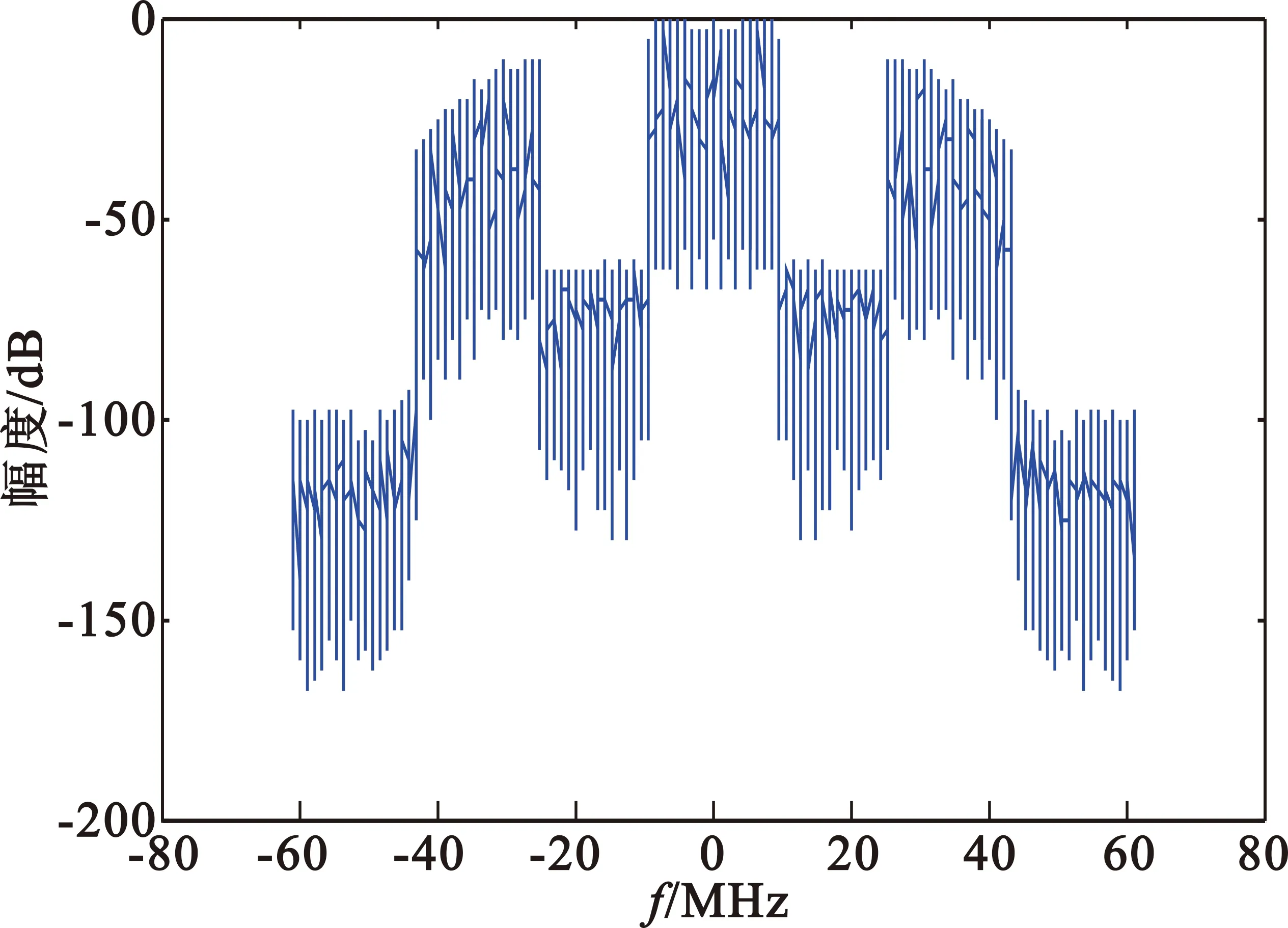

图7 基带信号的仿真频谱图

Fig.7 Spectrum of baseband signal

图6(d)中信号的镜像干扰还是较大,经过多级滤波抽取之后,得到如图7所示的基带信号的频谱图,信号带宽为1.4 MHz,信号经过高性能FIR滤波器带外噪声抑制为80 dB。以上从频域分析了算法设计的正确性。

为了验证数字下变频的正确性,对上述仿真得到的基带数据进行算法验证。图8为利用辅同步信号(Secondary Synchronization Signal,SSS)序列做的定时粗同步的相关峰,可以看到相关峰很明显,还正确解出了小区ID=293和CP=0等系统信息,验证了数字下变频的正确性。

图8 定时粗同步的相关峰

Fig.8 Correlation peak of coarse timing synchronization

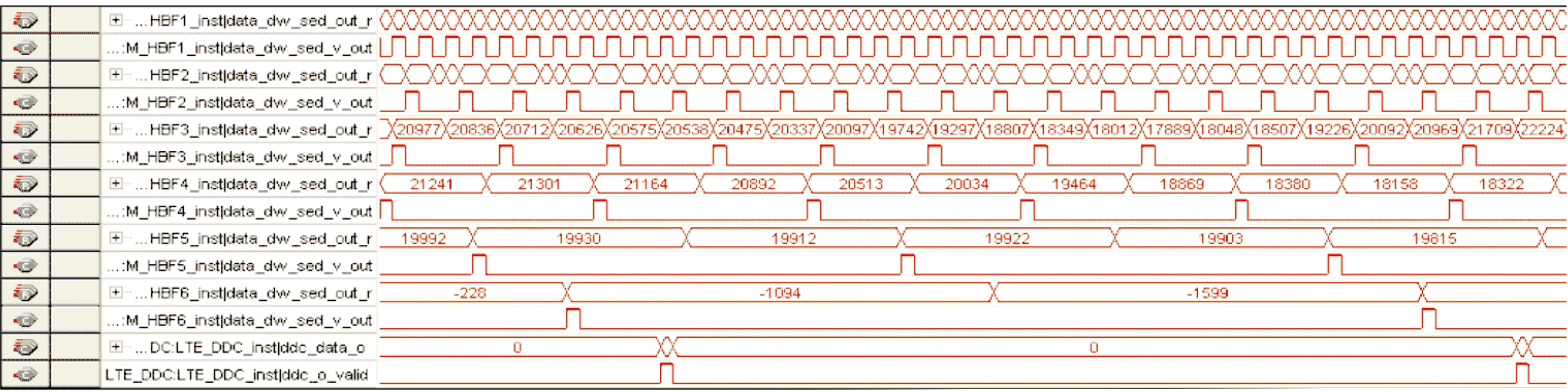

5.2 硬件测试结果

图9为软件无线电平台,包括射频板、基带板和上位机等。将多带宽数字下变频的FPGA设计移植到FPGA芯片。空中TD-LTE信号经过射频板混频和放大后AD采样到中频信号,再经数字下变频到基带信号。通过逻辑分析仪捕捉到的FPGA中数字下变频信号如图10所示,图中是各级降采样滤波模块的数据信号以及数据有效标志位。

图9 硬件测试平台

Fig.9 Hardware test platform

图10 抽取滤波的信号时域图

Fig.10 Signal time domain diagram of extraction filter

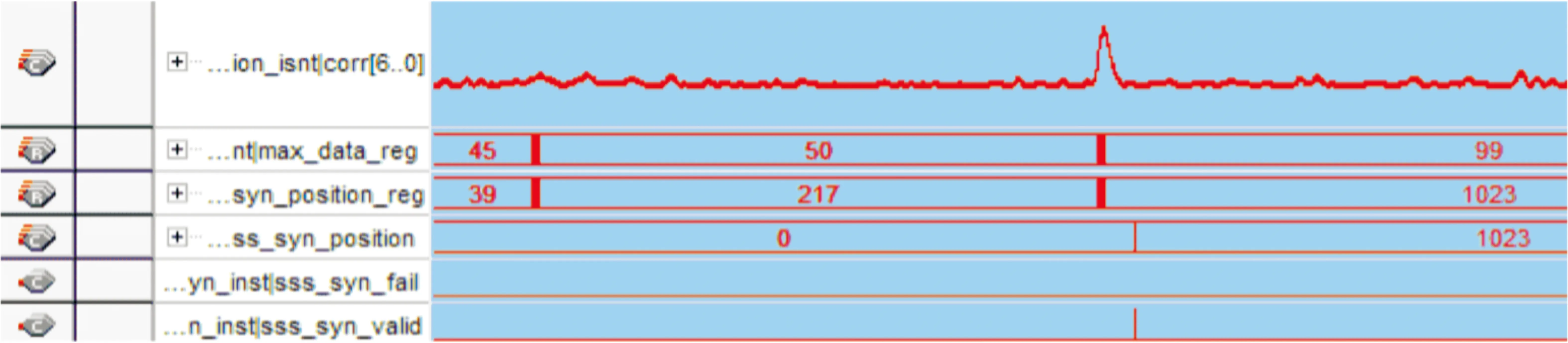

为了验证多带宽数字下变频的正确性,本文还进行了小区搜索的FPGA设计与移植。图11为定时粗同步信号图,可以看到时域波形与图8的仿真基本一致,有明显的相关峰值,同时解得CP=0和ID=293,验证了工程的正确性。

图11 定时粗同步的信号图

Fig.11 Signal of coarse timing synchronization

5.3 资源对比分析

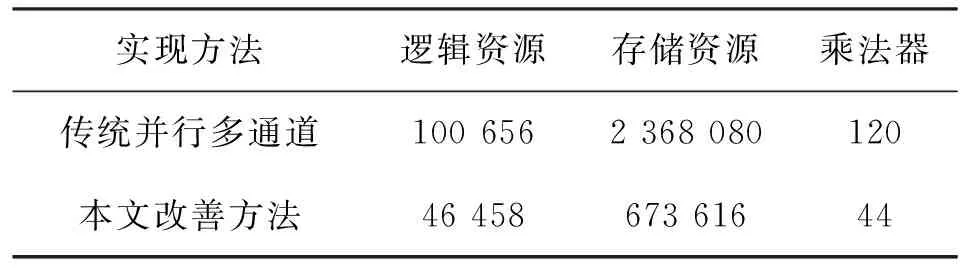

传统的TD-LTE中频一般通过并行多通道的方式实现多种带宽和模式的切换,本文通过灵活的开关选择与复用技术实现TD-LTE多带宽。表2为两种不同实现方式的FPGA的资源消耗的对比,使用的FPGA芯片是EP4SGX230KF40C2。

表2 不同实现方法的资源比较

Tab.2 Resource comparison between different implementation methods

实现方法逻辑资源存储资源乘法器传统并行多通道1006562368080120本文改善方法4645867361644

从表2中可以看出,本文改善方法在逻辑资源、存储资源和乘法器等方面都比传统方法节约相当多的资源。

6 结 论

针对TD-LTE系统支持6种不同带宽和基带速率的特性,本文首先设计了TD-LTE数字下变频的参数,根据参数和通用数字下变频的架构设计了可以兼容6种不同带宽和基带速率的数字下变频;通过采用复用技术对方案进行资源优化,并对混频器和滤波器的设计进行改进和优化。仿真结果表明了本方案的正确性和高性能,硬件测试结果说明各个模块在FPGA芯片上解析出的结果是正确的,证明本文方案的正确性和具有很好的工程实用价值。

[1] ANDREWS J G,BUZZI S,CHOI W,et al.What will 5G be?[J].IEEE Journalon Selected Areasin Communications,2014,32(6):1065-1082.

[2] OMRI A,BOUALLEGUE R.New transmission scheme for MIMO-OFDM system[J].International Journal of Next-Generation Networks,2011,3(1):11-19.

[3] LIN Z H,XIAO P,VUCETIC B,et al.Analysis of receiver algorithms for LTE SC-FDMA based uplink MIM systems[J].IEEE Transactions on Wireless Communications,2010,9(1):60-65.

[4] ZHANG Q X,SU X X.The design of digital down converter based on FPGA[C]//Proceedings of 2012 Wireless Communications,Networking and Mobile Computing(WiCOM).Shanghai:IEEE,2012:1-4.

[5] 张庭伟,袁正午,周牧,等.一种改进的多模数字下变频结构及其FPGA实现[J].电讯技术,2013,53(12):1592-1597. ZHANG Tingwei,YUAN Zhengwu,ZHOU Mu,et al.An improved multimode digital down converter structure and its FPGA implementation[J].Telecommunication Engineering,2013,53(12):1592-1597.(in Chinese)

[6] The 3rd Generation Partnership Project.Physical channels and modulation:3GPP TS 36.101 v11.5.0[S].Valbonne,France:3GPP Support Office,2013:204-211.

[7] 牛光辉,苏鹏.带通采样在多载波数字中频接收机中的应用[J].电讯技术,2008,48(1):47-51. NIU Guanghui,SU Peng.Bandpass sampling and its application in digital IF receiver[J].Telecommunication Engineering,2008,48(1):47-51.(in Chinese)

[8] LEI Z H,WANG W L.The design of NCO based on CORDIC algorithm and implementation in FPGA[C]//Proceedings of 2011 International Conference on Electronics,Communications and Control(ICECC).Ningbo:IEEE,2011:2902-2905.

田增山(1968—),男,河南人,1999年于电子科技大学获博士学位,现为教授,主要研究方向为无线通信、卫星导航、无线定位;

TIAN Zengshan was born in Henan Province,in 1968.He received the Ph.D. degree from University of Electronic Science and Technology of China in 1999.He is now a professor.His research concerns wireless communication,satellite navigation,wireless localization.

李 路(1990—),男,湖北人,硕士研究生,主要研究方向为无线通信。

LI Lu was born in Hubei Province,in 1990.He is now a graduate student.His research concerns wireless communication.

Email:lilu_cqupt@163.com

Design and FPGA Implementation of Multi-bandwidth Digital Down Converter in TD-LTE System

TIAN Zengshan,LI Lu

(Chongqing Key Laboratory of Mobile Communications Technology,Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

Time division-long term evolution(TD-LTE) system needs to support six different bandwidths and baseband rates,in order to satisfy the requirements of various environments.To meet the demand of multi-bandwidth and multi-rate in TD-LTE system,a multi-bandwidth digital down converter(DDC) scheme is designed which can support the flexible switch of multi-bandwidth and multi-rate.The proposed scheme takes advantage of the time division multiplexing,the reasonable collocation and the high performance filter techniques to achieve resource optimization and high signal-to-noise ratio(SNR) of output signal.In addition,a parallel Coordinate Rotation Digital Compute(CORDIC) frequency mixer and a high speed parallel configurable filter are proposed by improving the digital mixer and anti-aliasing filter.Software simulations and hardware tests verify the correctness of the multi-bandwidth DDC scheme.And the proposed scheme is featured by flexibility,high performance,low resource consumption and high value for practical engineering.

TD-LTE system;digital down converter;multi-bandwidth;digital frequency mixer;anti-aliasing filter;field programmable gate array

10.3969/j.issn.1001-893x.2016.07.017

田增山,李路.TD-LTE多带宽数字下变频设计与FPGA实现[J].电讯技术,2016,56(7):808-814.[TIAN Zengshan,LI Lu.Design and FPGA implementation of multi-bandwidth digital down converter in TD-LTE system[J].Telecommunication Engineering,2016,56(7):808-814.]

2015-12-24;

2016-03-04 Received date:2015-12-24;Revised date:2016-03-04

国家自然科学基金资助项目(61301126);重庆市基础与前沿研究计划项目(cstc2013jcyjA40041,cstc2013jcyjA40032);重庆邮电大学博士启动基金(A2012-33)

Foundation Item:The National Natural Science Foundation of China(No.61301126);The Fundamental and Frontier Research Project of Chongqing(cstc2013jcyjA40041,cstc2013jcyjA40032);The Dr.Start-up Foundation of Chongqing University of Posts and Telecommunications(A2012-33)

TN929.5

A

1001-893X(2016)07-0808-07

**通信作者:lilu_cqupt@163.com Corresponding author:lilu_cqupt@163.com