RISC-V架构的开源处理器及SoC研究综述

雷思磊

(酒泉卫星发射中心,酒泉 735000)

RISC-V架构的开源处理器及SoC研究综述

雷思磊

(酒泉卫星发射中心,酒泉 735000)

RISC-V是一种新的指令集架构,发布以来得到了大量关注,在描述了RISC-V的产生背景、基本设计的基础上,简单比较了其与现有的开源指令集架构、商业指令集架构的优劣,然后详细介绍了现有的采用RISC-V架构的开源处理器、开源SoC,并展望了RISC-V的未来发展。

RISC-V;Rocket;BOOM;SoC

引 言

RISC-V是加州大学伯克利分校(University of California at Berkeley,以下简称UCB)设计并发布的一种开源指令集架构,其目标是成为指令集架构领域的Linux,应用覆盖IoT(Internet of Things)设备、桌面计算机、高性能计算机等众多领域。其产生是因为UCB的研究人员在研究指令集架构的过程中,发现当前指令集架构存在如下问题[1]:

① 绝大多数指令集架构都是受专利保护的,比如:x86、MIPS、Alpha,使用这些架构需要授权,限制了竞争的同时也扼制了创新。

② 当前的指令集架构都比较复杂,不适合学术研究,而且很多复杂性是因为一些糟糕的设计或者背负历史包袱所带来的。

③ 当前的指令集架构都是针对某一领域的,比如:x86主要是面向服务器、ARM主要是面向移动终端,为此对应的指令集架构针对该领域做了大量的领域特定优化,缺乏一个统一的架构可以适用多个领域。

④ 商业的指令集架构容易受企业发展状况的影响,比如:Alpha架构就随着DEC公司的被收购而几近消失。

⑤ 当前已有的各种指令集架构不便于针对特定的应用进行自定义扩展。

为此,UCB的研究人员Krste Asanovic、Andrew Waterman、Yunsup Lee决定设计一种新的指令级架构,并决定以BSD授权的方式开源,希望借此可以有更多创新的处理器产生,有更多的处理器开源,并以此降低电子产品成本[2]。RISC-V自2014年正式发布以来,受到了包括谷歌、IBM、Oracle等在内的众多企业,以及包括剑桥大学、苏黎世联邦理工大学、印度理工学院、中国科学院在内的众多知名学府与研究机构的关注和参与,围绕RISC-V的生态环境逐渐完善,并涌现了众多开源处理器及SoC采用RISC-V架构,这些处理器既有标量处理器,也有超标量处理器,既有单核处理器,也有多核处理器。本文简单介绍RISC-V架构的基本设计,并详细描述目前采用RISC-V架构的开源处理器与SoC。

1 RISC-V简介

1.1 RISC-V的基本设计

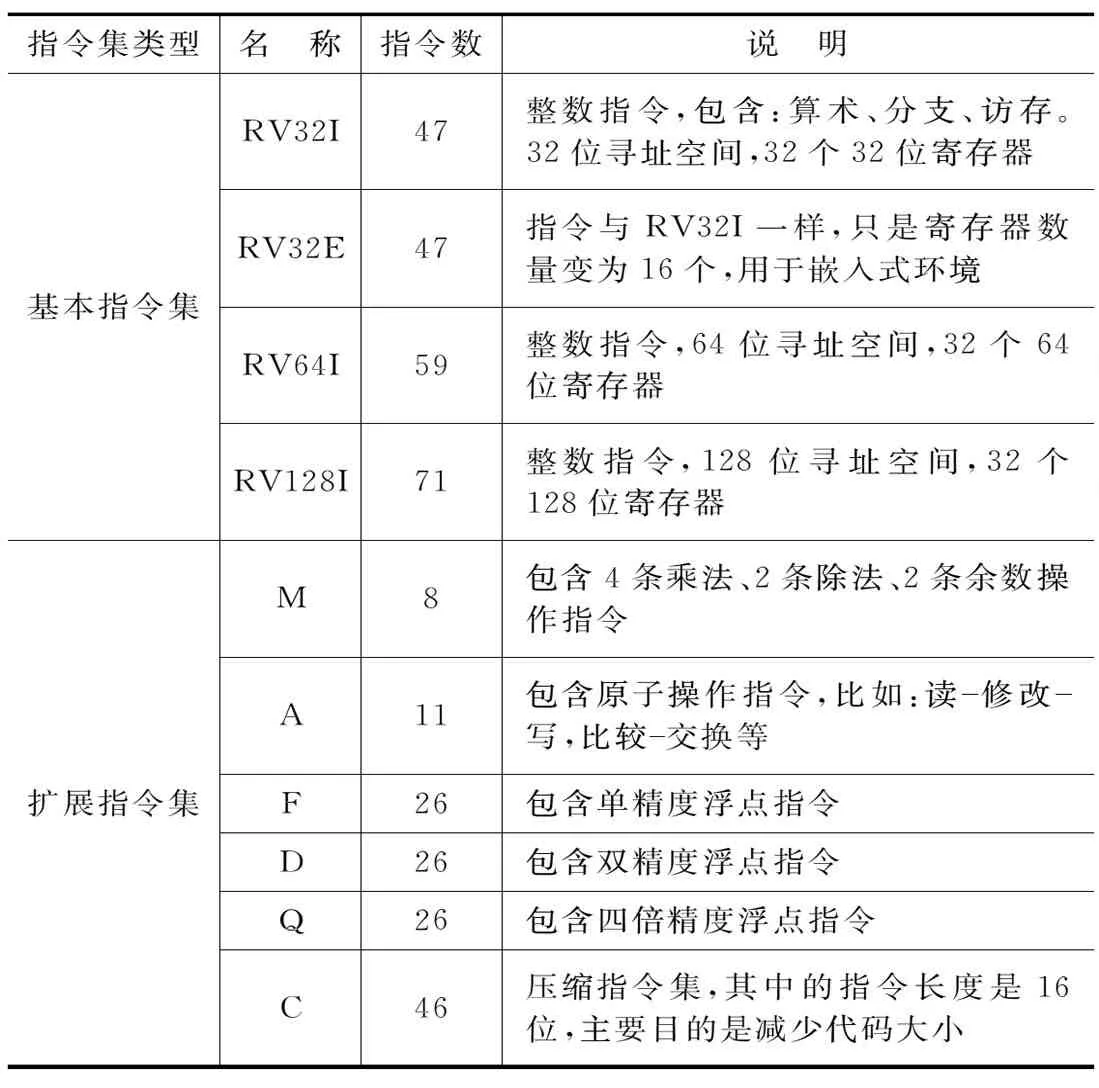

RISC-V是一个典型三操作数、加载-存储形式的RISC架构,包括3个基本指令集和6个扩展指令集,如表1所列,其中RV32E是RV32I的子集,不单独计算。

表1 RISC-V的指令集组成

基本指令集的名称后缀都是I,表示Integer,任何一款采用RISC-V架构的处理器都要实现一个基本指令集,根据需要,可以实现多种扩展指令集,例如:如果实现了RV32IM,表示实现了32位基本指令集和乘法除法扩展指令集。如果实现了RV32IMAFD,那么可以使用RV32G来表示,表示实现了通用标量处理器指令集。本文只介绍RV32I的基本情况。

RV32I指令集有47条指令,能够满足现代操作系统运行的基本要求,47条指令按照功能可以分为如下几类:

① 整数运算指令,实现算术、逻辑、比较等运算。

② 分支转移指令,实现条件转移、无条件转移等运算,并且没有延迟槽。

③ 加载存储指令,实现字节、半字、字的加载和存储操作,采用的都是寄存器相对寻址方式。

④ 控制与状态寄存器访问指令,实现对系统控制与状态寄存器的原子读-写、原子读-修改、原子读-清零等操作。

⑤ 系统调用指令,实现系统调用、调试等功能。

1.2 RISC-V的优势

1.2.1 与开源指令集架构比较

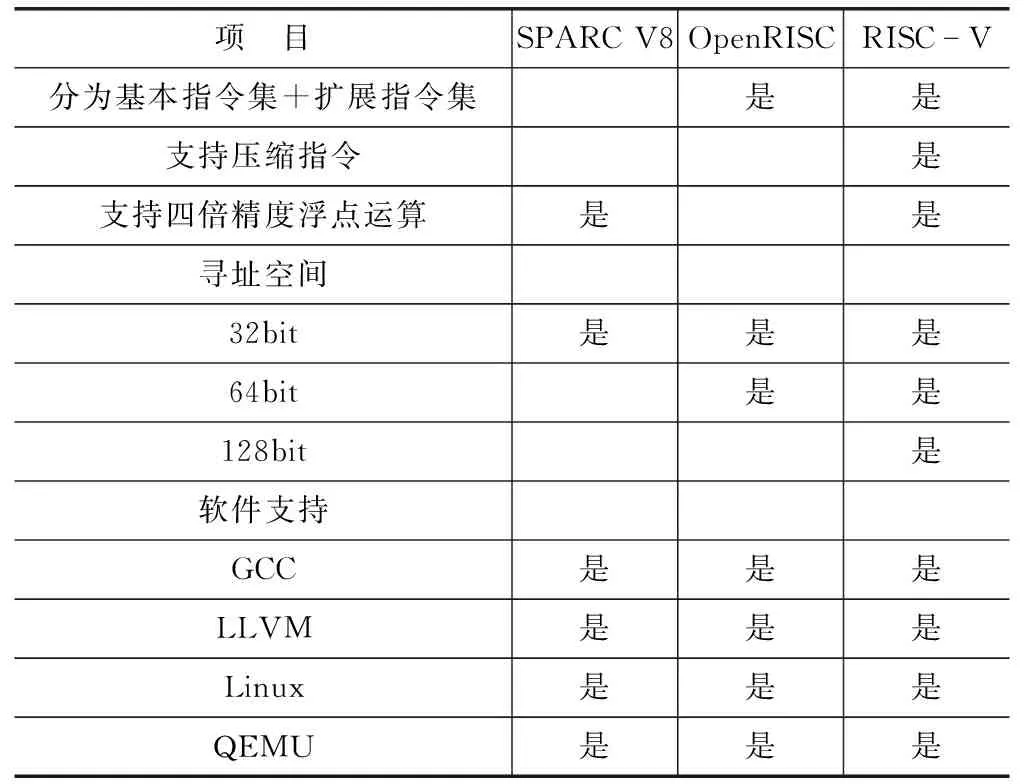

在RISC-V发布之前,实际上已经有几种开源指令级架构,包括SPARC V8、OpenRISC,其中SUN发布的开源多核多线程处理器OpenSparcT1、OpenSparcT2,以及欧空局的LEON3采用的就是SPARC V8,OpenRISC也有同名的开源处理器,RISC-V与前两者的比较如表2所列。此外,OpenRISC的许可证为GPL,这意味着所有的指令集改动都必须开源,而RISC-V的许可证是较为宽松的BSD License授权。

表2 RISC-V与SPARC V8、OpenRISC的比较[2]

1.2.2 与商业指令集架构比较

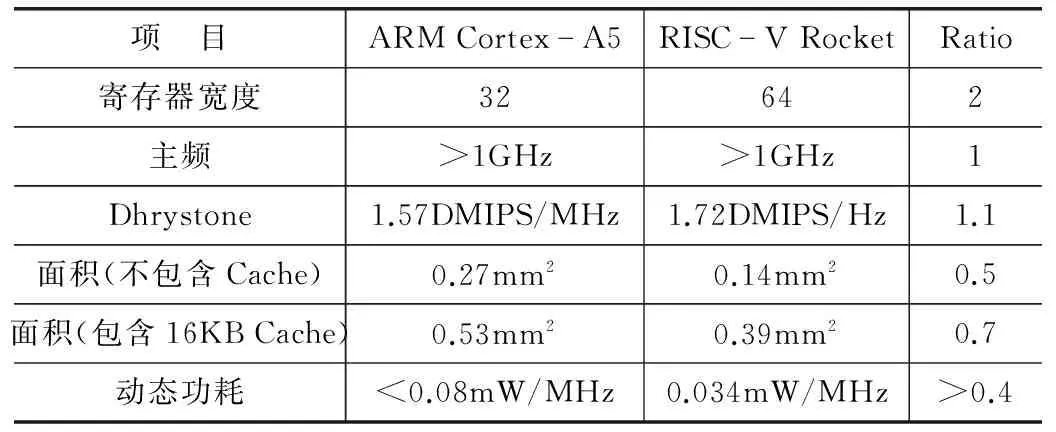

UCB的研究人员设计了一款采用RISC-V指令集架构的开源处理器Rocket,并且成功流片了11次,其中采用台积电40 nm工艺时的性能,与采用同样工艺的、都是标量处理器的ARM Cortex-A5的性能对比如表3所列,可见Rocket占用面积更小,且功耗更低,性能更优。

表3 ARM Cortex-A5与采用RISC-V指令集架构的Rocket比较[2]

2 基于RISC-V的开源处理器研究现状

2.1 标量处理器——Rocket

Rocket是UCB设计的一款64位、5级流水线、单发射顺序执行处理器,主要特点有:支持MMU,支持分页虚拟内存,所以可以移植Linux操作系统;具有兼容IEEE 754-2008标准的FPU;具有分支预测功能,具有BTB(Branch Prediction Buff)、BHT(Branch History Table)、RAS(Return Address Stack)。

Rocket是采用Chisel(Constructing Hardware in an Scala Embedded Language)编写的,这也是UCB设计的一种开源的硬件编程语言,是Scala语言的领域特定应用,可以充分利用Scala的优势,将面向对象(object orientation)、函数式编程(functional programming)、类型参数化(parameterized types)、类型推断(type inference)等概念引入硬件编程语言,从而提供更加强大的硬件开发能力。Chisel除了开源之外,还有一个优势就是使用Chisel编写的硬件电路,可以通过编译得到对应的Verilog设计,还可以得到对应的C++模拟器。Rocket使用Chisel编写,就可以很容易得到对应的软件模拟器。同时,因为Chisel是面向对象的,所以Rocket的很多类可以被其他开源处理器、开源SoC直接使用。

2.2 超标量乱序执行处理器——BOOM

BOOM(Berkeley Out-of-Order Machine)是UCB设计的一款64位超标量、乱序执行处理器,支持RV64G,也是采用Chisel编写,利用Chisel的优势,只使用了9 000行代码,流水线可以划分为6个阶段:取指、译码/重命名/指令分配、发射/读寄存器、执行、访存、回写。

借助于Chisel,BOOM是可参数化配置的超标量处理器,可配置的参数包括:

① 取指、译码、提交、指令发射的宽度。

② 重排序缓存ROB(Re-Order Buffer)、物理寄存器的大小。

③ 取指令缓存、RAS、BTB、加载、存储队列的深度。

④ 有序发射还是无序发射。

⑤ L1 Cache的路数。

⑥ MSHRs(Miss Status Handling Registers)的大小。

⑦ 是否使能L2 Cache。

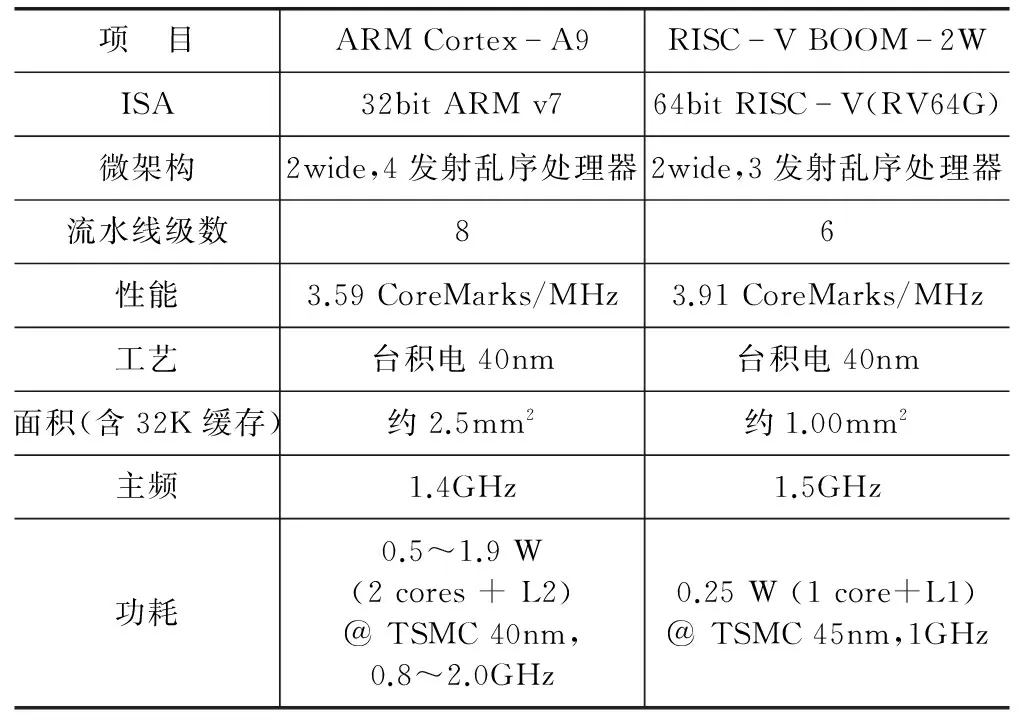

UCB已经在40 nm工艺上对BOOM进行了流片,测试结果如表4所列。可见BOOM与商业产品ARM Cortex-A9的性能要略优,体现在面积小、功耗低。

表4 BOOM与ARM Cortex-A9的性能对比[3]

2.3 处理器家族——SHAKTI

SHAKTI[4]是印度理工学院的一个计划,目标是设计一系列适合不同应用环境的、基于RISC-V的开源处理器,以及一些IP核,以便搭建SoC。这些处理器是E-Class、C-Class、I-Class、M-Class、S-Class、H-Class、T-Class、N-Class,目前已经开源的是前三个,使用Bluespec System Verilog编写。

E-Class:32位标量处理器,3级流水线,支持RISC-V的C(Compress)扩展,目标是超低功耗处理器。

I-Class:64位、1~8核,乱序执行处理器,共享L2 Cache、支持双线程、SIMD/VPU,目标是通用处理器。

M-Class:I-Class的增强版,增加了指令发射大小、支持四线程、最高支持16核,目标是通用处理器、低端服务器和移动应用。

S-Class:64位、超标量多线程处理器,支持L3 Cache、RapidIO、HMC(Hybrid Memory Cube)、向量处理单元,还有协处理器用于数据库访问、加密算法、机器学习,最高支持64核,目标是通用处理器、服务器。

H-Class:64位、32~128核、支持多线程、顺序或者乱序执行处理器,具有向量处理单元,目标是高性能计算。

T-Class:64或者128位处理器,其中通过为存储器引入Tag,从而增强其安全性。

N-Class:目标是通过自定义的扩展进行网络数据处理。

2.4 嵌入式应用处理器——ORCA

PicoRV32是由VectorBlox公司设计的一款32位标量处理器,目标是应用于嵌入式领域,采用VHDL编写,实现了RV32IM,也可以移除其中的M扩展,也就是移除乘法除法扩展,从而减少芯片占用资源,甚至可以移除与定时器有关的指令,从而仅仅实现RV32E。当ORCA作为一个软核下载到FPGA上的时候,其资源占用与主频如表5所列。

尽管PPP项目有其独特的优势,但其在智慧城市领域的实际应用中实现建设落地的并不多,依旧处于起步建设阶段。PPP模式的运营周期主要分为识别认证、准备材料、采购落实、执行方针和移交五个阶段。而目前根据政府和社会资本合作(PPP)综合信息平台了解,智慧城市PPP项目有累计86个依旧处于识别认证时期,占总比例的53.4%。而在历经三个阶段考验后,停滞于执行方针阶段的项目累计达到24个,占比14.9%。其很大一部分原因是由于国内尚未出台针对PPP模式的专项税收政策,因此在智慧城市的PPP项目推进过程中面临诸多税收不确定性,例如财政不同的重复征税、优惠政策覆盖面有限等。

表5 ORCA不同配置时的资源占用与主频[5](以Altera's Cyclone IV为目标FPGA)

2.5 其他开源处理器

(1) RI5CY

RI5CY是由苏黎世联邦理工大学和波罗尼亚大学联合设计的一款小巧的4级流水线开源处理器,实现了RV32IC以及RV32M中乘法指令mul,其目标是作为并行超低功耗处理器项目PULP(Parallel Ultra Low Power)的处理器核,所以RI5CY在RISC-V的基础上增加了许多扩展,包括硬件循环、乘累加、高级算术指令等。采用UMC的65 nm工艺进行流片,RI5CY主频达到654 MHz,动态功耗是17.5 μW/MHz[6],采用SystemVerilog编写。

(2) RIDECORE

RIDECORE (RIsc-v Dynamic Execution CORE)是由东京工业大学设计发布的一款超标量乱序执行处理器,实现了RV32IM,6级流水线分别是取指、译码、指令分配、发射、执行、提交,可以同时取两条指令、对两条指令译码、提交两条指令,采用的是Gshare分支预测机制。

(3) Hwacha

Hwacha是由UCB开发的一款向量处理器,UCB将Hwacha作为RISC-V的一个非标准扩展Xhwacha,已经以28 nm和45 nm的工艺流片多次,主频在1.5 GHz以上,目前还在研发中,正在修改OpenCL的编译器,以适合Hwacha,UCB计划以开源的形式发布其代码。

(4) f32c

f32c是由萨格勒布大学设计发布的32位、5级流水线、标量处理器,原本实现的是MIPS指令集,后来添加实现了RISC-V指令集,处理器包括分支预测、直接映射缓存,同时发布的还有SDRAM控制器、SRAM控制器、视频FrameBuffer、SPI控制器、UART、GPIO等IP,使用VHDL编写代码。使用f32c处理器核,萨格勒布大学发布了FPGArduino项目,该项目将一块FPGA开发板变为一个Arduino板,并且可以使用Arduino IDE进行程序编译下载。

(5) Z-scale/V-scale

Z-scale是UCB发布的针对嵌入式环境的32位、3级流水线、单发射标量处理器,实现了RV32IM,指令总线和数据总线都是AHB-Lite。Z-scale采用是Chisel编写代码,利用Rocket中的代码,仅增加了604行代码就实现了Z-scale。V-scale是Z-scale对应的Verilog版本。

(6) sodor

sodor是UCB发布的针对教学的32位开源处理器系列,采用Chisel编码实现,可以很容易的得到对应的C++模拟器。sodor系列有5种处理器,分别是单周期处理器、2级流水线处理器、3级流水线处理器、5级流水线处理器、可执行微码的处理器。

(7) PicoRV32

PicoRV32是由RISC-V开发者Clifford Wolf设计发布的一款大小经过优化的开源处理器,实现了RV32IMC,并且根据不同环境可配置为实现RV32E、RV32I、RV32IC、RV32IM、RV32IMC。内置一个可选择的中断控制器,其特点是小巧,在Xilinx7系列芯片上占用750~2 000个LUT,速度可以达到250~400 MHz。PicoRV32采用Verilog编写代码。

(8) Tom Thumb

Tom Thumb是由RISC-V开发者Maikmerten设计发布的一款32位、6级流水线开源处理器,实现了RV32I,目标是尽量减少FPGA的资源占用,在Cyclone IV系列FPGA上大约占用资源1200 LEs,采用VHDL编写代码。

(9) FlexPRET

FlexPRET[7]是由UCB设计发布的5级流水线、多线程处理器,目标是使用在实时嵌入式应用中,线程数量可配置为1~8。为了提高嵌入式处理器的资源利用率,每个硬件线程被标记为硬实时(hard real-time thread)或者软实时(soft real-time thread),硬实时线程按照固定的频率被调度,如果当前没有硬实时线程可调度,再调度软实时线程。使用Chisel编写代码。

(10) YARVI

YARVI(Yet Another RISC-V Implementation)是由RISC-V开发者Tommy Thorn设计发布的一款简单的、32位开源处理器,实现了RV32I,使用Verilog作为开发语言。其出发点不在于性能,而是要能够清晰、准确地实现RV32I。

3 基于RISC-V的开源SoC研究现状

3.1 Rocket-Chip

UCB为了方便用户学习,同时也为了便于重复使用已设计好的硬件模块,在GitHub上建立了Rocket-Chip Generator的项目,其中包括了Chisel、GCC、Rocket处理器,以及围绕Rocket的一系列总线单元、外设、缓存等,并且采用了参数化的配置方法,从而可以方便地创建不同性能要求的基于Rocket处理器的SoC。采用Chisel编写,主要的子模块如下:

① Chisel:UCB设计的开源硬件编程语言。

② Hardfloat:参数可配置的、兼容IEEE 754-2008标准的浮点单元。

③ Riscv-tools:开发工具,包括GCC、Newlib,以及移植的Linux。

④ Rocket:Rocket处理器,包括L1 Cache。

⑤ Uncore:实现了需要与Rocket紧密连接的功能单元,比如L2 Cache、L1 Coherence Hub等。

⑥ Juntions:实现了不同协议的接口之间的转换。

⑦ Rocketchip:顶层模块,同时也实现了内部总线TileLink向外部总线AXI或者AHB的转换。

前文介绍的BOOM、Z-scale都可以通过配置Rocket-Chip的不同参数得到。

3.2 LowRISC

LowRISC是由剑桥大学为主的一些研发人员成立的非营利性组织,主要是设计发布基于RISC-V指令集的64位开源SoC,其成员有树莓派的合作者,目标是希望将设计的SoC做成像树莓派那样价格便宜、功能丰富、拥有大量用户的开源硬件。LowRISC发布的SoC的名称也是LowRISC,是在Rocket-Chip的基础上改进开发的,采用System Verilog编写改进部分的代码。主要特点是:

① Tagged Memory。给每一个存储位置都增加了一个Tag,目前是双字(64位)对应一个Tag(4位),目的是防止控制流劫持攻击,同时也有其他的一些用处,比如:垃圾回收、设置watchpoint等。为了实现Tagged Memory,LowRISC为RISC-V增加了两条指令用来读写Tag。2015年4月发布的0.1版本中具有该功能。

② Untethered。早期的Rocket-Chip需要依赖于一个通用处理器的协助才能够启动,才能够访问串口、网口、SD卡等外设,Untethered LowRISC通过实现(Memory mapping I/O)、片上NASTI interconnect等功能,解决了上述问题。2015年11月发布的0.2版本中具有该功能。

③ Trace Debugging。引入了Open SoC Debug,支持Trace Debugging,可以收集指令执行记录,便于离线或者在线分析。2016年7月发布的0.3版本中具有该功能。

3.3 PULPino

PULPino是苏黎世联邦理工大学和波罗尼亚大学联合发布的基于RISC-V的开源处理器,其处理器核RI5CY在前文已述,苏黎世联邦理工大学和波罗尼亚大学本来设计的项目是PULP,这是一个多核SoC项目,考虑到这个项目太复杂,有许多IP、自定义工具集,不方便开源,所以开发者决定先开源一个单核SoC项目,即PULPino。PULPino直接使用了PULP项目的许多IP。

PULPino具有一个AXI互连总线,另外还有一个APB总线,用来连接低速外设,比如:GPIO、UART、I2C控制器、SPI Master控制器等。调试模块支持Advanced Debug Unit。PULPino包括一个Boot ROM,其中可以写入BootLoader,从而实现在启动的时候从外部Flash读入程序并执行。

3.4 RISC-V VHDL

RISC-V VHDL是俄罗斯的GNSS Sensor公司发布的基于Rocket的开源SoC,其前身是莫斯科物理技术学院的一个项目。该项目的处理器核直接用的是Rocket,可以配置为只有L1 Cache,也可以配置为包括L2 Cache,在此基础上,提供了大量的IP核,采用类似LEON3的GRLIB库的方式,所有的IP核都是即插即用,RISC-V VHDL提供了一个AXI总线,IP核都挂载在该总线上。IP核包括:UART、GPIO、中断控制器、以太网控制器,此外还支持DSU(Debug Support Unit),均采用VHDL编写代码。RISC-V VHDL中大多数IP核都是开源的,唯一商业的是GNSSLIB,这是一个与定位导航有关的库,也是RISC-V VHDL的特色。

结 语

RISC-V的发展十分迅速,除了前文已述的基于RISC-V的开源处理器、开源SoC大量涌现,还有很多的商用处理器也计划采用RISC-V指令集架构,比如PulSAR[8],采用的是一个异构多处理器结构,其中包括2个标量处理器Rocket,还包括两个超标量乱序执行处理器BOOM。RISC-V的发展一方面得益于自身设计吸取了RISC接近40年的经验教训,使得架构设计更加合理;另一方面得益于日渐成熟的软件生态,UCB提供了针对RISC-V的开源编译器GCC、LLVM,还提供了开源仿真器Spike、QEMU,社区还移植了FreeBSD、Debian、Gentoo、Yocto、Genode等操作系统。

[1] A Waterman,Y Lee,DA Patterson, et al.The RISC-V Instruction Set Manual, Volume I: User-Level ISA[J].Eecs Department,2011, 7(9):475.

[2] Krste Asanovic, David Patterson.The Case for Open Instruction Sets[J].MICROPROCESSOR report, 2014(8): 1-7.

[3] Celio, Christopher and Patterson, David A.and Asanovic, Krste, The Berkeley Out-of-Order Machine (BOOM): An Industry-Competitive, Synthesizable, Parameterized RISC-V Processor[R].EECS Department, University of California, Berkeley, June 2015.

Research on Open Source Processor and SoC Based on RISC-V

Lei Silei

(Jiuquan Satellite Launch Center,Jiuquan 735000,China)

RISC-V is a new instruction set architecture(ISA),and it gets a lot of attention since the release.On the basis of describing the background and the basic design of RISC-V,the advantages and disadvantages with the existing open-source instruction set architecture and commercial instruction set architecture are compared.Then the existing open source processor and SoC using RISC-V architecture are described.Finally,the future development of RISC-V is prospected.

RISC-V;Rocket;BOOM;SoC

TP368.1

A