一种SRAM读取时间自测试电路及测试方法

西安紫光国芯半导体有限公司 拜福君 段会福 付 妮 李晓骏

一种SRAM读取时间自测试电路及测试方法

西安紫光国芯半导体有限公司 拜福君 段会福 付 妮 李晓骏

本文设计了一种SRAM读取时间自测试电路及测试方法,通过增加一个延时扫描电路、一个比较器和一个计数器,可以自动扫描并快速地找到与SRAM读取时间最近接的延时,通过测量由该延时组成的环形振荡器的振荡周期从而得到SRAM的读取时间。这种测试方法避免了测试时频繁的人工操作介入,测试效率高,并且由于采用固定延时单元和具有多个可选延时的单元的组合方式,在保证较大的测量范围的前提下,节省版图面积。

SRAM;读取时间;自测试

一、引言

静态随机存储器(SRAM: Static Random Access Memory)在集成电路领域有广泛应用。读取时间是其重要的时序参数指标,表征了读操作时从时钟信号上升沿到输出数据有效的延时。

如何对SRAM的读取时间进行实测?內自建测试电路技术(BIST)[1]通过搭载在芯片上的硬件电路实现存储器的高速测试,虽然实现了测试自动化,但只能证明SRAM功能正常,无法测量其读取时间。因此为了测试SRAM的读取时间,只能在SRAM读操作时对输出数据在不同的延时之后进行采样并将采样结果与SRAM输出数据作比较[4]。如果该延时大于读取时间则采样数据与SRAM输出数据相同。通过不断的调整采样延时可以找到使采样数据正确的最小延时作为SRAM读取时间的测量值。这个原理在实际应用时需要克服的难点包括:一、测量过程比较繁琐,需要测试人员不停地改变延时电路直到找到合适的延时使得数据采样电路的结果正确,整个测试比较耗时;二、延时电路本身延时的大小需要准确的测量;三、为了获得较大的测量范围和测量精度,必须要放置大量的延时电路,造成芯片面积的浪费。

针对上述技术难点,本文提出的SRAM读取时间自测试电路及测试方法可以对延时做自动扫描从而快速准确测量出SRAM的读取时间。

二、SRAM读取时间自测试电路

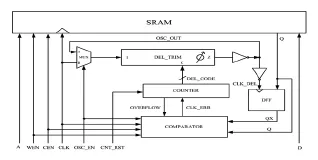

本文提出的SRAM读取时间自测试电路如图1所示,包括待测的SRAM、一个二路选择器MUX、一个延时扫描电路DEL_TRIM、一个锁存器DFF、一个比较器COMPARATOR、一个计数器COUNTER和其他一些电路。

待测SRAM连接至输入地址信号A、输入写信号WEN、输入片选信号CEN、输入时钟信号CLK、输入数据D和输出数据Q;

二路选择器用于测试电路模式的切换,由测试模式选择信号OSC_EN控制。当OSC_EN有效时,延时扫描电路经过一个反相器和二路选择器形成一个首尾相连的环形震荡器,用于测量扫描延时电路的延时。反之当OSC_EN无效时,输入时钟CLK经过延时扫描电路延迟后得到新的时钟信号CLK_DEL,该信号用来对SRAM的输出数据进行采样。

延时扫描电路的延时大小由其控制端DEL_CODE决定。DEL_ CODE来自于计数器,随着着计数器的累加,延时扫描电路的延时也逐步增加从而实现了延时的扫描。

锁存器对SRAM的输出数据进行采样,由于在扫描过程中其时钟信号CLK_DEL的延时在不断增加,锁存器的采样点也在不断后移。

比较器在SRAM执行读操作时对锁存器的采样数据和SRAM的输出数据进行比较并在两组数据不同时通过CLK_ERR信号使计数器累加。随着计数器的累加,锁存器采样点不断后移,当数据相同时整个自测试电路会停止。此时延时扫描电路的延时大小就与SRAM的读取延时相当。当然如果SRAM的读取时间大于延时扫描电路的最大延时则无论如何比较器也无法找到能使这两者相当的计数器的计数值,这种情况下测试在计数器溢出(OVERFLOW)后停止。

图1 SRAM读取时间自测试电路图

三、延时的扫描和确定

延时的扫描和确定是SRAM读取时间测试的难点。

图2是延时扫描电路的原理图,延时扫描电路由固定延时电路DEL_ FIX和具有多个可选延时的可调延时电路DEL_STEP串联而成。延时扫描电路的延时tD=tDF+tDT,其中tDF为固定延时电路的延时,tDT为可调延时电路的延时。可调延时电路的延时tDT=tDTmin+N*tDS,其中tDTmin为延时最小值,tDS为可调步长。则tD=tDF+ tDTmin+N*tDS,其中N为计数器的计数值,满足N为自然数且0≤N≤M。整个延时扫描的范围是[tDF+tDTmin, tDF+tDTmin+M*tDS],在测试电路设计时务必保证预期的SRAM读取时间包含在该范围内并留有余量。

图2 延时扫描电路原理图

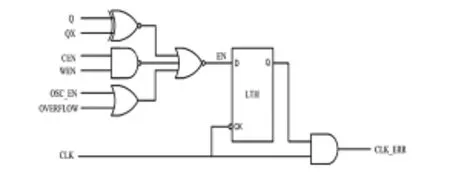

图3 比较器电路原理图

图3 是比较器的原理图。只有当片选信号无效,写信号无效,测试模式为扫描模式(即OSC_EN无效)且计数器没有溢出时,比较器才会对SRAM的输出数据Q和锁存器的采样数据QX进行比较。而当CLK的上升沿时,若比较结果不同则CLK_ERR上出现一个脉冲使计数器累加,否则计数器将停留在当前计数值不变。换句话说,在计数器停止且未溢出时,通过测量延时扫描电路的延时就可以确定SRAM的读取时间。

四、SRAM读取时间自测试方法

基于上所述原理和电路,SRAM读取时间的测试步骤如下:

第一步,测试模式选择信号OSC_EN置为无效,并通过CNT_ RST信号将计数器复位。此时,SRAM的输入时钟CLK经过二路选择器、延时扫描电路等逻辑电路延时后形成延后的时钟信号CLK_DEL。计数器复位后,DEL_CODE为0,OVERFLOW为‘0’。

第二步,对SRAM进行正常的读写操作,在每次读操作时,测试电路对待测SRAM的输出数据Q进行采样和比较,并根据比较结果调整采样延时,直到采样正确或者计数器溢出。在每次读操作时,锁存器使用经过延时产生的CLK_DEL信号作为时钟对SRAM的输出数据Q进行采样。与此同时比较器会对采样结果QX和Q进行比较,只要比较结果不同时比较器将在该读操作的下一个时钟周期生成一个脉冲信号CLK_ERR。一旦CLK_ERR信号的上升沿来临,则计数值DEL_CODE加1。随着计数值的增加,延时扫描电路的延时将逐步增加,从而实现了延时的自动扫描。扫描结果有两个:1.在DEL_CODE=N时,比较器的比较结果相同,计数器停止累加且未溢出,从CLK到CLK_DEL的延迟就是测试电路找到的最接近且不小于SRAM 的读取时间的延时,继续进行第三步的测量;2.计算器溢出,OVERFLOW信号为‘1’,此时比较器也将停止工作,表示SRAM的读取时间超过了测量范围的最大值,测试结束。

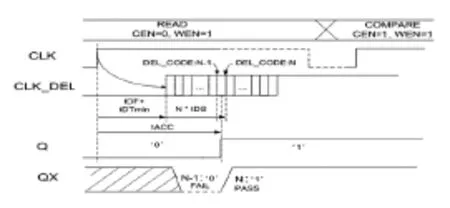

图4 SRAM读取时间测试波形图

图4 是测试电路自动扫描并找到与SRAM读取时间tACC相当延时的过程示意图。首先,向测试电路发送读命令(CEN=0,WEN=1),测试电路将对SRAM 进行一次读操作读出数据Q。此时DEL_CODE=N-1,则经过tDF+tDTmin+(N-1)*tDS的延时后锁存器对读出数据进行采样得到QX。然后,向测试电路发送比较命令COMPARE(CEN=1, WEN=1),测试电路对Q和QX进行比较。若数据不同,则比较结果CLK_ERR上出现一个脉冲信号,该信号上升沿使得计数器计数加1,此时DEL_CODE=N。然后不断重复以上两个命令直到比较数据相同,假设当DEL_CODE=N时数据相同,则SRAM的读取时间约为tDF+tDTmin+N*tDS。

第三步,测试模式选择信号OSC_EN置为有效,二路选择器MUX、延时扫描电路DEL_TRIM和一个反相器形成一个环形振荡器。先测量该环形振荡器的震荡周期,然后计算得到SRAM的读取时间。若环形振荡器的输出信号为OSC_OUT的振荡周期为tOSC,则SRAM的读取时间为tACC=0.5*tOSC。

五、结束语

本文设计了一种SRAM读取时间自测试电路及测试方法,通过增加一个延时扫描电路、一个比较器和一个计数器,可以实现对延时时间的自动扫描并快速地找到与SRAM读取时间最近接的延时,通过测量由其组成的环形振荡器的振荡周期得到SRAM的读取时间值。这种测试方法一方面节省了测试时间,多个延时单元的选择通过测试电路自动完成,只需要进行一次测试就能对所有的延时单元进行扫描从而找到合适的延时大小。另一方面节省了布局空间,采用固定延时单元和具有多个可选延时的单元的组合方式,在保证较大的测量范围的前提下节省了版图面积。

[1]须自明,苏彦鹏,于宗光.基于March C-算法的SRAM BIST电路的设计[J].半导体技术,2007,32(3):245-247.

[2]Van D G A J.Using march tests to test SRAMs[J].IEEE Design & Test of Computers,1993,10(1):8-14.

[3]拜福君.SRAM读取时间自测试电路及测试方法:,CN103886913A[P].2014.

[4]张艳.数字集成电路可测试性设计研究与应用[D].浙江大学,2010.

拜福君(1982—),男,工学硕士,工程师,现任职于西安紫光国芯半导体有限公司,从事半导体存储的研究工作,研究领域包括DRAM、SRAM和FLASH存储器,主要研究方向为存储单元阵列设计。