集成电路中多重图形工艺专利技术综述

曹丽冉

摘 要:集成电路制造工艺的发展是以特征尺寸的减小作为原驱动力的,特征尺寸的减小极大程度上取决于光刻技术的发展,多重图形工艺被认为是目前实现22nm技术,甚至14nm技术的重要的可行性解决方案,本文通过对专利文献进行检索,统计和分析了多重图形工艺的发展现状,重点梳理了该领域的专利申请量趋势、分布地区、重要申请人等状况,并对技术发展的趋势进行了预测。

关键词:集成电路;多重图形工艺;专利

从20世纪50年代以来,集成电路的发展遵循着特征尺寸减小,技术代升级的摩尔定律(Moores Law),特征尺寸的减小极大程度上取决于光刻技术的发展,多重图形工艺被认为是成为193nm ArF光刻工艺向极紫外(EUV)光刻工艺过渡的技术桥梁。本文以专利申请的角度,从技术现状分析、专利申请状况分析和技术发展趋势3个方面对多重图形工艺进行了分析。

1 技术现状分析

多重图形技术的原理是将一套高密度的电路图形分解成多套分立的、密度低一些的图形,然后将它们印制到目标圆晶上。实现多重图形的方法大致分为3类:纯间距分离技术、纯间距分割技术和间距分离分割混合技术。

多重图形技术是在双重图形技术的基础上发展起来的,纯间距分离技术实现多重图形可以分为基于单刻蚀双重图形(SEDP)的纯间距分离技术和基于二次刻蚀双重图形(DEDP)的纯间距分离技术。基于单刻蚀双重图形(SEDP)的纯间距分离技术由于受制于空间成像能量的阈值问题,在一定的线宽下,多种光刻胶在多次曝光中都得到兼顾且不发生互相影响是几乎不可能的;而基于二次刻蚀双重图形(DEDP)的纯间距分离技术避免了中多次光刻胶的相互作用,然而这种方法的明显弱点就是光刻的线宽成倍减小后,光刻和刻蚀的成本也成倍增加,并由此带来了设备产能的降低,所耗费机时的增加和由于引入的多次光刻和刻蚀带来的CD均匀性和重合精度的工艺控制的难度,导致成本的增加。

纯间距分割技术是在自对准双重图形(SADP)技术的基础上发展起来,纯间距分割技术实质上是SADP技术的多次重复,多重纯间距分割技术有能力实现拥有优异线宽和节距控制效果的高密度平行线条。对于任意给定的可以用光刻方法定义的线条,可以在每个侧边使用间隔层,当去除最初的核心材料后,就能有效实现线条密度的加倍。由于纯间距分割图形技术只需要一次高等级光刻工艺,增加一次形成侧墙和刻蚀的工艺,在成本上并没有增加太多,相对于纯间距分离技术具有明显的成本优势,体现了极大的优越性。目前美国Applied Materials和Lam Research两家公司都提供多重纯间距分割技术解决方案。

间距分离分割混合工艺能够结合产品实际设计需要,提供更多的工艺组合,这样就可以为版图的分解提供更高的自由度,具备一定的发展前景。

2 专利申请状况分析

针对多重图形技术,作者在全球专利数据库对该领域的专利申请进行了检索、统计和分析,由于光刻工艺是集成电路制造领域的核心技术,在多重图形技術方面的专利申请人更是集中了全球多家知名半导体企业,其注重在全球范围的专利布局,专利年度申请量趋势能够在一定程度上反映技术受关注的程度及技术发展的趋势,其中,在2004至2006年,专利申请量快速增长,美国Intel、应用材料、韩国三星、荷兰ASML等重要半导体企业注重专利布局,实现核心技术向专利成果的转化;在2006年以后,申请量基本保持恒定,技术趋于成熟,台湾台积电、韩国海力士和中国中芯国际等企业也先后在多重图形技术方面申请专利保护。

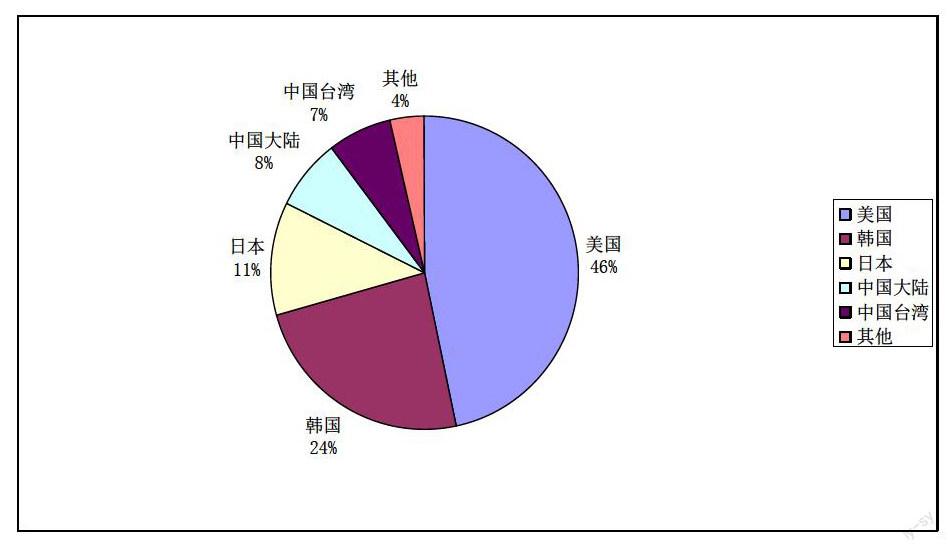

作者也对该领域的首次申请国家/地区分布进行了分析,其中美国的专利量最多,占到了全球专利申请量的46%,在一定程度上反映了美国在集成电路制造技术领域的引领地位;韩国得益于三星、海力士等知名半导体,申请量位居第二,占到了总申请量的24%,其次是日本、中国大陆和中国台湾,这5个国家/地区的申请量占到了总申请量的95%,集中了多重图形技术领域的主要研发力量。

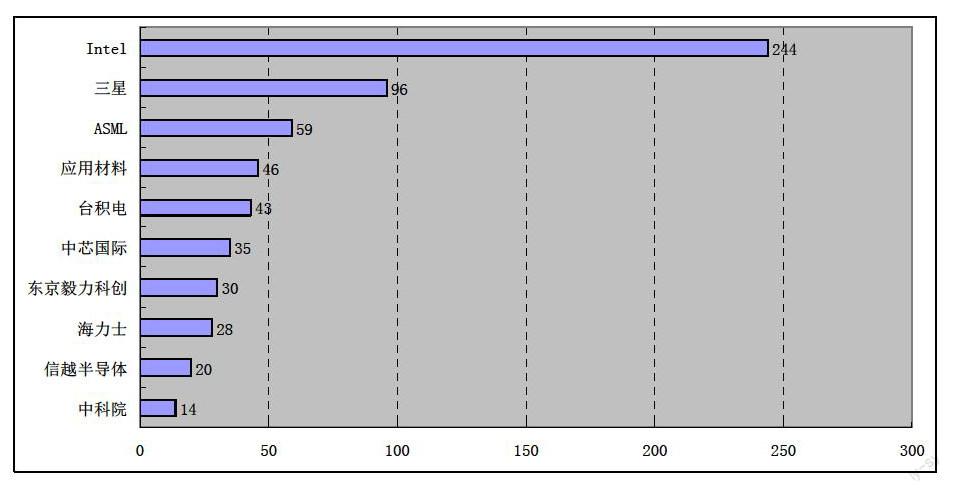

多重图形技术重要申请人主要有美国的Intel公司、韩国的三星、荷兰的ASML等,Intel公司作为行业巨头,申请量遥遥领先,处于绝对领先的地位,在排名前10位申请人中,美国、韩国、日本、中国大陆和中国台湾均分别有2位申请人,中国企业特别是中芯国际也开始占据一席之地。

3 技术发展趋势预测

多重图形技术是从193nm ArF光刻工艺向极紫外(EUV)光刻工艺过渡进程中不可或缺的技术。四重以上的纯间距分离图形技术因成本考量和对准精度问题,难以成为工业界的主流选择;纯间距分割多重图形技术配合侧墙工艺改进技术、切割图形技术可实现高精准度光刻,将是EUV技术或其他替代技术完全成熟之前实现22nm以下设计尺寸的主要解决方案,其中,三重纯间距分割技术可以同步获得不同尺寸的图形,具备独特的优势;间距分离分割混合工艺结合了纯间距分离技术和纯间距分割技术的优点,因其高自由度和特征尺寸的精确度,具有广阔的发展前景。

需要指出的是,极紫外线(EUV)光刻技术仍被认为是将来最有竞争力的技术方案,对EUV光刻技术的研究仍在持续,一旦在光源强度、掩模版制作、缺陷控制等方面实现突破,将释放巨大的潜力,将集成电路制造技术推进一个新时代。

参考文献

[1]洪中山,吴汉明.多重图形技术的研究进展[J].微纳电子技术,2013,(10):656-661.

[2]李长河,丁玉成.先进制造工艺技术[M].北京:科学出版社,2011.

[3]何杰,夏建白.半导体科学与技术[M].北京:科学出版社,2007.

(作者单位:国家知识产权局专利局专利审查协作天津中心)