TMS320C6678中的高速串行接口RapidIO研究

卢建章,刘洋

(1.中航工业雷华电子技术研究所,无锡 214063;2.江南计算技术研究所)

TMS320C6678中的高速串行接口RapidIO研究

卢建章1,刘洋2

(1.中航工业雷华电子技术研究所,无锡 214063;2.江南计算技术研究所)

本文从嵌入式多核处理器之间高速数据通信的应用出发,结合对TI的TMS320C6678多核DSP的认识,开展了对RapidIO(SRIO)接口协议和TMS320C6678 SRIO模块结构的研究。并在此基础上,工程实现了TMS320C6678片间SRIO通信的详细配置过程,并对其通信性能进行了评测分析,为多核DSP系统级通信的设计提供了一定的参考。

TMS320C6678;RapidIO;处理器间通信

引 言

为了实现高性能的嵌入式系统,由Mercury和Freescale共同研发的RapidIO互连技术发展起来,其具有高传输效率、低系统成本和高可靠性等特点,RapidIO协议为嵌入式系统各器件之间提供高带宽、低延时的数据传输,并且可以支持板到板、芯片到芯片间的通信。

2010年11月,TI公司发布了KeyStone结构的8核DSP处理器TMS320C6678,其每个C66x内核主频最高达1.25 GHz,可以提供每秒高达40 GB MAC定点运算和20 GB FLOP浮点运算能力[1];该芯片中集成了一个兼容于RapidIO互联规范REV2.1.1的4通道的SRIO模块,可配置成1x, 2x, 4x模式,每通道支持1.25 Gbps、2.5 Gbps、3.125 Gbps和5 Gbps的传输速率[1]。SRIO的数据格式默认采用大端格式,支持8b/16b的设备ID、组播ID,同时额外支持错误管理、阻塞控制,为实现系统级的互联提供了可行方案。适用于诸如雷达信号处理等对定浮点运算能力以及大数据通信有较高要求的超高性能计算应用。

基于以上分析,本文针对TMS320C6678多核处理器,首先介绍了SRIO的传输协议,分析TMS320C6678的SRIO收发模型和配置过程,并对其传输带宽进行了评测,为多处理器系统的设计提供了一定的参考。

1 SRIO协议简介

RapidIO技术是一种基于协议包格式的互联技术,在TMS320C6678芯片手册中,通常把RapidIO称为SRIO,为DSP之间提供一种高带宽、低延迟、低系统成本的通信,是系统互连的最佳选择之一,下面分析SRIO的协议构成。

1.1 SRIO协议概述

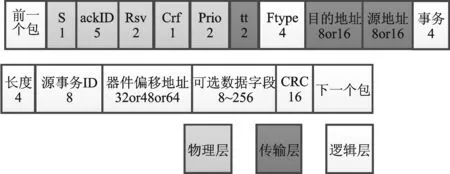

图1 SRIO协议层次结构图

为了满足灵活性和可扩展性的要求,SRIO协议可分为三层:逻辑层、传输层和物理层,如图1所示。逻辑层位于顶层,定义了在应用程序中如何通信、包格式、为端点器件发起完成事务提供信息,它支持DirectI/O、消息传递和全局共享存储。传输层位于中间层,数据传输的地址空间和传输包所需的路由信息由它来定义。物理层位于底层,定义了设备级接口、报文传输、流量控制、电气特性、底层错误处理等[2]。

1.2 SRIO协议包

SRIO是基于包交换的数据传输协议。一个传输包由属于逻辑层、传输层和物理层的数据域组成。逻辑层域由包头(定义入口类型)和有效载荷(即数据)组成。传输层域从物理布局上来说,在某种意义上是独立的,由发送和接收设备的源ID号和目的ID号等组成。物理层在物理接口上是独立的,包含优先级、信息确认和错误检测域。SRIO协议包如图2所示。

图2 SRIO协议包

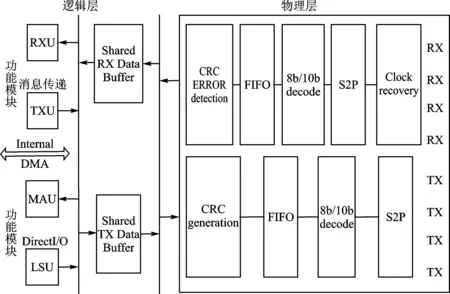

图3 SRIO的数据流图

数据包最外层为物理层字段,最内层为逻辑层字段,中间的为传输层字段,图2中的数字为字节数。其中S字段用来表示该包是一个数据包还是一个控制符号。ackID是链路级包鉴定符,即包序列号,每发送一个包,ackID加1。Prio为优先级字段,tt、目的地址和源地址表示传输地址的类型,即包接收和产生地址是8位还是16位。Ftype代表被请求的事务类型,不同类型的SRIO包协议也略有不同。长度为编码后的事务长度,SRIO最多允许256个待完成事务。在源事务ID之后是器件偏移地址。后面接着有效数据载荷,再以16位循环冗余校验码(CRC)结束,接收端通过CRC校验码来判断这个包是否正确。

2 TMS320C6678中SRIO实现

TMS320C6678是一款处理能力很强的新型高性能多核DSP,相比于之前的芯片,集成了丰富的外设,如PCI总线端口、千兆以太网端口、64位无缝外部存储器端口、HyperLink端口等,最重要的是增加了对SRIO支持的模块。

2.1 SRIO模块简介

TMS320C6678芯片的SRIO接口是一个外部驱动的从设备模块,同时能够在DSP芯片内作为一个主设备。这意味着外部设备可以根据需求传输(突发写入)数据到DSP内部,而无需向CPU发送中断或依赖DSP 芯片的EDMA资源。这种机制既降低了系统的中断个数,又减少了与只读外设的握手操作,同时还释放了 EDMA资源以便其他任务使用。

SRIO外设模块的数据流如图3所示。当接收数据包时,高速数据包在物理层依次进行时钟恢复、串并转换、8b/10b解码,并将之缓存在各个端口的缓存区,最后进行 CRC 错误检测;相反,当发送数据包时,数据包首先进行 CRC 生成,经过各个端口的缓存区后依次进行8b/10b编码、并串转换,最后到达发送端口。数据包在逻辑层与物理层间通过发送共享缓存区和接收缓存区进行过渡,最后到达逻辑层的数据包,整个包已被解码,负载数据已被缓存,根据接收的数据包类型的不同,包的进一步操作通过功能模块来实现,其中LSU(Load/Stone Unit)负责控制发送DirectI/O模式的数据包,MAU(Memory Access Unit)负责控制接收DirectI/O模式的数据包,TXU负责控制发送消息传递模式的数据包,RXU负责控制接收消息传递模式的数据包。这4个单元通过内部DMA与DSP芯片的存储器进行通信,通过缓存区和接收发送端口与外部设备通信。

2.2 SRIO操作实现

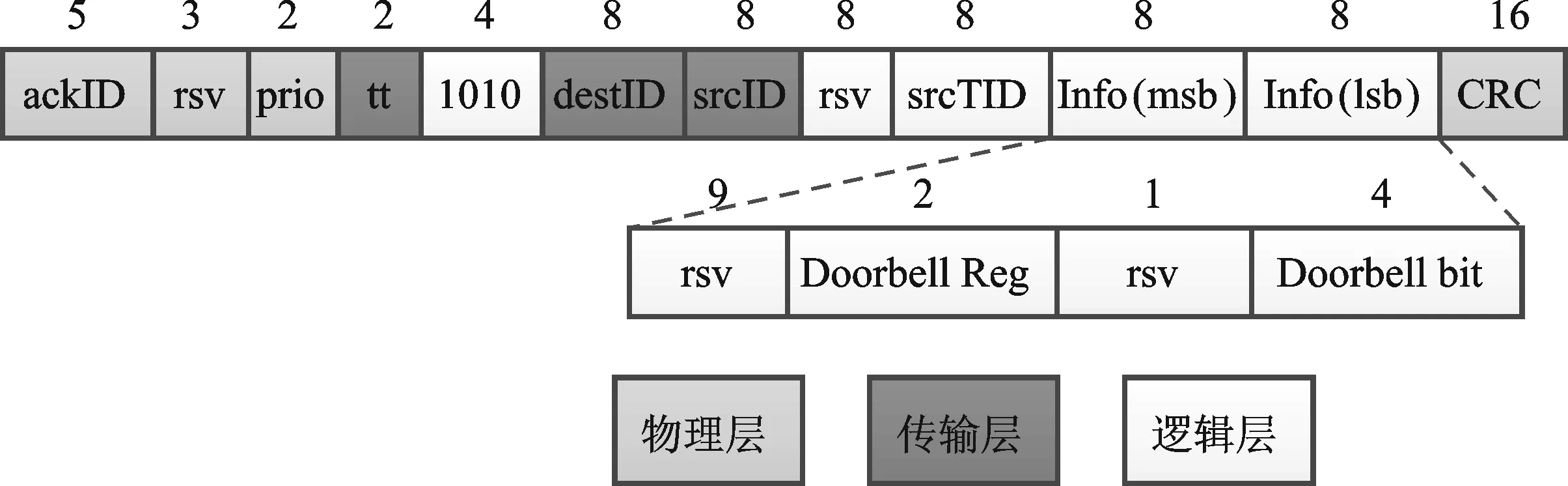

SRIO操作是通过包的传输完成的。在C6678中关于SRIO的操作主要分为DirectI/O和Doorbell这两大类。通过对LSU寄存器进行配置,从而完成操作。DirectI/O包括了NREAD、NWRITE、NWRITE_R、SWRITE、Maintenance Read和Maintenance Write这几种协议。对于DirectI/O而言,数据传输和DMA传输是结合的。此DMA为SRIO模块中的内部引擎,当发起SRIO操作时,DMA将会自行启动。DirectI/O操作分为主、从两种模式。当DSP工作在主模式下时,DSP需要知道外部相连器件的ID号以及存储器地址映射情况,从而发起读/写操作。若DSP工作在从模式下,DSP无需知道其他外部芯片的逻辑地址情况,读写操作都由主设备发起,通过DMA完成。Doorbell 协议包不包含数据负载,是一种用于器件间响应中断的协议,如图4所示。

图4 Doorbell包结构

在Doorbell操作中,存在着一个Drbll_Info的结构,Drbll_Info分为16位,由Doorbell的发送方置位。Doorbell的接收方可以在中断服务程序中,读取ICCR寄存器的值,此时ICCR中的值会根据 Drbll_Info的值,在相应的位上进行置位。这样通过 Drbll_Info便可以发送不同的指令。

TMS320C6678的SRIO模块设计以寄存器为基础,通过调用TI公司软件开发工具PDK中的底层库(CSL)驱动和SRIO模块驱动进行程序设计。SRIO模块的驱动程序初始化按以下步骤设置[3-4]:

① 端口使能:使能内部发送(LSU,TXU)与接收(MAU,RXU)模块。

② SerDes初始化:参考时钟以及传输速度初始化,相连器件间需要配置相同的参考时钟,传输速度有1.25 Gbps、2.5 Gbps、3.125 Gbps和5 Gbps。

③ 传输模式初始化:Lane可以配置为1x、2x或4x,设置锁相环PLL和设备ID。

④ 中断初始化:初始化Doorbell中断,将其映射到核内中断向量上。

按照上述步骤完成配置后,在SRIO接收到Doorbell中断时,接收DSP即跳入中断服务程序,完成门铃响应。

3 性能测试

本节对SRIO传输的性能进行实测评估,并提供在不同的操作条件下获得的性能测试数据。大部分测试是在最理想的测试条件进行,以评估可以获得的最大吞吐量。处理器运行的频率设置为1 GHz,DDR配置成64位,位宽1333 M,采用的编译环境是TI公司的CCSv5.0。

图5 SRIO的传输带宽

图5表述SRIO在不同类型的存储空间之间的传输速率随着数据块的增大,一直呈现上升趋势。

表1是DSP核以DirectI/O模式的SWRITE方式通过SRIO从本地LL2、SL2和DDR3分别访问远端LL2、SL2和DDR3,每次发送数据量为8 KB,发送多次取平均所得的传输带宽。由于SRIO本身具备硬件纠错功能,当检测到数据传输错误后会自动重传,造成带宽的损耗,另外,背板的硬件电气特性也会直接影响到实测的带宽,这些因素均会造成实测带宽与理论带宽的差距。

表1 DSP核通过SRIO实现8 KB数据传输带宽

结 语

[1] Texas Instruments Inc.Multicore design overview,2011.

[2] Sam Fuller.RapidIO:The embedded system interconnect[M].Hoboken:John Wiley&Sons,2005.

[3] Texas Instruments Inc.TMS320C6678 data manual,2011.

[4] Texas Instruments Inc.KeyStone Architecture Serial RapidIO User Guid,2012.

卢建章(工程师),主要研究方向为雷达信号处理、嵌入式信号处理系统;刘洋(工程师),主要研究方向为信息安全。

Research on High-speed Serial Interface RapidIO in TMS320C6678

Lu Jianzhang1,Liu Yang2

(1.AVIC Leihua Electronic Technology Research Institute,Wuxi 214063,China;2. Jiangnan Computing Technology Research Institute)

Based on the application of high-speed data communication between embedded multi-core processors and the knowledge of TMS320C6678 multi-core DSP,the research on RapidIO interface protocol and TMS320C6678 SRIO module structure is carried out.The detailed configuration process of SRIO communication between TMS320C6678 chips is achieved,and its communication performance is analyzed and evaluated.It provides some reference for multi-core DSP system-level communication design.

TMS320C6678;RapidIO;inter-processor communication

TN915.04

A

�士然

2017-02-13)