光传输设备中并行总线转SPI的设计

熊建新+王元+郑鹏

摘 要:文章提出并論证了在光传输设备中利用SPI总线替代并行地址数据总线的设计,利用SPI总线实现设备板卡间通信,极大地简化了设备的背板及各单元板的硬件设计,是一种简易、可靠、稳定的传输方式。

关键词:SPI;并行总线;光传输

传统的光传输设备中多采用背板和板卡的结构,根据各功能模块各板卡具有不同的功能,如SDH光传输设备采用的控制板、光板、以太网板、2 M板等各单元电路板,均通过背板进行总线连接。因为各单元电路采用了对应的专用集成电路,控制盘对各单元板业务功能的初始化及功能控制是采用并行控制总线来完成的,这些总线包括各板卡间的地址、数据总线和控制信号等,由此带来背板的布局连线极为困难复杂。采用SPI总线替代8位、16位或32位的并行控制总线后大大简化了背板的设计难度,并在一定程度上增加了设备的可靠性和稳定性[1]。

1 系统总线设计

控制板CPU与各业务板之间通过4根信号线连接,总线设计如图1所示。控制板CPU通过4根SPI串行总线与各业务板连接,其中MISO,MOSI,SCLK共用,通过片选信号CS将各业务板区分开来,各业务板通过SPI总线与控制板CPU通信,并将各总线命令进行串并转换,与业务板专用芯片进行实时控制管理。由图可知控制板CPU作为SPI总线的主机,各业务板FPGA作为SPI总线的从机。SPI信号线详细定义如表1所示。

2 控制板CPU总线设计

控制板CPU选用NXP公司的LPC1768,LPC1768是一款基于ARM Cortex-M3内核的微控制器,操作频率可达100 MHz,具有三级流水线和哈弗结构[2]。控制板CPU SPI管脚分布为:P0.16为控制板CPU的CS信号,直连控制板的FPGA IO管脚;P0.15为共用的SCLK管脚,P0.17为共用的MISO,P0.18为共用的MOSI,再选用LPC1768的其他几个IO口作为其他几个业务板的CS片选信号,分别作为每一块板的读写控制。

控制板CPU定义SPI总线时序如图2所示。

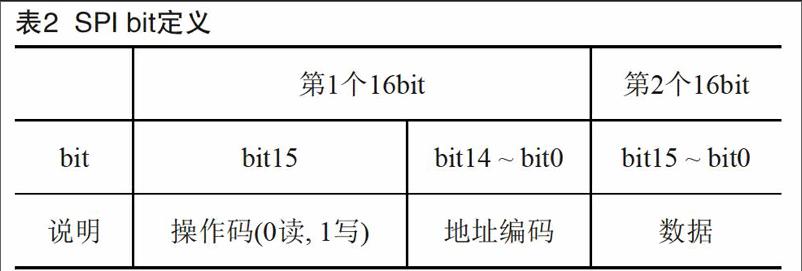

1次片选有效的读/写周期内,有32个时钟。前16个时钟为操作+地址,后16个时钟为数据。每个16 bit中,MSB在前,LSB在后。每次读写操作之间CPU在给完地址信息后预留1 ms的间隔时间,用来给FPGA完成缓存读写使能信号、地址信号,CPU数据给出后,FPGA继续缓存上面保存的地址信号的数据,最后由FPGA全部给出到专用芯片。详细定义如表2所示。

为避免SPI总线竞争,使用互斥信号量对SPI总线进行保护操作,在CPU访问SPI总线之前,首先获取互斥信号量,操作完毕之后再释放互斥信号量。内部接口具体函数如表3所示。

3 业务板FPGA总线设计

本设计中业务板采用XILINX公司目前主流通用的Spartan6系列芯片XC6SLX100-FGG676实现SPI转并行总线的功能,已通过板级验证。编程语言采用业内共用的VHDL硬件逻辑语言[3]。

业务板主要功能是通过背板接收控制板CPU的SPI读写信号,实时地转换为对本电路板的专用芯片的读写控制。具体设计流程为:FPGA在SPI时钟信号SCLK上升沿下对CS进行判断,当CS为0时,缓存MOSI信号,最高位为地址信号的第16位,判断CPU是读或写操作。

当最高位为0,CPU对业务板进行读操作。FPGA先缓存SPI的15位地址总线ADDR,然后在SPI地址总线和数据总线的1 ms间隔周期内对专用芯片进行读操作,读出该芯片地址ADDR的数据,在SPI数据位到来的时候依次给出16位数据,注意MSB先给出,LSB后给出。

当最高位为1,CPU对业务板进行写操作。FPGA先将CPU给过来的地址数据总线全部缓存,然后在CPU写操作完成后对专用芯片进行写指令,将缓存的地址、数据依次写入专用芯片。业务板FPGA总线设计如图3所示。

4 结语

本文针对常用的光传输设备设计过程中背板控制总线的处理,提出了一种采用SPI串行总线替代并行总线的设计,并对设计过程进行了详细的阐述和论证。事实证明假设设备共有6块业务板,每块业务板采用的最低8位的地址数据总线,每块业务板需要19根总线,6块业务板则需要114根总线,采用SPI总线后只需要10根总线即可。这种设计方法极大地简化了背板的设计难度,提高了设备的稳定性和可靠性,具有很好的使用价值。

作者简介:熊建新(1983— ),男,湖北黄冈,硕士研究生,工程师;研究方向:光通信开发。

[参考文献]

[1]刘敏,陈金鹰.基于FPGA的并行数据转SPI接口设计[J].电视技术,2012(5):31-32.

[2]李大江,崔建明.一种基于FPGA的可配置SPIMaster接口设计实现[J].电子技术应用,2010(10):60-62.

[3]XILIN X.DS160:Spartan-6 family overview[EB/OL].(2010-11-05)[2017-06-25]. http://www.xilinx.com.

Abstract: This paper presents and demonstrates the use of SPI bus instead of the parallel address data bus in the optical transmission equipment. The SPI bus is used to realize the communication between the devices boards, which greatly simplifies the hardware design of the backplane and the unit board, is a simple, reliable, stable transmission mode.

Key words: serial peripheral interface; parallel bus; optical transmission