一种S波段高线性度下变频模块的设计

闫 超,赵家敏,姚武生

(中国电子科技集团公司第三十八研究所,合肥 230088)

一种S波段高线性度下变频模块的设计

闫 超,赵家敏,姚武生

(中国电子科技集团公司第三十八研究所,合肥 230088)

描述了一种应用于S波段接收通道的高线性度下变频模块设计,针对模块的增益、线性度、杂谐波抑制等关键技术指标进行了详细的理论和仿真分析,并硬件实现了该模块。该模块主要采用SMD器件,包括有源混频器、高OIP3放大器和LC滤波器等。测试结果显示,模块增益为21 dB,杂谐波抑制度大于65 dBc,对特定频点的抑制度大于40 dBc,IIP3大于24 dBm,表明该模块满足指标要求,能够充分适应高性能接收通道的应用要求。

下变频模块;增益;线性度;杂谐波抑制

0 引 言

现代通信、雷达接收机大多采用超外差接收体制,下变频器是超外差接收机的关键组成部分。下变频器将适于传输的射频信号变换为较低的频率进行处理。下变频器的性能直接影响到接收机的性能指标[1],而其中的线性度、杂谐波抑制度、通道增益则是下变频模块的关键指标。

本文介绍了一种高线性度S波段下变频模块,模块将S波段射频信号变换至260~460 MHz中频,且具有高线性度、较好的杂谐波抑制度等特点。文章重点分析了关键指标的电路实现方法,并进行了测试,结果表明模块的性能完全满足指标要求。

1 下变频模块技术要求

S波段下变频模块的主要技术指标:

(1) 中频:260~460 MHz;

(2) 增益:G≥17 dB;

(3) IIP3:≥24 dBm(增益G=16 dB时测试);

(4) 杂谐波抑制度:≥60 dBc;

(5) 中频抑制:≥38 dBc(输出频率为220 MHz和500 MHz时)。

2 电路结构与设计方案

2.1 电路结构

下变频模块主要由低通滤波器、带通滤波器、功率合成/功分器、混频器、数控衰减器、放大器、耦合器和功率检测电路构成,电路结构示意图如图1所示。射频信号经低通滤波器滤除带外噪声和干扰后进入混频器。混频器将射频信号下混频至260~460 MHz的中频,再经过一级低通滤波器滤除谐波及杂散信号。中频信号通过功分器将功率一分为二,二路分别放大再合成,以提高输出功率。最后将已放大的中频信号进一步滤波后输出,模块内的功率电路检测输出功率大小。系统监控根据输出功率的大小控制数控衰减器的衰减码,从而调节电路的增益。

图1 电路结构示意图

2.2 关键技术指标设计分析

2.2.1 线性度、增益设计方案

在射频电路设计中,通常采用IP3(third-order intercept point,三阶交调截取点)指标来衡量系统的线性度。其定义为系统的三阶非线性输出与一阶线性输出相等时的输入或输出功率,分别被称为输入三阶交调截取点IIP3(input IP3)和输出三阶交调截取点OIP3(Output IP3)。[2]

设一个非线性系统的传输函数为

(1)

其中k1、k2、k3分别为系统的电压增益、二阶、三阶非线性项系数。当同时输入两个频率相近的信号Acosω1t、Acosω2t时,系统将产生多个不属于输入信号谐波的频率分量,即为两个信号的交调分量。

(2)

二阶交调项为

(3)

三阶交调项为

(4)

由式(2)、(4)可知,基频与信号幅度A成比例增加,而三阶交调项与A3成比例增加。所以,随着输入信号幅度的增加,基频与三阶交调项必相交于一点,该点即为三阶交调点[3],如图2和式(5)所示,其中G为系统增益。

(5)

图2 三阶交调截取点示意图

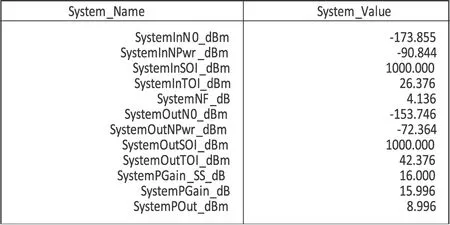

由上述理论可知,在射频电路中,非线性的有源器件对系统的线性度影响较大,如有源混频器、放大器[4],因此需要依托仿真软件和理论计算对有源器件进行精心选择与对比,才能保证链路性能。在本设计中,混频器选用IDTF1763有源混频芯片。该芯片增益为11.7dB,OIP3可达45dBm,二次谐波及交调抑制可达60dBc以上。同时,为了保证系统增益和线性度,放大器的选择也至关重要,电路选用HXG-122放大模块。该模块的OIP3高达47dBm,放大增益为16dB。选定器件后,利用ADS仿真软件对该模块的射频链路预算做仿真分析,重点关注整个链路的增益、IIP3、谐波抑制度等指标。链路预算仿真模型和仿真结果如图3、图4所示。

图3 下变频模块链路预算仿真

图4 下变频模块链路预算仿真结果

图4中“SystemPGain_dB”项为链路的增益,“SystemInTOI_dBm”项为链路的IIP3指标。由此可知,模块的增益约为21.4 dB,可以满足系统指标要求,此时的IIP3约为21.5 dBm。对于链路增益G=16 dB时的IIP3指标,需要将数控衰减器的衰减量调节至5.5 dB后,再次对图3的模型进行仿真,仿真结果如图5所示。可知,当链路增益约为G=16 dB时,下变频模块的IIP3指标为26.4 dBm,可以较好地满足系统指标。

图5 增益为16 dB时下变频模块链路预算仿真结果

电路中使用的放大器虽然线性度较高,但是其输出1 dB压缩点(P-1dB)为23 dBm。当射频输入信号达到3 dBm时放大器进入饱和状态,若输入功率继续增大,系统的放大增益、输出功率和杂谐波抑制则无法保证。因此,本电路中采用双管合成的放大形式,以此在保证电路线性度指标的同时提高输出功率。功率合成采用双路等功率同相合成方式,设两路的功率及相位分别为P1、P2和θ1、θ2,则合成功率为

(6)

当P1=P2、θ1-θ2=0时,Pout=2P1=2P2合成效率最大[5],而且当某一支路失效时整个模块的输出功率会下降到原先的四分之一,但模块仍可工作,在一定程度上提高了系统的可靠性。

2.2.2 杂谐波抑制设计

作为一种非线性器件,混频器在产生有用的中频信号时还会产生谐波和交调分量。这些频率分量一般表示为

mRF±nLO

(7)

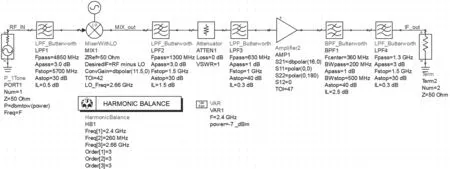

在实际应用中,一般通过选用性能良好的中频滤波器来抑制谐波和交调。下变频模块的二次谐波范围为520~920MHz,三次谐波780~1 380MHz。本电路选用的中频滤波器主要性能指标为中心频率为360MHz、带宽200MHz、220MHz以下和500~1 000MHz频段的抑制度≥40dBc。因此,滤波器对二次谐波的抑制可以达到40dBc。在设计时将后端放大器的输出功率回退10dB使用,远离放大器的P-1点。电路对二次谐波的抑制可增加20dB[6],故模块的二次谐波抑制度可以满足≥60dBc的要求。同理,本模块对三次谐波的抑制度也可以达到60dBc以上。通过仿真计算可得,本模块中频通带内最低次交调为5RF-4LO,中频带外最低次交调为2RF-LO。仿真计算结果如图6所示。

图6 交调仿真计算结果

根据混频器资料,混频器对带内5RF-4LO交调的抑制度在60dBc以上,混频器与各级滤波器对带外2RF-LO交调的抑制度也可达到60dBc以上。混频器中频输出端对本振、射频信号的最小抑制度分别为27、38dBc,而模块中各级低通和带通滤波器对本振和射频的抑制均在40dBc以上。因此,模块对本振和射频信号的抑制可以满足60dBc的指标要求。针对220MHz和500MHz中频信号,中频带通滤波器对它们的抑制度均在40dBc以上,可以满足38dBc抑制度的要求。使用ADS软件中的谐波平衡仿真控件对下变频模块的杂谐波抑制情况进行仿真,仿真模型和结果如图7、图8所示。下变频模块将S波段的信号搬移至260MHz中频,并且整个射频前端对于各次谐波、本振和泄露的射频信号有很好的抑制作用。

图7 下变频模块杂谐波抑制仿真模型

图8 下变频模块杂谐波抑制仿真结果

除了在电路设计和器件选型上消除杂谐波的影响,电路结构和布线形式也需要考虑。放大器区域使用金属隔墙与前端小信号部分隔离,防止不同频率的信号互相串扰。同时,为了提高接地及散热效果,微带板背面大面积接地并钎焊在金属垫块上。此外,中频带通滤波器在安装时也要保证与垫块接触良好,以防出现因接地不良而导致滤波器响应变差。

3 电路测试结果

本电路模块的实物如图9所示,模块体积紧凑、结构简单,便于安装和测试。模块的各项实测指标如表1所示,增益、IIP3和杂谐波抑制度均较好地满足技术指标。

图9 下变频模块实物图

表1 下变频模块测试指标

4 结束语

本文介绍了一种S波段高线性度下变频模块的设计方案,并对该方案做了详细的理论与仿真分析。通过合理选择器件和优化电路形式,较好地提高了模块的IIP3性能,同时提高了模块增益和杂谐波抑制度。模块在260~460 MHz的带宽内增益大于22 dB,IIP3达到25 dBm,杂谐波抑制度大于65 dBc,而且对带外特定频率信号的抑制度达到45 dBc以上,完全满足性能指标要求。现阶段该下变频模块已投入使用180余件,实际使用效果完全验证了本设计的有效性。

[1] 林燕海,詹铭周,徐锐敏. Ka频段下变频模块设计[J]. 微波学报,2010(S1):375-377.

[2] 林敏. CMOS射频前端电路设计中的低噪声、高线性度研究[D].北京:清华大学,2004.

[3] 周苏萍.基于P和L频段射频前端关键电路研究[D].杭州:杭州电子科技大学,2011.

[4] 何俊岑,侯智鹏,周俊.基于LTCC的小型化宽带变频组件[J].电子信息对抗技术,2015(3):59-62.

[5] 王延恩.微波固态功率合成电路设计[D].北京:中国地质大学,2012.

[6] 李文广,吴国安.射频功放的非线性分析与线性化技术[J].舰船电子工程,2006(6):134-136.

Design of an S-band high-linearity down conversion module

YAN Chao, ZHAO Jia-min, YAO Wu-sheng

(No.38 Research Institute of CETC, Hefei 230088)

A high-linearity down conversion module is designed for the S-band receiving channel. The key technical specifications such as the gain, linearity as well as spurious and harmonic wave suppression are simulated and analyzed theoretically in detail with the hardware implemented. The module mainly adopts the SMD devices, including the active mixer, the high-OIP3 amplifier and the LC filter. The test results show that the gain of the module is 21dB, the spurious and harmonic wave suppression is greater than 65dBc, the suppression of the specific frequency is more than 40dBc, and the IIP3 is greater than 24dBm, indicating that the module meets the requirements, and can fully meet the application requirements of the high-performance receiving channel.

down conversion module; gain; linearity; spurious and harmonic wave suppression

2017-03-07;

2017-03-20

闫超(1988-),男,助理工程师,硕士,研究方向:雷达射频前端;赵家敏(1985-),男,工程师,博士,研究方向:雷达射频前端和宽带功率放大器;姚武生(1968-),男,研究员,硕士,研究方向:雷达收发系统设计。

TN850

A

1009-0401(2017)02-0055-05