一种基于基准电压的高速IO

许 迪 孙长江 罗尧宇

(深圳市国微电子有限公司,广东 深圳 518057)

一种基于基准电压的高速IO

许 迪 孙长江 罗尧宇

(深圳市国微电子有限公司,广东 深圳 518057)

本论文提出一种通过基准电压来减小延时的IO设计方法,设计出具高速特性的IO模块,从而满足高速SRAM产品的使用需求。该模块主要的设计思路为:通过基准电压提供一个中间态电压,通过中间态电压快速响应,减小IO的延时。通过HSPICE仿真表明,这款电路能满足200M hz SRAM需求,并通过流片,验证此结构是可行的。

IO;高速;翻转速度

1 引言

为满足高端存储器的芯片的高速时序要求,其对IO的延时亦有较高的要求。一般来讲,适当地提升驱动能力可以有效减少IO的延时。但是提高驱动能力会带来一系列副作用,如更高的功耗,更大的地弹及噪声,需要占用更大的面积。本文中设计出一种基于基准电压的IO结构,利用基准电压使IO在电平转换的时候进行高速翻转,在尽量减小驱动能力的同时,可以满足高速的需求。

2 总体电路

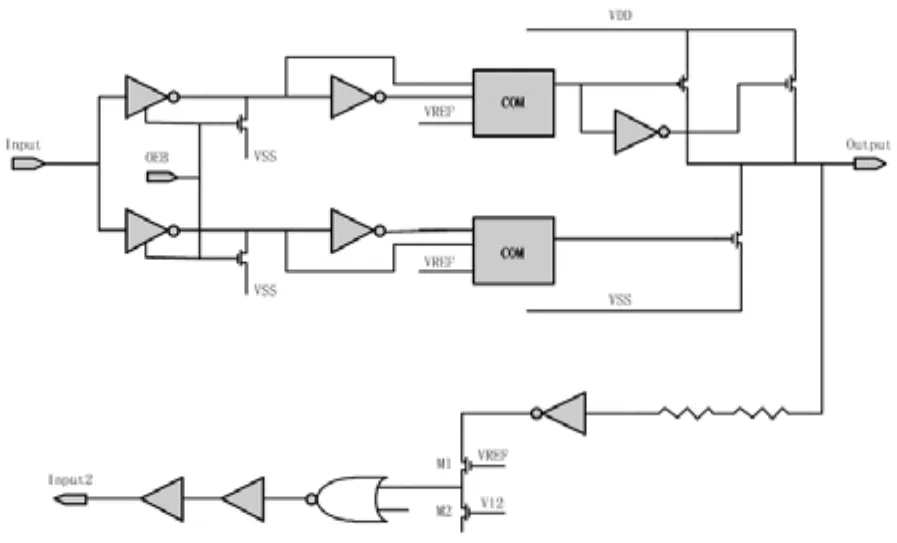

总体电路可以分为两部分,一部分为IO模块,另一部分为带隙基准。其中IO模块提供高低电平的转换以及ESD保护。带隙基准模块为IO提供一个基准电压,协助IO进行高速翻转。其中带隙基准为常用结构,在此文中不再详细介绍。本文重点介绍IO模块部分,其中可以分为输入部分以及输出部分。其总体结构图如图1所示。

图1 总体IO结构

3 输入部分

输入部分主要完成将外部信号输入到芯片内部的任务,同时将外部的信号电压转换为内部的信号电压。在本论文中,外部信号的电压为3.3V/2.5V,内部信号的电压为1.2V。电压的转换主要由两个N管构成,如图2所示,其中M 1管的栅极接基准电压,为2V,M 2管的栅极接1.2V电压。

当输入信号为高时,M 1漏极为3.3V,M 1管导通,由于M 2管宽长比远远小于M 1管宽长比,故M 2的导通电阻比M 1的导通电阻大很多,因此其分压较大,但是由于M 1管的栅极接VREF电压,为保证其导通,M 1的源极最高电压不能高于VREF-Vthn。至此,输入信号为高时的电压转换完成[1]。

当输入信号为低时,M 1的漏极为0V,由于M 1管栅极接VREF电压,M 2管的栅极接1.2V电压,处于打开状态,故M 2的漏极电荷会通过M 1管和M 2管释放出去,迅速拉低到0V。至此输入信号为低时的电压转换完成。

图2 输入部分

4 输出部分

输出部分主要完成将内部信号输出到芯片外部的任务,同时将内部信号的电平转换为外部信号所需的电平。在输出部分,主要包含两大部分,分别为电压转换部分及驱动部分。其中电压转换部分将内部1.2V电压转换为2.5V/3.3V电压,驱动部分主要增强输出的驱动能力,以满足驱动大型负载的要求。

图3 输出部分

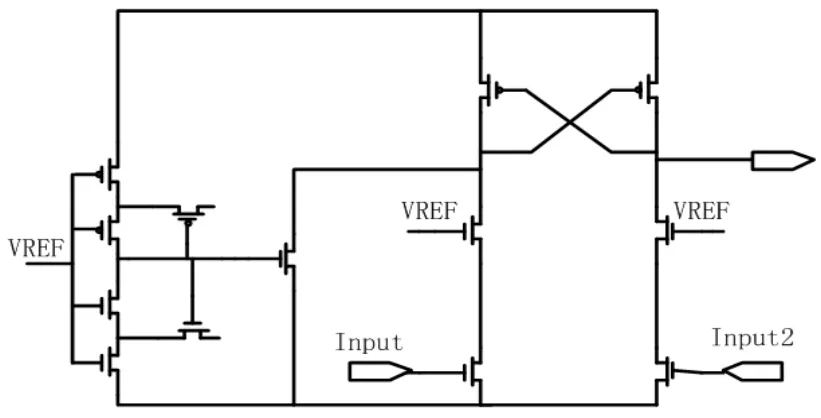

电压的转换部分主要由一个带有基准电压的比较器完成,其结构如图4所示,比较器的两端由N管组成,并通过上面的N管组成cascode结构,提高放大增益倍数,在N管的上面是由P管组成的正反馈系统,由于正反馈的作用,当两个P管的漏极电压稍微发生差分变化时,会将差分变化迅速放大。因此比较器的响应速度非常高[2]。

通过比较器之后的电压为2.5V/3.3V,用此电压来进行驱动部分的驱动管开关。当输入电压为高时,上面P驱动管的栅极电压被拉为低电压,P驱动管打开,上面N驱动管的栅极电压被拉为高电压,N驱动管打开,两个管子同时对输出充电,下面的N驱动管的栅极电压被拉为低,N驱动管关闭,因此输出电压将被拉高。当输入电压为低时,情况正好相反,上面P驱动管的栅极电压被拉为高电压,P驱动管关闭,上面N驱动管的栅极电压被拉为低电压,N驱动管关闭,下面的N驱动管的栅极电压被拉为高,N驱动管打开,对输出放电,因此输出电压将被拉低。

图4 比较器

5 仿真结果

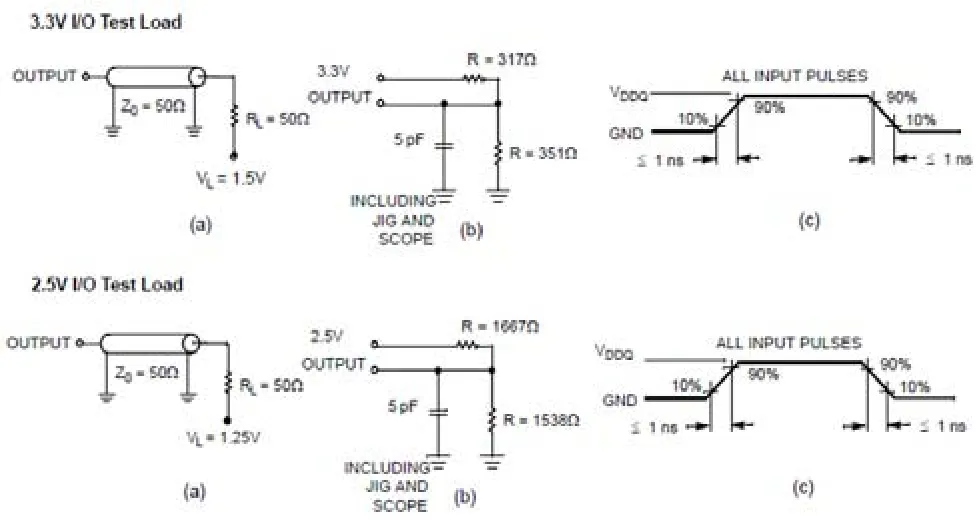

本结构通过版图设计后,提取带有寄生参数的后仿真网表,以求更加精确的仿真结果。其负载情况如图5所示。

图5 负载模式

输入部分的负载:0.1pF

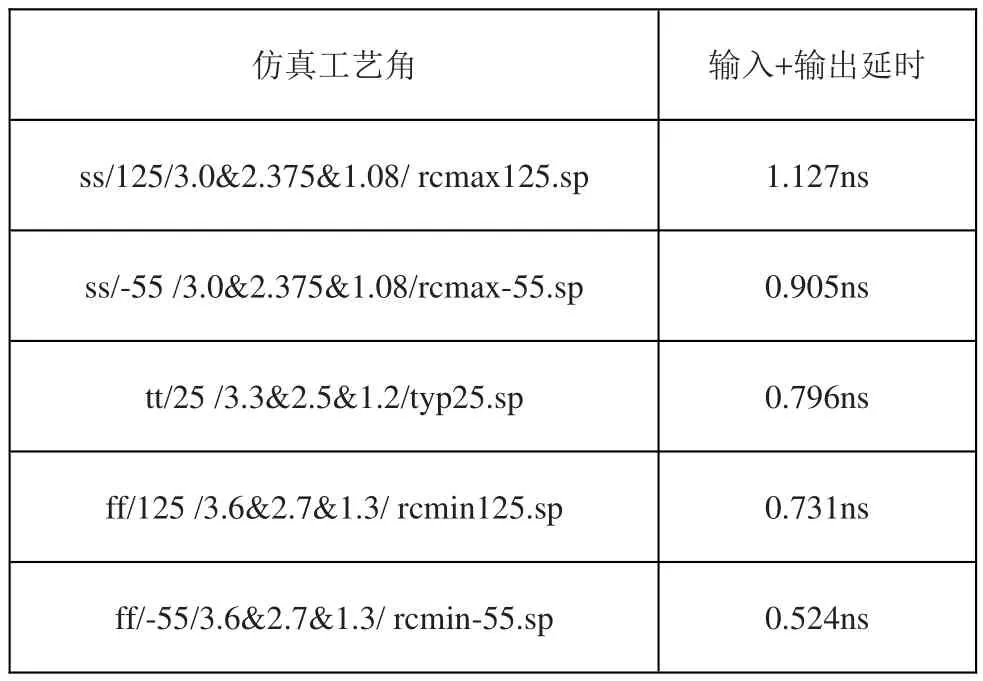

表1 (vref2=2V输入:1.2V/250MHz/tr=500ps)

表2 (vref2=2V输入:1.2V/250MHz/tr=500ps)

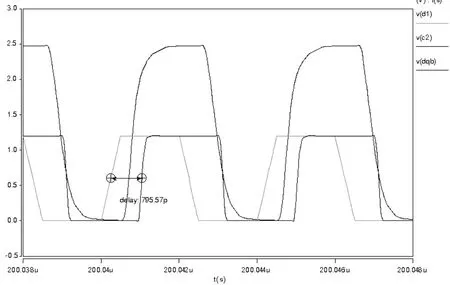

以下为延时波形示意图,工艺角为tt。

图6 3.3V电压波形

图7 2.5V电压波形

从仿真结果可以看出,IO基本可以满足1.2ns以内的延时需求。

6 结论

本论文通过提出一种基于基准电压的IO结构,分析其输入部分及输出部分的工作原理,以降低IO的延时,通过此种结构,可以降低IO的延时,为SRAM等产品提供更大的时序空间。

[1]Behzad Razavi.模拟CMOS集成电路设计[M].北京:清华大学大学出版社,2005.

[2]Phillip E.Allen,DouglasR.Holbeng.CMOS模拟集成电路设计[M].北京:电子工业出版社,2007.

Design of the High Speed IO Based on Bandgap Reference Voltage

Xu Di Sun Changjiang Luo Yaoyu

(Shenzhen StateM icroelectronicsCo.,Ltd.,Shenzhen 518057,Guangdong)

This paper introducesa designmethod through the bandgap voltage to reduce the delay of IO,presentsa design of IO w ith high speed,whichmeets the requirementof high speed SRAM products.Themain design idea of thismodule is:With bandgap supplying am iddle stage voltage,themodule can response fast,which reduces the delay of IO.Through the HSPICE simulation results,the demand of 200Mhz SRAM can be satisfied by this circuit,and themodulehasbeen proved reliableby taping out.

yword】 IO;high speed;flip speed

TN432

A

1008-6609(2017)06-0045-03

许迪(1988-),男,辽宁大连人,硕士,工程师,研究方向为模拟集成电路设计。