跨平台武器系统总线同步时钟发生技术研究*

周玉清, 薛小乐, 黎玉刚, 骆 盛

(中国兵器工业第203研究所, 西安 710065)

跨平台武器系统总线同步时钟发生技术研究*

周玉清, 薛小乐, 黎玉刚, 骆 盛

(中国兵器工业第203研究所, 西安 710065)

提出一种新颖的跨平台武器系统总线同步时钟发生技术,该技术采用相位延迟、中断窗口等方法,降低了传统直接触发技术带来的误差,提高了总线同步时钟发生器的容错性以及武器的安全性。并且,把该技术用于某武器系统的时钟同步系统中,从而验证了方法的可行性和有效性。

通信总线;同步时钟;相位延迟;中断窗口;ARM

0 引言

武器系统发射平台多样化是其重要的发展方向[1]。当一个子系统与其它平台大系统进行融合时,大系统常常要求子系统协同工作。这种协同工作可能是异步或同步的[2]。异步工作时,要求某系统按照自身特有的时序独立工作,与其它子系统互不干涉,在任务完成后交换结果;同步工作时,要求按照统一的步调同时工作,在某个子系统/部件完成此刻工作,另外一个子系统/部件开始下一步工作。目前,进行分布式武器系统集成时,主要涉及同步技术,其研究重点集中在外同步、主从同步、保持同步、独立同步、NTP等方面[3-9]。由于某子系统可能有其独立的同步时钟,若要确保武器系统工作正常安全有序、总线数据传输通畅,必须进行时钟信号统一管理,因此,深入研究跨平台下的总线同步时钟发生技术具有重要现实意义和应用价值。

1 总线同步时钟脉冲信号需求分析

某平台下武器系统包括3个层次:大系统、时钟同步系统、子系统。其中大系统产生周期为T的脉冲信号;子系统按照周期为2T的时钟节拍进行工作;时钟同步系统起到两者时钟同步的作用。因此,进行同步时钟设计时,应考虑如下需求:

1)子系统以大系统周期T的上升沿作为自身周期2T的启动信号,即外部触发时钟,每间隔2T与大系统同步1次。

2)子系统对2T时间段进行分时,通常分为20个均匀间隔,在每个时刻某个部件完成相应的任务工作,如图1所示,大系统、部件i、部件j、部件k、部件m、部件p分别在每个周期的ti、tj、tk、tm、tp等时刻占用数据总线,进行数据通信。

3)为提高武器系统运行的安全性,一旦大系统同步时钟脉冲丢失,时钟同步系统能够独立产生周期为2T的同步时钟信号,保证小系统正常工作。

2 总线同步时钟脉冲信号发生方法

1)直接发生法

总线同步时钟发生通常采用直接发生法,其工作原理如图1(a)所示,周期为T的外部时钟上升沿触发计数器0,每触发1次,计数器0累加1;计数器0每奇数个上升沿触发定时器1,定时器1开始延时,对周期为2T的同步时钟的占空比调节以及均间隔分时;1.9T后,定时器1停止定时。同步时钟直接发生法原理简单,但可靠性和容错性都不高。当外部时钟间断触发或丢失时,计数器0不按照正常节拍累加,将导致同步脉冲紊乱;此外,外部时钟信号丢失时,同步信号不能继续产生周期为2T的同步信号。如图1(a)所示,当第5个外部脉冲丢失,第6个、第7个脉冲按时来时,同步时钟的周期将是3T,从而出现错误。

2)定时发生法

为提高直接发生法的可靠性和容错性,提出一种同步时钟定时判断发生法。定时发生法的工作原理如图1(b)所示。打开计数器0中断使能,周期为T的外部时钟上升沿触发计数器0和定时器1。计数器0置中断标志;定时器1开始定时,一方面用于同步时钟占空比调节,另一方面用于均间隔分时。当定时器1定时为T/2,清计数器0中断标志。当定时器1定时到1.8T时,判断计数器0标志是否为0,若为0,说明第偶数个外部脉冲丢失,此时,定时器1抢过定时控制权,继续发生周期为2T的同步脉冲;若为1,清计数器0中断标志,定时器1继续定时,并在[2T-tp/2,2T+tp/2]区间查询计数器0中断标志,判断第奇数个外部脉冲是否到来,若查到,则定时器1从零开始定时,新的一周同步脉冲开始,并使计数器0中断标志为0;若查不到,定时器1抢过定时控制权,继续发生周期为2T的同步脉冲。其中tp由系统所能承受的外部时钟周期的最大误差所确定。

显然,定时发生法具有很高的容错性。由于外部同步脉冲精度一般是微秒级的,同步脉冲定时发生法采用在[2T-tp/2,2T+tp/2]判断的策略,判断语句将引起误差。不同时间尺度的判断语句引起的误差也不同,时间尺度越小,判断语句占用的时间就越小。如图1(b)所示,时间尺度ts1比ts2造成的误差小。

3)相位延迟发生法

为进一步提高定时发生法的同步准确性,在其基础上,提出一种相位延迟法。相位延迟法的工作原理如图1(c)所示。

打开定时器0中断使能,周期为T的外部时钟上升沿触发定时器0,定时器0触发定时器1。定时器1开始定时,并关定时器0中断使能。当定时器1定时到T-tp时,打开定时器0中断使能。定时器1定时到T时,触发定时器2,定时器1清0,定时器2开始定时,用于同步时钟占空比调节和均间隔分时。并且,当定时器2定时到tp,关定时器0中断使能。当定时器2定时到0.9T时,判断定时器0中断标志是否为1,若为1,继续定时,否则说明第偶数个脉冲异常,此时,定时器2抢过定时控制权,继续发生周期为2T的同步脉冲。定时器2定时到T-tw时,定时器0打开中断使能;定时器2定时到T+tp时,定时器0关中断使能,若在[T-tp,T+tp]区间,有外部脉冲触发。定时器1自动定时。当定时器2定时到1.9T时,判计数器0标志是否为1,若为1,定时器2定时清0;若为0,说明第奇数个外部脉冲丢失,定时器2抢过定时控制权,继续发生周期为2T的同步脉冲。当定时器1定时到T时刻,触发定时器2进行新一轮周期定时。

相位延迟法的工作原理体现两个特点:

①外部时钟是否丢失判断时刻选在第0.9T、1.9T,判断语句不导致同步时钟产生误差,从而提高同步时钟的准确性;

②增加[T-tp,T+tp]区间的中断窗口,可对外部脉冲周期进行选择。

3 同步时钟误差分析

若外部触发时钟为T-ΔTt,其中ΔTt为偏离误差,根据总线同步时钟触发原理,则合成后的理论同步时钟应为2(T-ΔTt)。在实际工作中,由于芯片延迟、软件调度、晶振漂移等原因产生的误差ΔTs,实际合成的时钟应为2(Tt-ΔT)+ΔTs。进行外部触发时钟和合成时钟进行比较,则同步时钟误差为ΔTs。ΔTs是考核时钟同步特性的重要指标,为便于分析,同步时钟误差通常采用百分比的形式表示,即:

(1)

4 案例研究

4.1 系统要求

某子系统与大系统进行系统集成时,大系统采用周期为10 ms的总线同步时钟,子系统采用周期20 ms的同步时钟。若保证大系统通畅工作,必须对跨平台的总线同步信号进行协同控制。并要求1路输入,多路输出,每20 ms校准1次;当外部同步时钟10 ms丢失时,继续产生20 ms时钟信号,以保证武器系统的安全性。

4.2 硬件设计

为实现上述要求,搭建一种基于ARM7 LPC2478的时钟同步系统。为保持与大平台的AM26LS31信号兼容,同步时钟系统采用AM26LS32进行差分信号接收,然后合成单端信号通过磁隔离芯片ADUM1200[10],进入LPC2478中产生全局中断。主控芯片按照相位延迟法发生原理,产生多路周期20 ms的同步信号,通过磁隔离芯片ADUM1200进入差分芯片MAX488中。差分芯片MAX488与子系统的子部件连接,协调与各子部件按节拍工作。

4.3 软件设计

系统软件主要包括10 ms外部触发信号粗校验子程序、10 ms外部触发信号测量子程序、20 ms同步时钟发生子程序。10 ms外部触发信号粗校验子程序主要用于查看10 ms信号是否到来,粗检验原理如下:系统定时1 s,程序查看这一时间区间的10 ms触发系统中断的个数;严格意义上讲,若外部10 ms没有误差,10 ms中断个数应为100个,但10 ms信号有可能出现误差,则中断个数有偏差;一般认为中断个数落在95~105区间,则认为外部10 ms信号正常到来。10 ms外部触发信号测量子程序主要用于获取外部10 ms信号的真实值。方法如下:打开系统计数器,分别测量100个外部10 ms的信号,然后把100个测量值进行均化处理,从而获得比较精确的10 ms真实值。当外部10 ms触发信号丢失时,系统自动产生2倍的10 ms真实值,从而减少由于外部时钟晶振和信号转换器时钟晶振差异造成的周期误差漂移。20 ms同步时钟发生子程序包括10 ms正常和丢失两个状态,产生原理采用相位延迟发生法,这里不再赘述。

4.4 试验分析

采用高精度信号发生器产生不同偏差的10 ms外部触发信号;逻辑分析仪分别接在10 ms外部触发信号和20 ms同步时钟端,用于获取两者真实值。试验分为两个模式:10 ms正常状态以及10 ms丢失状态。

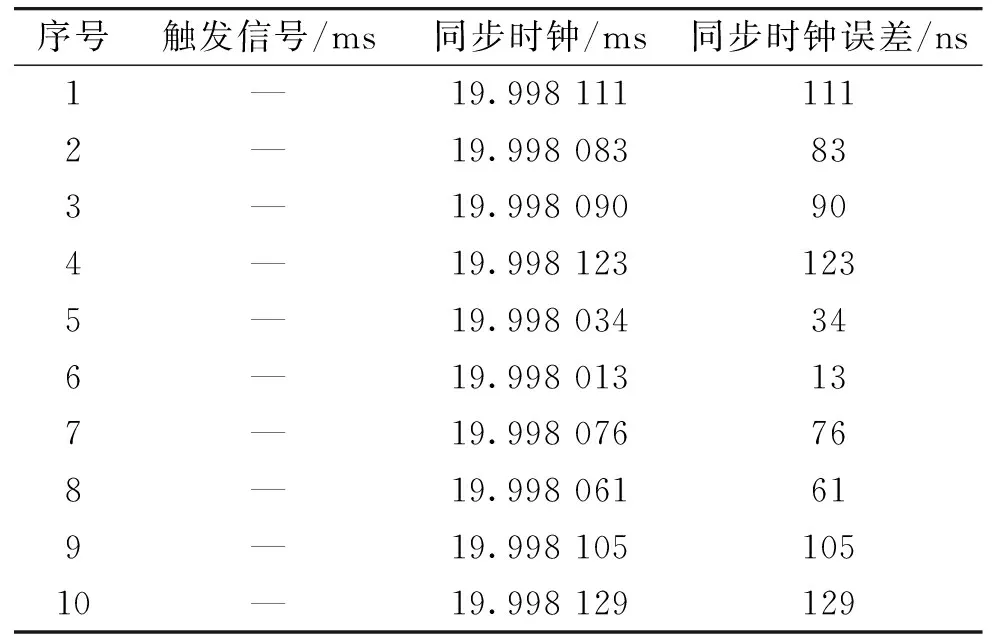

0 ms正常状态下,试验时,其触发信号、同步时钟及其误差如表1所示,其均化误差为:

10 ms丢失状态下试验步骤如下:提供外部触发时钟为9.999 ms;时钟同步系统正常工作10 s后,物理断掉外部触发信号,连续获取10个周期的同步时钟如表2所示。

表1 同步时钟误差试验分析表

因此,10 ms丢失状态下的均化误差约为:

上述试验表明该系统具有很高的时钟同步精度且有很好的容错性,从而证明了同步时钟相位延迟发生法的可行性和准确性。值得说明的是:10 ms丢失状态下的均化同步误差小于正常状态下的均化同步误差,原因在于10 ms丢失状态下,同步时钟由系统自动产生,减少了外部触发软件调度环节。

表2 10 ms丢失状态下试验

5 结论

提出一种新颖的跨平台武器系统同步信号发生技术,通过理论分析和试验研究,可得出如下结论:提出的同步信号相位延迟发生技术,大大降低了传统直接触发法的同步误差,提高了时钟同步精度以及系统的可靠性和容错性;同步信号相位延迟发生技术原理简单,在ARM、DSP、单片机、FPGA等平台易于实现。

[1] 中国科学技术协会. 2008—2009兵器科学技术学科发展报告 [M]. 北京: 中国科学技术出版社, 2009: 2-3.

[2] 魏建峰, 王涛, 张莹, 等. 基于CPLD的火控系统CAN总线同步信号发生器的设计 [J]. 弹箭与制导学报, 2008, 28(6): 247-249.

[3] 裴福俊. 基于捷联基准及变形测量的分布式姿态基准系统研究 [D]. 南京: 东南大学, 2005.

[4] 王刚, 乔纯捷, 王跃科. 基于时钟同步的分布式实时系统监控 [J]. 电子测量与仪器学报, 2010, 24(3): 274-278.

[5] 赵建强. 分布式系统高精度时间同步技术研究 [D]. 成都: 四川大学, 2005.

[6] LAMPORT L. Time, clocks, and the ordering of events in a distributed system [J]. Communication of the ACM, 1978, 21(7): 558-565.

[7] SRIKANTH T K, TOUEG Sam. Optimal clock synchronization [J]. Journal of the Association for Computing Machinery, 1987, 34(3): 626-645.

[8] 潘玉林, 姚新宇, 陈勇, 等. 并行分布实时仿真的高精度时间管理 [J]. 系统仿真学报, 2009, 21(增刊2): 154-156.

[9] 刘晚春, 李峭, 何锋, 等. 时间触发以太网同步及调度机制的研究 [J]. 航空计算技术, 2011, 41(4): 122-127.

[10] 田野, 桂欣, 李一兵. 基于ADuM540x隔离通信电路的设计与实现 [J]. 哈尔滨商业大学学报(自然科学版), 2009, 25(5): 574-577.

InvestigationonBusSynchronousClockGeneratingTechnologyofCrossPlatformWeaponSystem

ZHOU Yuqing, XUE Xiaole, LI Yugang, LUO Sheng

(No.203 Research Institute of China Ordnance Industries, Xi’an 710065, China)

A novel bus synchronous clock generating technology of cross platform weapon system was proposed, which adopted phase delay, interrupt window methods to reduce the error caused by the traditional direct triggering technology and enhance the fault tolerance of bus synchronous clock producer and the safety of arm system. Furthermore, the technique was applied to the clock synchronization system of a weapon system, and the feasibility and effectiveness of the method was verified.

communication bus; synchronous clock; phase delay; interrupt window; ARM

TP274

A

2016-09-18

周玉清(1978-),男,安徽临泉人,高级工程师,博士,研究方向:武器系统综合测试技术。