应用于谐振式光学陀螺的数字低通滤波器设计*

谌浩然, 薛晨阳, 张成飞, 王 颖, 陶 煜, 郑永秋

(中北大学 仪器科学与动态测试教育部重点实验室, 山西 太原 030051)

谐振式光学陀螺是基于Sagnac效应的新一代高精度角速度传感器, 其微弱的频差信号要求高信噪比的信号检测系统[1]. 锁相放大器[2]作为微弱信号检测技术领域中的一个重要部分, 具有检测能力强、 通用性强、 可靠性高等优点, 取得了广泛应用[3-5]. 随着谐振式光学陀螺信号检测系统向数字化检测的方向发展, 数字锁相放大器成为了对陀螺信号进行解调输出的主要组成模块[6]. 数字低通滤波器是数字锁相放大器的主要构成部分之一, 其作用是滤除锁相放大器解调输出信号的带外噪声, 在窄带宽范围内得到微弱频差信号, 提高数字锁相放大器的信噪比, 该滤波器的带外抑制能力决定了整个解调输出系统的抗干扰能力[7]. 在谐振式光学陀螺数字信号检测系统中, 要求数字低通滤波器具有较低的截止频率且调节方便、 较高的采样率、 较低的FPGA资源占用率[7]. 相对于谐振式光学陀螺数字信号处理系统40 MHz的工作频率来说, 实验室现有的普通一阶无限脉冲响应(Infinite Impulse Response, IIR)滤波器所需带宽仅几十赫兹, 其系数选择困难, 截止频率调节过程繁琐, FPGA资源占用率高, 功耗大[7]. 因此该滤波器并不适用于谐振式光学陀螺数字信号检测系统. 本文针对谐振式光学陀螺数字信号检测系统提出的要求, 设计了一阶惯性数字低通滤波器, 具有截止频率低且带宽调节方便, 采样率高, FPGA资源占用率低, 阶数可调节等优点.

1 系统原理

1.1 谐振式光学陀螺基本原理

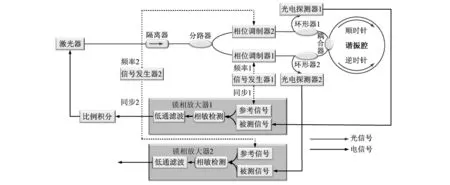

谐振式光学陀螺数字信号检测原理如图 1 所示, 激光器发出的光经隔离器后由分路器分成两束相同的光, 再经过相位调制器后由环形器进入耦合器耦合进谐振腔形成顺时针和逆时针两个方向上的激光, 谐振腔输出的光信号经光电探测器转换为电信号后进入数字锁相放大器进行解调, 其中顺时针路经过比例积分环节对激光器的输出频率进行锁定, 使激光器输出与顺时针路的谐振频率相同的激光, 逆时针路经数字锁相放大器解调后即为陀螺输出信号.

图 1 谐振式光学陀螺基本原理Fig.1 Basic principle of Resonant optical gyro

数字锁相放大器作为谐振式光学陀螺微弱频差信号检测的核心器件, 可实现对光电探测器输出信号的同步解调, 得到激光器中心频率与谐振频率之间的频差信号, 其带宽决定锁频环路和陀螺输出带宽, 其性能直接决定了陀螺输出信号的质量.

1.2 锁相放大器基本原理

锁相放大器是微弱信号检测领域中一种基于相关检测理论的对交变信号进行相敏检测的放大器, 能对被测信号和参考信号进行相关运算, 有效地抑制噪声, 实现对信号的鉴频和跟踪[1,8]. 基本原理如图 2 所示, 主要由被测信号模块, 参考信号模块, 相敏检测模块和低通滤波模块等几部分组成[1].

设被测信号为S(t), 参考信号为R(t),ω0为被测信号和参考信号的频率,φ为两者相位差, 对被测信号进行相敏检测

P(t)=S(t)R(t)=Vscos(ω0t+φ)Vrcos(ω0t)=

0.5VrVscosφ+0.5VrVscos(2ω0t+φ),

(1)

图 2 锁相放大器原理图Fig.2 Schematic of lock-in amplifier

式中: 最后一个等号后第一项为直流分量, 第二项为二倍频分量, 频率为ω0的频谱被相敏检测器搬移到了频率为ω=0和ω=2ω0处, 其幅值取决于Vr和Vs, 相敏检测信号输出后经过低通滤波器, 滤除二倍频分量后得到直流分量:P0(t)=0.5VrVscosφ, 当φ=0时,P0(t)输出幅值最大, 从而通过鉴幅实现对信号的检测, 同时可滤除系统内其他带外噪声, 提高信号的信噪比[9].

在谐振式光学陀螺数字信号检测系统中, 数字锁相放大器的理论输出信号为直流信号, 要求系统的信噪比高, 数字锁相放大器中数字低通滤波器的截止频率低. 为了满足系统检测精度并匹配40 MHz的FPGA工作时钟, 要求信号处理频率为40 MHz; 由于不同参数的光学谐振腔需要不同的调制参数和环路带宽, 需要不同的截止频率, 其截止频率的调节要求方便快捷[7]; 对于实验室现有的IIR滤波器而言, 需要根据MTALAB仿真得到收敛的量化系数来调整程序和寄存器的位数, 调节过程繁琐[6]. 同时, 截止频率越低需要的滤波器阶数越高, 导致PFGA资源占用过多, 增加了系统功耗和调节的复杂程度. 因此, 为了充分利用FPGA内部资源, 需要设计一种在保证40 MHz采样率的同时, 截止频率低且调节方便, 资源占用率低, 阶数可调节的数字低通滤波器.

2 惯性数字滤波器设计、 仿真与测试

2.1 惯性低通数字滤波器设计、 仿真

针对谐振式光学陀螺数字信号检测系统对数字锁相放大器中低通滤波器提出的40 MHz采样率、 低截止频率及其调节的便捷性和阶数可调节的要求, 设计了惯性低通滤波器[10], 其函数模型为

Y(n)=αX(n)+(1-α)Y(n-1),

(2)

式中:α为滤波器系数,X(n)为本次采样值,Y(n-1)为上一时刻滤波输出值,Y(n)为本次滤波输出值. 将本次采样值与上一时刻滤波输出值进行加权处理得到有效输出值, 实现输出信号对输入信号的反馈, 达到滤波目的.

图 3 数字惯性滤波器的数学模型Fig.3 Mathematical model of digital inertial filter

在程序实现过程中, 滤波器的输入信号与负反馈信号相加之前, 对输入信号由32 b扩展到59 b防止累加造成数据溢出, 同时做数据正负号区分处理, 以便后续内部程序进行有符号运算, 然后进行累加运算, 经过2N增益后输出, 则该数字滤波环路的传递函数为

(3)

式(3)即为一阶低通滤波器的传递函数, 截止频率

(4)

式中:N为数字低通滤波器中截止频率的调节信号, 即设计的数字低通滤波器只需调节整个算法程序中的N值即可实现不同截止频率的数字低通滤波器,N每增加1, 截止频率降低为原来的1/2, 反之,N每减小1, 截止频率增加至原来的2倍.

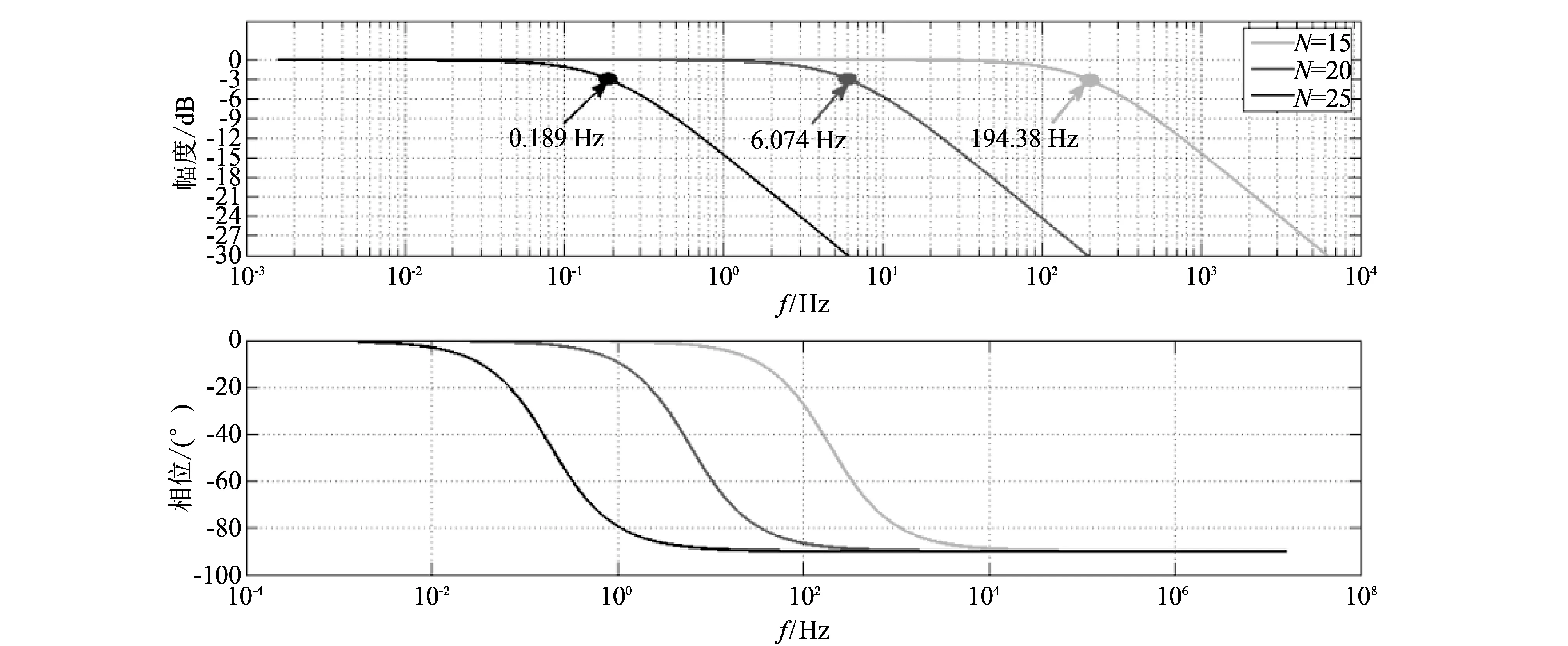

为了验证算法的正确性, 采用Matlab对以上模型进行仿真, 结果如图 4 所示, 当N=15, 20, 25时, 理论上3 dB截止频率分别为194.38 Hz, 6.074 Hz, 0.189 Hz.

图 4 不同N值下波特图Fig.4 The Bode plot with different N values

针对以上模型进行低通数字滤波器VHDL模块设计, 如图 5 所示, 图中模块(1), (2), (3)为3个惯性滤波单元, 通过级联后即可形成一个三阶数字低通滤波器, clkin为40 MHz时钟控制信号, datain为32 b输入信号, ink为滤波器截止频率调节端口, 可通过上位机直接调节, 模块(4)为D/A输出模块, 完成数模转换后输出滤波信号.

图 5 数字低通滤波器程序模块组成Fig.5 Program module of digital low-pass filter

2.2 惯性低通数字滤波器的测试

目前实验室所采用的IIR滤波器与所设计的惯性数字低通滤波器FPGA资源消耗对比如表 1 所示.

表 1 滤波器FPGA资源消耗对比

图 6 滤波器测试系统图Fig.6 The test system of the filter

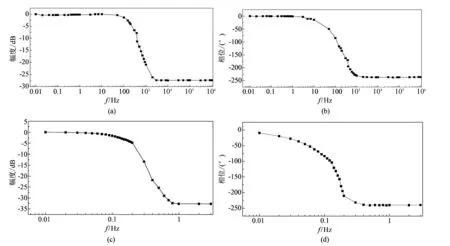

所设计的惯性数字低通滤波器消耗DSP48s单元仅为0.09%, 查找表和逻辑片仅占用0.06%, 大大降低了FPGA的资源占有率, 降低了功耗. 实验对理论截止频率分别为194.38 Hz(N=15), 0.189 Hz(N=25)的惯性数字低通滤波器的幅频特性和相频特性进行了测试, 测试系统如图 6 所示, 信号发生器产生不同频率的正弦波经低通滤波器滤波后与原始正弦信号在示波器上进行对比, 并对示波器显示的数据进行采集和处理, 为降低测量误差, 试验中对每个正弦信号进行3次滤波测试, 取滤波后信号频率和幅值的均值.

测试结果如图 7 所示, 得到截止频率分别为162 Hz, 0.14 Hz, 与理论值基本相符, 且该滤波器在截止频率处信号幅值衰减斜率较大, 截止特性良好, 相频特性优良.

图 7 幅频特性和相频特性测试结果Fig.7 The test results amplitude/phase frequency characteristics

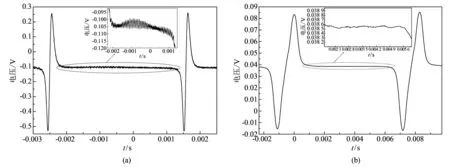

图 8 锁相放大器输出对比Fig.8 The comparison of the lock-in amplifier output

根据图 1 所示谐振式光学陀螺系统原理图, 将所设计的惯性数字低通滤波器和传统的IIR低通滤波器分别应用到数字锁相放大器中, 对其输出的解调输出信号进行了对比. 由于IIR低通滤波器在40 MHz的信号处理频率下, 截止频率很难做到kHz以下, 考虑到FPGA内部有限的运算资源, 截止频率只能设计到10 kHz, 如图8(a)所示, 解调曲线中仍残存有较高频的带外噪声. 而采用设计的数字惯性滤波器滤波时, 由于占有FPGA内部运算资源极少, 截止频率可以调节到更低, 且滤波器的阶数可通过滤波单元的串联实现阶数扩展, 因而具有良好的滤波效果, 如图 8(b) 所示, 截止频率为194 Hz时, 解调曲线中不再存在高频噪声.

3 结束语

本文通过对谐振式光学陀螺信号检测系统中锁相放大器内低通数字滤波器应用条件的分析和介绍, 设计了滤波算法简单, 采样率高, 截止频率低且调节方便, FPGA资源占有率低的惯性数字低通滤波器, 其阶数可通过级联的方式进行调节, 拥有优良的幅频特性和相频特性; 针对不同情况下陀螺输出信号对带宽的要求以及检测灵敏度和动态范围的选择, 设计了滤波器的带宽和增益控制机制; 对谐振式光学陀螺锁相放大器输出信号进行了测试, 解调曲线高频波动基本消失. 此外, 该滤波器在满足不同条件下陀螺输出信号检测要求的同时, 对于提高其他微弱信号检测系统的信噪比也具有一定的参考价值.

参考文献:

[1]鲍慧强. 谐振式光学陀螺频率锁定技术与FPGA实现[D]. 杭州: 浙江大学, 2010.

[2]高晋占. 微弱信号检测[M]. 北京: 清华大学出版社, 2004.

[3]Paulkd, Leiw. Broad band digital lock-in amplifier techniques[J]. Review of Scientific Instruments, 1989, 60(10): 3329-3336.

[4]Gaspar J, Chen S F, Gordillo A, et al. Digital lock in amplifier: study, design and development with a digital signal processor[J]. Microprocessors & Microsystems, 2004, 28(4): 157-162.

[5]杨桂东, 马慧莲, 张旭琳, 等. 一种应用于谐振式微型光学陀螺的高频锁相放大器的设计[J]. 传感技术学报, 2005, 18(4): 863-866.

Yang Guidong, Ma Huilian, Zhang Xulin, et al. Design of high frequency lock-in amplifier applied in R-MOG[J]. Chinese Journal of Sensors and Actuators, 2005, 18(4): 863-866. (in Chinese)

[6]彭博. 基于FPGA的谐振式光纤陀螺数字系统设计和实现[D]. 杭州: 浙江大学, 2010.

[7]杨俊义. 基于FPGA的数字锁相放大器研究[D]. 杭州: 浙江大学, 2012.

[8]蔡满军, 于彬, 赵晓东. 基于正交锁相放大器的微弱应变信号检测系统[J]. 仪表技术与传感器, 2017(4): 67-72.

Cai Manjun, Yu Bin, Zhao Xiaodong. Weak strain signal detection system based on quadrature lock-in amplifier[J]. Instrument Technique and Sensor, 2017(4): 67-72. (in Chinese)

[9]王文怡. 双路闭环谐振式微光学陀螺数字信号检测系统的设计与实现[D]. 杭州: 浙江大学, 2013.

[10]邵强, 艾莹. 有源滤波与惯性滤波方法的综合应用[J]. 大连民族大学学报, 2007, 9(3): 45-47.

Shao Qiang Ai Ying. Application of active filter and digital filter methods[J]. Journal of Dalian Nationalities University 2007, 9(3): 45-47. (in Chinese)