SV DPI技术在FPGA仿真验证的应用探讨

,,, ,

(上海航天电子技术研究所,上海 201109)

0 引言

目前数字系统设计中应用最为广泛且最为有效的验证方法就是仿真。除了验证单个模块功能的正确性、接口交互以及整个系统功能的正确性,还可以模拟边界测试、故障测试等,而硬件测试上往往是不能进行的。但是随着FPGA功能趋于复杂以及实现算法复杂度提高,其输入信号可能是通过复杂模型产生的,比如信号的调制,傅里叶变换等。验证人员受专业限制,无法理解和模拟该类输入信号,只能向设计师要数据源。那么谁来保证数据源的正确性?如果使用该数据源出错,那么问题是出在数据源,还是FPGA设计呢?很显然,这样无法保证验证工作的独立性。即使是明白专业的验证人员通过Verilog或VHDL来实现复杂的输入模型,同样存在致命的缺点。比如调用Verilog和VHDL的IP来实现正弦函数,由于HDL并行化的特点,在仿真中将占用大量的内存,极大的影响仿真的速度。此外,如何在一个独立的验证平台中验证FPGA算法功能是否正确。比如计算一幅图像的方差,通常方法是额外编写一个C程序,然后人工的比对双方的结果,以验证该算法是否正确,没有进行实时比对,仍然存在测试有效性的问题。

本文提出了一种新的验证解决方案,利用仿真工具中的SV DPI技术,实现了在SV仿真验证平台中调用C或C++编程语言[1],利用高级语言可以更加方便的实现激励读取、参考模型构建等功能。本文就该类解决方法进行相关的阐述和讨论,这对于提高FPGA验证充分性和验证的独立性,以及验证的灵活性都有着重要意义。

1 SV DPI仿真验证方法

1.1 PLI和SV DPI

Verilog是现有航天FPGA验证中最常用的语言。Verilog使用编程语言接口PLI(Programming Language Interface)来跟C语言程序交互。使用PLI可以生成延迟计算器,以连接和同步多个仿真器,并增加诸如波形显示等调试工具。但是PLI非常繁琐,即使通过PLI连接一个简单的C程序,都需要编写大量的代码,并需理解很多概念,这些概念包括多个仿真阶段的同步、调用段、实例指针等等。此外,PLI给仿真带来了额外的负担,因为为了保护Verilog数据结构,仿真器必须不断地在Verilog和C语言域之间复制数据。所以现有的FPGA验证过程中,FPGA验证人员基本不会去使用PLI。

而新一代的验证语言SystemVerilog引入了直接编程接口DPI[2-3],它能更加简单地连接C、C++编程语言。一旦你声明或者使用import语言“导入”了一个C子程序,你就可以像调用SystemVerilog中的子程序一样来调用它,使用起来非常方便。首先,通过高级语言实现复杂模型比使用hdl语言要轻松很多,且仿真速度快。比如C语言已经提供了很多库函数,直接调用即可,无须重新编写。这样既保证了激励编写的正确性,又提高了可重用性。同时C语言目标代码的执行速度比hdl仿真速度要至少提高一个数量级。其次,FPGA中实现的算法都有可靠的高级语言模型,基于DPI技术的FPGA仿真验证平台可以直接调用该模型,实现同一份激励输入到FPGA设计和高级语言模型,然后比对两个结果,以判断FPGA设计实现正确性。通过该方法,验证人员可以不受专业限制,将FPGA设计完全看做是一个黑盒,保证验证方的独立性。再次将C函数连入验证平台,容易实现验证平台的完整性,为自动测试创造了条件。最后,利用SystemVerilog的受限制随机激励生成功能、断言和功能覆盖率功能可以大大提高测试的效率和质量。

1.2 SV DPI验证技术使用步骤

要使用SV DPI验证技术顺利将SystemVerilog和C联合起来仿真,应按照下面4个步骤进行。

1)编写C代码实现算法。DPI包括两个完全独立的层次,分别是SystemVerilog和C,在C代码中需要声明包含头文件svdpi.h,因为在svdpi.h中包含了SystemVerilog DPI结构和方法的定义[4]。

2)实现C与SystemVerilog通信。SystemVerilog平台中通过导入函数和任务来调用C代码,DPI也允许在C代码中通过导出函数和任务来调用SystemVerilog中的方法[5]。被调用的SystemVerilog方法可以是一个保存C函数操作结果的简单任务,或者是一个实现部分硬件模型的耗时任务[6]。

SystemVerilog平台中导入函数和任务的定义如下:

import “DPI” [c_identifier =][pure][context]function type name(args);

import “DPI” [c_identifier =] [context]task type name(args);

SystemVerilog平台中导出函数和任务的定义如下:

export “DPI” [C_identifier =]function type name;

export “DPI” [C_identifier =]task type name;

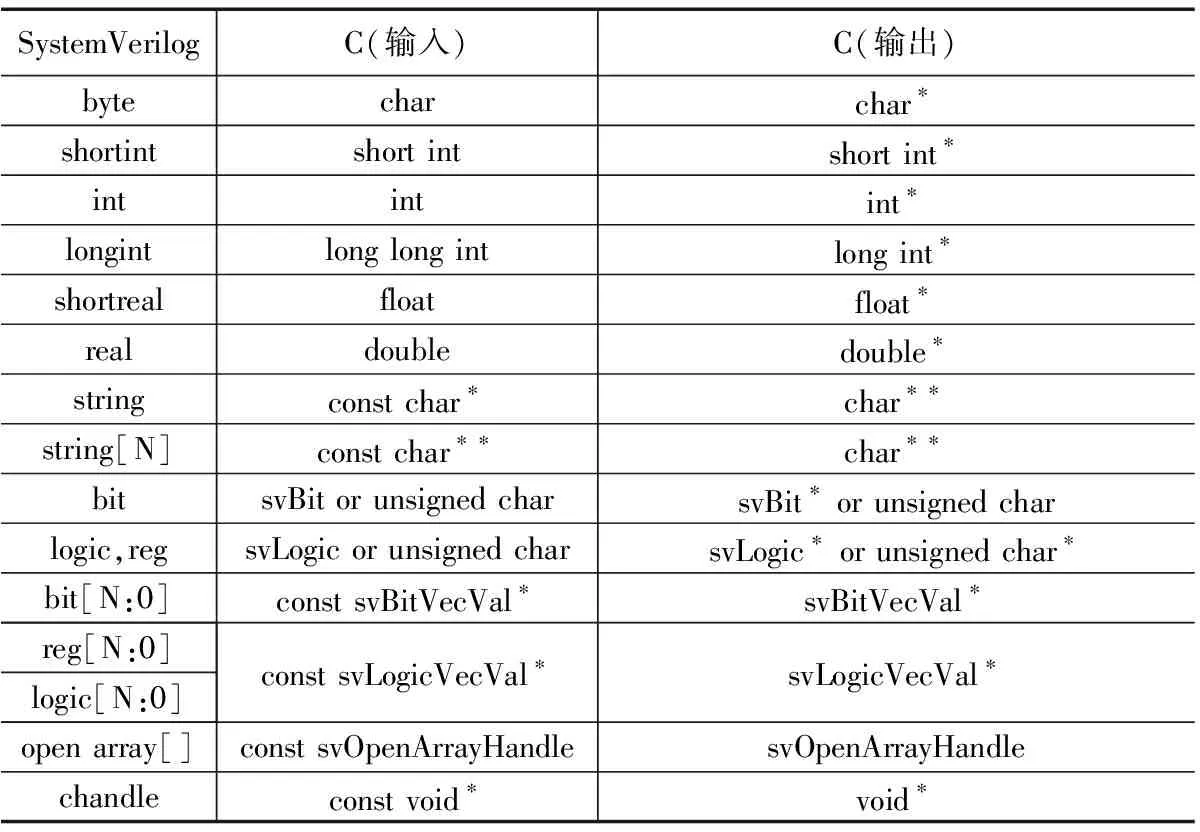

3)匹配数据类型映射。由于SystemVerilog数据类型和C语言数据类型差异比较大,SystemVerilog3.1语言手册定义了通过DPI传递的每个数据类型的匹配模式。具体见表1[4]。

表1 SystemVerilog和C语言之间的数据类型映射

其中对于bit和logic类型匹配在svdpi.h文件中有专门的指定。使用者需根据svdpi.h文件中的定义来选择匹配的数据类型。另外需要注意的是:DPI不会检查数据类型的兼容性,需要使用者自己保证数据匹配的正确性。

4)利用仿真工具编译C程序的方法,生成最终的目标码,并和SystemVerilog混合运行。

2 工程实例

2.1 仿真模型构建

某FPGA产品根据采集到的多音组合调频信号,依据一定的解调算法实现最终的解码[9]。验证人员在VCS环境搭建基于DPI技术的FPGA仿真验证平台如图1所示。解出的密码包括m个码元,每个码元为n位。每个码元都是由n个单音(正弦波)中的4个叠加而成,而每个单音的频率是不一样的,若m个码元解密出的数据与存储密码一致,则解密成功。每个多音组合调频信号指令格式如图2所示。

图1 某FPGA产品验证架构

图2 多音组合调频信号指令格式

该FPGA产生AD芯片的采样的时钟和读控制信号,AD芯片根据相应的时序采集外围的模拟信号,AD芯片将其转换为数字信号输出给FPGA设计。基于图1的验证架构,验证人员根据DPI验证流程按照以下步骤,实现整个FPGA验证架构。

1)编写C程序模拟完成多个单音数据(正弦波)叠加后的数字化采样。在SystemVerilog验证架构中随机挑选4个单音进行叠加,生成多种单音组合序列,SystemVerilog将这些序列指令码元的组合情况通知C程序,C程序根据输入的参数实现AD采样数据的模拟。C程序先根据参数频率计算15组码元数据的角速度值和导频音角速度值,利用角速度值和幅值参数生成16组标准的2048个点精度的二进制偏移正弦波,然后根据输入的单音组合序列,当有组合序列对应位置为1时,将对应的正弦波叠加,再根据组合情况,按照时间顺序,前10 ms输出导频音正弦波,5 ms输出第一组叠加的多音组合,下个5 ms输出第二组多音组合,依次输出7个。

图3 C程序模拟AD输入数据生成代码

2)在SystemVerilog中调用C程序,实现数据的相互通信。在SystemVerilog中,通过import “DPI-C”声明定义C函数的原型[7],接着在SystemVerilog的任务或者进程中就可以调用C函数MaYuan。为了提高仿真的效率,应尽量减少SystemVerilog和C函数的通讯,所以在该平台中,将C函数计算出的7个码元对应的数字化采样数据一次性写入到文件中,SystemVerilog平台通过Read_file过程使用读取文件的方式来实现AD数据的注入,而不是通过C函数返回的方式,这样可以适当提高仿真的效率。

图4 在SV中调用C程序

3)注意匹配SystemVerilog的数据类型和C语言的数据类型的兼容性映射。在 该应用实例中SystemVerilog传递给C程序的接口包括指令组合(ZhiLing[0:6])、幅值(DaoPin_FUZHI)、频率(PinLv)。SystemVerilog的数据类型和C语言的数据类型的兼容性如表2所示。

表2 SystemVerilog的数据类型和C语言的数据类型映射

4)完成解调出的密码与输入的指令码元自动比对功能。图1的解调模块将根据时钟收集解调出的码元,同时将其按照特定的格式转换为指令,与传递给C程序的指令组合(ZhiLing[0:6])进行比较,完成自动比对功能,以确认FPGA设计的解调功能是否正确。

5)利用仿真工具VCS编译[8]C程序的方法,从而生成最终的目标码。该FPGA仿真工具采用了linux环境下的VCS仿真工具,VCS调用linux下的gcc编译器,可以实现在对FPGA代码编译的同时,也完成对C程序的编译以及目标码的生成,如图5所示。

图5 仿真工具VCS编译C程序

2.2 仿真结果与分析

对于复杂算法类 FPGA设计,怎样自动生成测试用例数据、怎样进行测试用例数据注入和进行结果分析是测试验证工程师面临的一大难题。传统的仿真验证方法只能通过matlab生成数据源,利用时钟导入的方式进行仿真验证,只能进行正常的功能测试,更无法进行结果比对。利用3.1节描述的仿真模型,验证人员通过ZhiLing、DaoPin_FUZHI和PinLv参数的配置以及MaYuan函数的灵活调用,实现了表3中的11个测试用例,并发现当预令码元不是由四个单音组成时,解码结果不正常的问题。而使用传统的仿真验证或者硬件测试方法要实现表3中的所有测试用例非常麻烦,耗时巨大,因此之前一直没有发现问题。

由此可知,通过上述方法搭建的基于DPI技术的FPGA仿真验证平台,具备如下几个优点:

1)由高级语言C编写的激励输入,相比Verilog中的IP调用[10],无疑极大的提高了仿真效率。

2)验证人员通过C代码编写的激励向量,无须向设计师索取激励输入数据,保证了验证工作的独立性。

3)依据随机产生的指令组合,然后根据C代码产生的AD数据作为FPGA输入,再对FPGA解码出的指令组合与随机产生的指令组合进行自动比对,提高了测试的自动化和测试的完备性。

3 结语

复杂算法FPGA仿真验证的有效性一直是FPGA验证的热点问题,本文提出的利用SV DPI仿真技术实现在SV仿真验证平台中调用C或C++的验证方案。经工程应用论证,利用SV DPI技术在SV仿真验证平台中调用C或C++编程语言,可以更加方便的实现激励读取、参考模型构建、测试结果自动比对等功能。基于SystemVerilog的FPGA验证平台,可以通过DPI实现SystemVerilog平台与高级语言(C、C++等)的通信,让Systemverilog的强大验证能力能够在事物处理级模型的验证工作中充分发挥[11],相对于传统的纯verilog验证平台,大大提高了仿真效率和验证的灵活性,同时也为算法级FPGA设计的确认测试提供了新的验证思路。

表3 调频和多音组合解调功能测试表

参考文献:

[1] 虞致国,魏敬和. 基于SystemVerilog DPI的ARM SoC虚拟调试验证平台的设计[J].微电子学与计算机,2009(11): 117-119.

[2] 闫 沫,张 媛. 基于SystemVerilog语言的设计验证技术[J].现代电子技术,200806:8-11.

[3] 耿 介,于治楼,毕研山.一种UVM验证环境中复用C程序测试向量的方法: CN104899138A[P]. 2015-09-09.

[4] Synopsys VCS MX/VCS MXi User Guide [S] .Version E-2011.03-SP1 August 2011.

[5] 李 璐,周春良,冯 曦,等.基于 DPI-C 接口的可扩展 SOC 验证平台[J].电子设计工程,2018,26(4):136-140.

[6] 王 纪,冯志华.SOC多语言协同验证平台技术研究[J].电子设计工程,2015,23(20):130-133.

[7] Synopsys.Reference Verification Methodology User Guide[S].September, 2004.

[8] Synopsys.Design Ware AHB Verification IP Databook[S].March 24,2003.

[9] 王俊蕊,李艳斌.短波多音并行信号全数字解调算法设计[J].无线电工程, 2016 (1):76-79.

[10] 鲍晓利, 冯永新. 宽带扫频式干扰的仿真与FPGA实现[J].沈阳理工大学学报,2008, 27(3):61-64.

[11] Schutten R.基于ESL并采用SystemC和SystemVerilog的设计流程[J].电子设计技术,2006 ,13(4) :142-142.