钛酸铋/铁酸钴层状复合材料的制备及其性能研究**

田佳豪 林 营 邱 云

(陕西科技大学材料科学与工程学院 西安 710021)

前言

随着社会不断进步和科学技术高速发展以及对器件微型化的不断需求,具有单一性能的材料已经很难满足新型器件对材料的要求。多铁性材料在集成电路、通讯技术、测绘技术、自动控制等高科技领域具有重要而广泛的应用,在国民经济和国防建设中占有重要的地位[1~2]。所以目前迫切需要开发出具有多种功能的先进材料,而铁电性和铁磁性共存的多铁性材料就是其中重要的一类[3~4]。

作为铋层状化合物铁电体重点带型代表——钛酸铋(Bi4Ti3O12),越来越引起人们的关注[5]。这是由于铋层状类钙钛矿结构的钛酸铋拥有着非常优异的极化翻转的抗疲劳特性、性能各向异性的自发极化强度,远高于室温的居里温度等优良的铁电性能使得钛酸铋高温铁电材料在小型化、集成化铁电技术具有越来越重要的意义[6]。许多科学工作者研究发现,将钙钛矿结构的ABO3型铁电体引入磁性离子或者与铁磁相复合,能够使材料在室温下获得一定的铁磁性能[7],对于铋系层状类钙钛矿结构的铁电体来说,其具有优良的铁电性能,不含Pb的环境友好特性,较低的烧结温度,较高的居里温度和杰出的抗疲劳性能,获得了越来越多研究学者的研究与关注[8~10],其中尤其以具有三层钙钛矿结构的Bi4Ti3O12为典型。

钛酸铋的铁电极化在不同方向上表现各异。在a-c平面内,其自发极化矢量沿a轴和c轴相差较大,分别为50 μC/cm2和4 μC/cm2。钛酸铋的居里温度远高于室温Tc=675 ℃,且具有优良的抗疲劳性能,被认为是绝佳的高温铁电材料[11]。CoFe2O4(CFO)为尖晶石型结构,其烧结温度在1 000~1 050 ℃之间,CFO制备较为容易。其居里温度很高,拥有很高的温室自旋极化率大、饱和磁化强度,磁晶各向异性,高矫顽力和温和的磁化性能。在目前的铁磁材料中CoFe2O4拥有最高的磁致伸缩性能[12]。

磁电复合陶瓷材料根据其连通方式不同可以分为0-3型颗粒磁电复合材料和2-2型层状磁电复合材料。2-2型层状磁电复合陶瓷材料在铁电性、铁磁性可以很好地保持各自的独立性,减少界面的化学反应,两相之间界面面积小,材料内部的缺陷较少,可以有效降低材料的介电损耗和漏导电流[13]。因此,相比于0-3型复合材料,2-2型具有更好的磁电耦合性能。

笔者选用Bi4Ti3O12作为铁电相,CoFe2O4和Ni0.37Cu0.20Zn0.43Fe1.92O3.88为铁磁相,分别将他们用微波烧结的办法制备成层状复合材料,通过改变铁磁相的含量来调控两相的相对含量,以研究随铁磁相含量的变化材料性能的变化。

1 实验

1.1 样品的制备

首先是Bi4Ti3O12和CoFe2O4前驱体粉体的制备,按照化学计量比称量所需原料Bi2O3(99.0%)、TiO2(99.8%)、Fe2O3(99.9%)、Co3O4(99.5%),置于120 ℃的烘箱内干燥12 h,其中Bi2O3过量3wt%用来弥补烧结过程中Bi挥发造成的损耗。分别经混合、过筛、预烧(750 ℃保温12 h),得到BIT粉体,然后二次球磨、造粒,放置备用。相同的方法合成CoFe2O4粉体,配置后球磨混合、过筛、预烧(1 000 ℃保温4 h),造粒。将造粒后BIT和CFO按(1-x)BIT/xCFO(x=0.2,0.4,0.6,0.8)进行称量,以BIT、CFO、BIT的顺序放入直径为10 mm的圆形模具中,垒层叠压成形,使用冷等静压250 MPa压制,将压制后的复合材料在950 ℃高温下保温3 h,得到三明治结构的磁电复合材料BIT/CFO。

1.2 材料结构表征及性能测试

采用日本Rigaku公司生产的D/max2200PC型X射线衍射仪对晶体结构和物相进行分析;采用日本JEOL公司生产的JSM-6460LV型扫描电子显微镜(SEM)表征复合材料的微观结构和形貌;采用E4980A阻抗分析仪对所制得的陶瓷样品介电常数和介电损耗进行测量;采用美国Lakeshore公司生产的7307型振动样品磁强计对样品的磁性能进行测试;样品的磁电性能是由自主搭建的仪器进行测试的,包括电磁铁,探测线圈,函数信号发生器,信号放大器和示波器等。

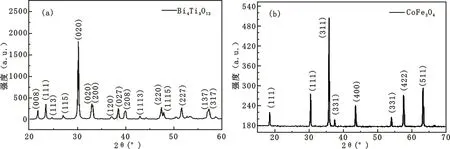

(a)950 ℃下制备的纯相BIT (b)1 150 ℃下制备的纯相CFO的XRD图谱

图1 BIT/CFO复合材料的XRD图谱

Fig.1 XRD patterns of BIT/CFO Composites

2 结果与讨论

2.1 物相和微观结构分析

图1(a)和图1(b)为纯相的Bi4Ti3O12和CoFe2O4在750 ℃下预烧粉体的XRD图,从图1中可以很清楚地看出,样品中只存在主晶相BIT和CFO,并不存在其他杂相,并且BIT为四方晶相,CFO为尖晶石相。

图2为970 ℃下烧结而成的BIT/CFO复合材料的SEM扫描图谱。

图2 BIT/CFO层状复合材料的扫描图谱Fig.2 SEM results of the representative BIT/CFO laminate composite

从图2可以看出,片层状的晶粒为BIT,多面体状的晶粒为CFO,晶粒发育完好,无杂相生成,致密度较高,没有明显的缺陷。在BIT和CFO之间,有一处明显的物相分界线,在物相分界线之间没有其他物相出现。其证明了BIT和CFO能够很好地共烧在一起。

2.2 电学性能分析

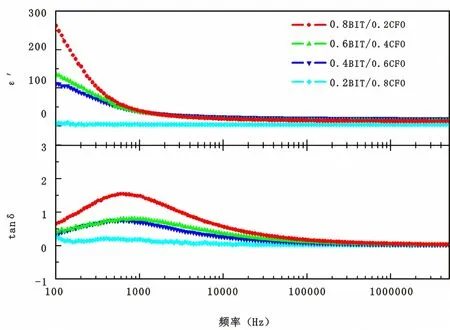

图3为BIT/CFO层状复合材料的介电频谱。从图3中可以观察到,随着CFO含量的增加,BIT/CFO层状复合材料的介电常数在减小,介电损耗在增大,这是因为CFO的介电常数比BIT小且CFO的电阻率低,介电损耗比较大的缘故造成的。

图3 BIT/CFO层状复合材料的介电频谱图Fig.3 Frequency dependence of the dielectric properties of the BIT/CFO composites

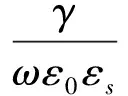

在低频下,对于BIT/CFO层状复合材料而言,在两种不同的物相界面处存在有界面极化,也就是空间电荷极化。根据双层麦斯威尔的界面极化机制,不均匀的结构可能会导致空间电荷极化。缺陷空间电荷的聚集在电场作用下层间,这些都会严重影响介电常数[14]。在高频时,空间电荷极化跟不上电场的变化,导致介电常数迅速降低。介电损耗主要分为极化损耗和漏导损耗。当处于交变电场下时,极化损耗和漏导损耗均会增大。因此,把介电损耗用公式(1)表达:

(1)

式中: D——介电损耗tanδ;

Dp——极化损耗;

DG——为漏导损耗。

从式(1)中可以看出,当ω→0时,Dp→0,这时介电损耗均是由漏导损耗贡献。从这里得出ωτ≤1,所以式(1)还可以表达为:

(2)

由于介电损耗与频率成反比,所以在低频下频率增大时介电损耗快速减小。

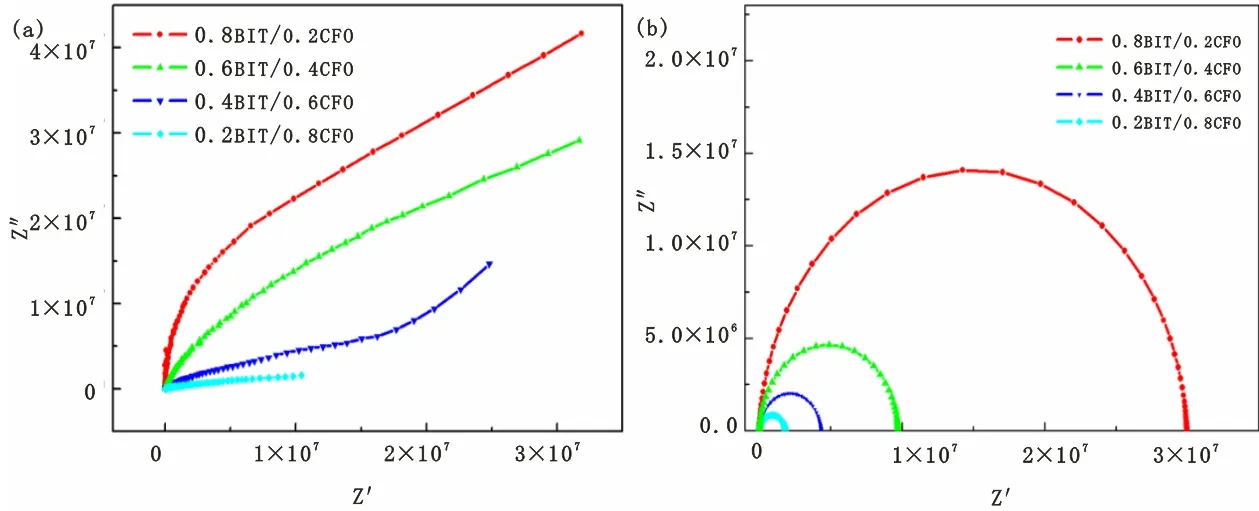

图4为BIT/CFO层状复合材料的室温阻抗图谱。

图4(a)为BIT/CFO层状复合材料的复阻抗图谱,图4(b)为BIT/CFO复合材料的模拟曲线图。从图4中我们得以观察到,随着随着CFO含量的增加,复合材料的阻抗越来越小,这是由于铁磁相CFO的阻抗比BIT小造成的。

(a)材料的复阻抗图谱的尼奎斯特图 (b)材料阻抗的模拟曲线图

图4 BIT/CFO层状复合材料的室温阻抗图谱

Fig.4 Room temperature impedance spectra of BIT/CFO layered composites

要分析阻抗图谱,对其进行了电路拟合,2-2型层状的复合材料可以被看成是电阻和电容并串联混合的电路,可以得出以下公式:

Z*(ω)=(R-1+jωC)-1=Z'(ω)-jZ"(ω)

(3)

Z'(ω)=R/[1+(ωRC)2]

(4)

Z"(ω)=ωR2C/[1+(ωRC)2]

(5)

(6)

从图4中可以明显得观察到,BIT/CFO复合材料的Z'和Z"值均随着CFO含量的增加而增加。CFO的含量分别为0.2、0.4、0.6和0.8时,对应的电阻R值分别为1.2×108Ω,5.8×106Ω、2.23×106Ω和1.1×106Ω,这说明,随着铁磁性CFO含量的增加,会弱化BIT/CFO复合材料的电阻率。

结合阻抗图谱和漏电流图谱可以得出,这两者之间是存在密切联系的,阻抗的样品其漏电流密度小,反之阻抗小的漏电流密度大,这两者之间的关系可以用公式(7)来描述:

(7)

图5为BIT/CFO层状复合材料的漏导电流图谱。

图5 BIT/CFO层状复合材料的漏导电流图谱Fig.5 I-E curves of the BIT/CFO composites

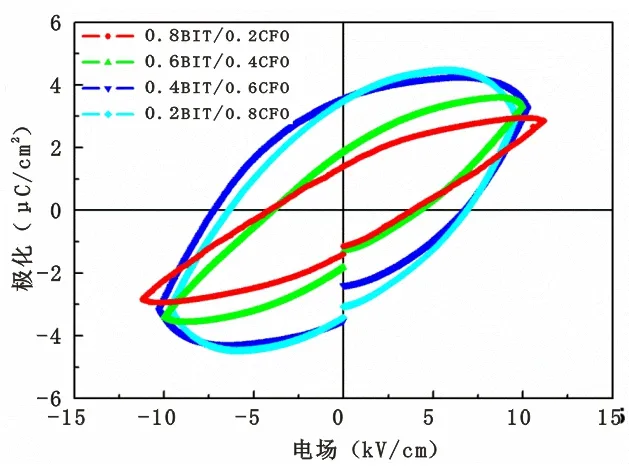

图6为BIT/CFO层状复合材料的室温电滞回线图谱。

图6 BIT/CFO层状复合材料的电滞回线图谱

Fig.6 Polarization hysteresis (P-E) loops of BFO-BT/CFO composites

从图6中可以看出,BIT/CFO层状复合材料表现出了典型的铁电体的电滞回线。随着CFO含量的增加,BIT/CFO层状复合材料电滞回线图形表现的越来越圆,在电滞回线测量的过程中,所测得的室温电滞回线图谱不仅是极化曲线,它还包括漏电流,极化电荷,损耗等情况。并且漏电流在其中占据了很大的地位,因为图像中的曲线包围的面积反映出材料的损耗情况。铁电体受漏电流影响时漏电流越大,损耗越大,其电滞回线就会越圆[15]。

2.3 磁学性能分析

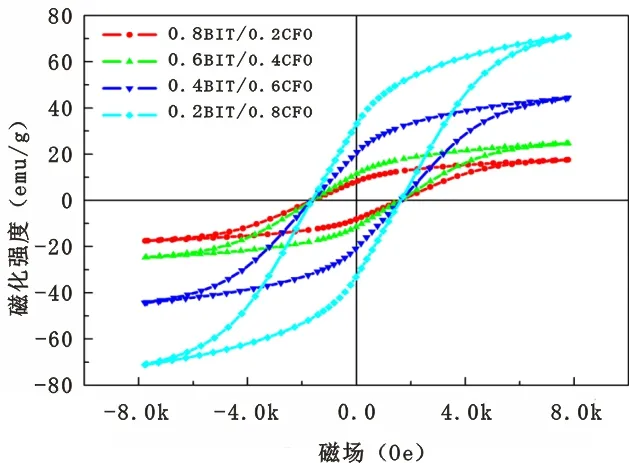

图7为BIT/CFO层状复合材料的磁滞回线图谱。

图7 BIT/CFO层状复合材料的磁滞回线图谱

Fig.7 Magnetic hysteresis (M-H) loops of the BIT/CFO composites

从图7中可以观察到,CFO含量为0.2、0.4、0.6和0.8时,复合材料的饱和磁化强度为19 emu/g,23 emu/g,42 emu/g和70 emu/g。随着铁磁相CFO的增加,BIT/CFO层状复合材料的饱和磁化强度增大。表明磁电复合材料的铁磁性直接取决于铁磁相,而与铁电相无关,随着铁电相的加入,复合材料体系中的磁性能被稀释,导致饱和磁化强度降低。

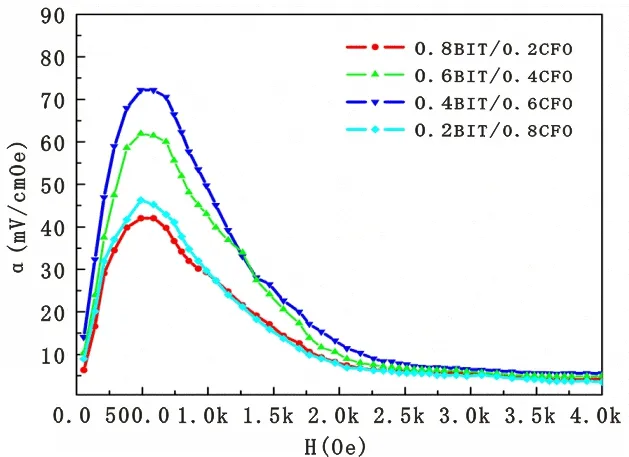

图8为BIT/CFO层状复合材料的室温下磁电耦合系数随磁场强度变化的关系图谱。

图8 BIT/CFO层状复合材料的磁电耦合系数随外加磁场强度变化的关系图谱

Fig.8 ME coefficient as functions of magnetic field for BIT/CFO composites

从图8中可以看到,随着磁场强度的增加,BIT/CFO复合材料的磁电耦合系数先增大而后减小。当磁场强度处于400 Oe左右,BIT/CFO复合材料磁电耦合系数达到一个峰值。其中0.4BIT/0.6CFO层状复合材料的最大磁电耦合系数为αE=73 mV/cm Oe。伴随着磁场的变化,材料的磁电耦合系数先增大而后减小,当磁场较小时,随着磁场强度的增大,材料内部磁距的磁致伸缩性能变好,导致材料磁电耦合系数增大。但是与此同时,其内部的退磁场也在不断增大。当磁场继续增大时,磁致伸缩达到饱和,体系内部磁致伸缩量不再得到增大,退磁场依旧增加,导致磁体难以被磁化,从而引起磁电耦合系数减小[16]。

3 结论

采用微波烧结法制备出BIT/CFO层状磁电复合材料,铁电相和铁磁相之间可以很好的共烧在一起,可以在高温下共存,且不会发生反应以及明显的原子扩散现象,使得它们在复合材料中可以保持自己的物理特性。通过研究材料的电性能发现,材料的阻抗随铁磁相含量的增加而减小,漏导电流随铁磁相含量的增加而增大,随铁磁相含量的增加,材料的介电常数逐渐降低,击穿场强减小,材料损耗逐渐增大,材料铁电性能得到一定的弱化。由于引入铁磁相,M-H磁滞回线变成了标准的S型回线,随铁磁相含量的增加,材料铁磁性得到显著提高。随铁磁相含量的增加,磁电耦合系数先增加后减小,在BIT/CFO层状复合材料中,当CFO含量为0.6时,材料磁电耦合系数最大为72 mV/cm Oe。