基于CMOS传感器的高性能图像采集系统设计

任勇峰,王国忠,储成群,焦新泉

(中北大学,电子测试技术国家重点实验室,山西太原 030051)

0 引言

CMOS图像传感器是一种新型的科学级集成芯片,其内部采用全新的集成电路制造工艺,在速度、分辨率、动态范围和读出噪声等方面都有了较好的改进和提升,再加上其本身所拥有的体积小、质量轻、功耗低、开发简单容易的优点,为高性能图像采集系统的发展提供了新的方向[1]。本设计采用低功耗CMOS图像传感器MT9P031作为图像采集前端,设计了一套高性能、小型化、低功耗的图像采集系统。

1 总体方案设计

系统总体方案设计如图1所示,由图像采集模块、控制模块、数据传输模块3部分组成。图像采集模块采用MT9P031 CMOS图像传感器作为图像采集系统的前端,通过配置其内部寄存器从而使其正常工作,把12位图像数据、帧同步信号FV、行同步信号LV以及像素时钟PIXCLK输出到控制模块;控制模块分为FPGA控制模块和DDR2控制模块,FPGA控制模块通过接收采集模块传来的FV和LV来控制DDR2缓冲图像数据,同时接收传输模块下发的配置命令来重新配置采集模块和接收重传命令实现数据重传,DDR2控制模块主要控制数据的存储和接收重传数据的地址,从而找到需要重传的数据,再把数据重新上传到传输模块;传输模块负责把图像数据通过网线上传到上位机软件,进行图像显示,同时还接收上位机软件下发曝光、增益、图像分辨率等配置命令,然后传输到控制模块实现对采集模块的配置,如果上位机软件校验数据有误的话,还会下发重传命令。

图1 总体方案设计

2 系统硬件电路设计

2.1 FPGA硬件设计

FPGA作为系统的硬件控制核心,在整个图像采集系统中占有重要地位,负责对CMOS图像传感器的控制以及对采集的图像数据进行解码,并把解码后的图像数据缓冲到DDR2中,同时解析上位机软件下发的命令,把图像数据实时上传到上位机进行图像显示。所以本系统选择内部资源丰富,处理速度快的XC6SLX45-2CSG324I作为主控芯片。

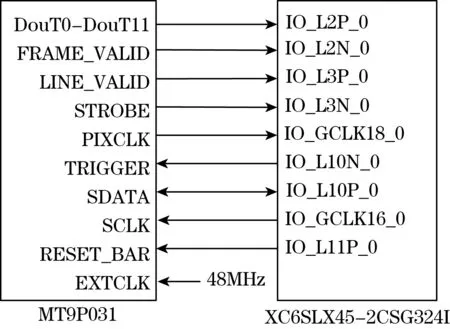

2.2 CMOS传感器硬件电路设计

本设计在提高图像清晰度的同时为了降低整个系统的功耗以及满足小型化的设计,采用了低功耗CMOS图像传感器MT9P031作为图像采集前端,MT9P031最高分别率可达2592H×1944V(500万像素)、最大帧频可达60 帧/s,内部集成了12位A/D转换器,可以同时输出12位数字图像数据,为整个系统提供了图像数据的来源,图2为MT9P031与FPGA的硬件连接图[2]。

图2 MT9P031与FPGA的硬件连接图

MT9P031图像传感器采用独立的48 MHz外部有源晶振作为其输入时钟,再通过内部PLL控制器产生像素时钟,然后经PIXCLK引脚输出到外部控制器,其最大输出像素时钟达96 MHz;FRAME_VALID、LINE_VALID分别为图像数据的帧同步信号和行同步信号,供外部控制电路读取图像数据流;STROBE信号为触发信号的输出使能信号,当触发快照有效时,STROBE信号为高电平输出;TRIGGER信号为快拍照触发信号,即当外部只需要1帧图像数据时,此信号有效,通过控制内部寄存器来输出1幅图像数据;SDATA为I2C总线的双向数据线、SCLK为I2C总线的时钟信号线,FPGA通过I2C总线对MT9P031内部寄存器进行配置,主要配置的寄存器有起始位置、图像大小、曝光时间、增益;RESET_BAR为复位信号,当上位机重新配置图像传感器的有关参数时,FPGA要对MT9P031进行复位操作,清空寄存器原始数据,并对其进行重新配置[3]。

2.3 以太网硬件电路设计

本设计根据实际需求采用千兆以太网进行数据传输,使用88E1518作为千兆以太网的物理层(PHY)芯片,通信协议采用UDP通信协议。FPGA控制器通过RGMII总线与88E1518物理层芯片进行数据传输,88E1518再把图像数据通过网线传输到上位机软件进行图像显示。

图3为千兆以太网的硬件电路图。千兆以太网是全双工数据传输模式,TXD[3:0]和RXD[3:0]分别为4位并行接收和发送数据线,在时钟的上升沿和下降沿都进行数据传输,因此其在一个时钟周期内实际传输的数据位数为8位;TX_CLK与FPGA的全局时钟线相连,可提供高达125 MHz的接口频率,伴随数据一同输出到物理层芯片;TX_CTRL为发送数据的使能控制信号线,该信号高电平有效,通过FPGA内部的以太网控制器来控制何时输出数据;RX_CLK同样与FPGA的全局时钟线相连,可接收高达125 MHz的时钟频率,伴随数据一同输入到FPGA内部;RX_CTRL为接收数据使能控制信号线,物理层芯片发送数据时,同时发送一个使能控制信号,当FPGA判断该信号为高电平时,开始接收数据;MDC和MDIO为寄存器可配置引脚,通过该引脚配置88E1518内部寄存器;RESETn为88E1518物理层芯片的复位引脚,每次上电之前以及传输完1包数据时进行复位,该引脚为低电平时复位有效;RSET为恒压基准引脚,该引脚通过外部4.99 kΩ电阻连接到地上,将该引脚拉低使芯片在恒压下才可以正常工作;CONFIG为88E1518硬件可配置引脚,而本设计采用了标准以太网协议,所以将该引脚接地。ZXRJ-286-02NL为网口,其内部是通过4个变压器实现与网线之间进行数据传输,所以在画PCB板图时,把其下面的铜全部扣掉,避免引入电磁干扰[4]。

图3 以太网的硬件电路

2.4 供电电路硬件设计

本系统采用外部24 V供电,然后通过电源芯片TPS54331将其转为5 V,供FPGA、DDR2和以太网电源芯片以及图像传感器的稳压芯片使用。为了避免单个电源芯片功率不够以及电源之间相互干扰的影响,本设计采用了各个模块独立供电,互不干扰,图4为电源芯片TPS54331的硬件电路图[5]。

图4 TPS54331硬件电路图

该电源芯片为输入和输出均可调的DC-DC电源管理芯片,芯片内部集成了欠压锁定电路,当电压低于一定数字时,该芯片使能无效,不再工作,从而提高了输出电源的可靠性、安全性以及稳定性,为本系统提供了稳定的外部输入电源。输入使能电压可以通过R2、R3来调整,其可调范围为7~28 V,输出电压通过R1、R5来调整,调整结果为Vout=0.8×(R1/R5+1),本设计需要输出电压为5 V,通过计算得R1、R5阻值为53.6 kΩ和10.2 kΩ。

3 逻辑设计

3.1 图像数据采集前端逻辑设计

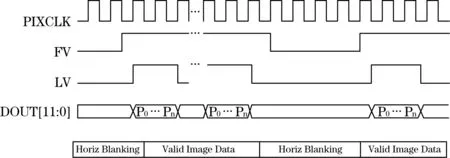

MT9P031图像传感器采集的数据是原始图像数

据,除了将12 bits的原始图像数据和由片上锁相环产生的表示像素点采样频率的像素时钟PIXCLK输出到FPGA,还同时将帧同步信号FV和行同步信号LV输出给FPGA,作为1帧图像数据和1行图像数据结束的标志位[6]。当PIXCLK为高电平,FV同时也为高电平时则说明有效数据开始采集,当像素时钟PIXCLK的下降沿到来时则预示着图像数据的产生,并且此时外部不断读取图像数据,直到下一个帧同步信号FV的上升沿到来时,1帧图像数据采集结束,图5为图像采集前端的逻辑设计时序图。

图5 图像采集前端逻辑设计时序图

根据实际需求,本设计只读取了MT9P031图像数据的高8位,作为本系统图像数据的来源。图6为逻辑分析仪的截图,图中显示了在帧同步信号FV为高电平期间,行同步信号LV出现2次高电平的波形图,当行同步信号LV为低电平期间,输出的图像数据全为0时,此时处于场消隐区[7]。当FV和LV均为高电平期间,输出有效的图像数据,在此期间像素时钟PIXCLK每出现一个下降沿,便输出1位数据,当行同步信号LV为高电平期间,共输出2 592位数据。也即是在1帧图像数据中帧同步信号FV为高电平期间,行同步信号LV出现1 944次高电平,当下一个帧同步信号FV的上升沿到来时说明分辨率为2 592×1 944的图像数据采集结束。可以通过配置MT9P031图像传感器内部寄存器的值,来改变图像传感器的分别率[8]。

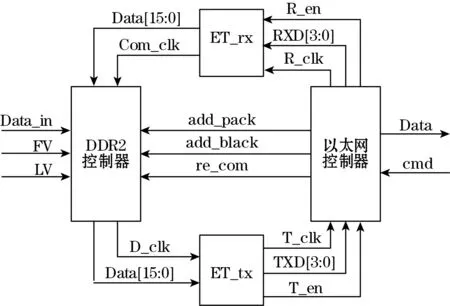

3.2 以太网重传逻辑设计

本设计为了提高系统的可靠性,在以太网控制器中增加了重传的逻辑设计模块。当图像数据上传到上位机软件的缓冲区,经上位机校验如果发现数据有丢失或有误时,下发一个重传指令并中断数据上传,同时把丢失或有误的数据地址以及对应的包地址下发给FPGA控制模块,然后FPGA控制模块再控制DDR2控制器把有误的数据重新送到以太网传输模块实现重传,图7为重传逻辑设计图。

图7 重传逻辑设计图

DDR2控制模块接收图像传感器采集的图像数据,并按每个bank存储1帧图像数据的格式进行缓冲,然后DDR2控制器每次以16位数据传输到以太网发送模块,在时钟的上升沿和下降沿均进行数据传输。当以太网发送模块接收到发送使能信号时,把图像数据以4位数据位宽送入以太网传输模块,且在时钟的上升沿和下降沿均进行数据传输,然后以太网控制模块把图像数据上传到上位机软件进行图像显示[9]。当以太网控制模块接收到重传指令以后中断数据上传并同时把包地址add_pack和块地址add_black下发到DDR2控制模块中,然后DDR2控制模块通过块地址找到缓冲区对应的图像数据,并把数据重新送到以太网发送数据模块ET_tx,然后控制使能发送,从而实现数据的重传。

4 结果分析及验证

本系统采用MT9P031作为图像采集前端,采集到的图像分辨率为2 592×1 944,帧频为14帧/s,且显示为256级8位灰度图像,因此每s采集到的数据量为68 MB(2 592×1 944×14 B),即采集1幅图像需要72 ms[10]。DDR2工作在125 MHz时钟下,其传输速度峰值高达500 MB/s,除去其自动刷新、预充电、状态信息等消耗的时钟,实际平均数据吞吐量为456 MB/s,通过计算读取1幅图像所需要的时间为11 ms。千兆以太网的传输速度为125 MB/s,传输1帧图像数据需要52 ms,通过逻辑分析仪发现重传1帧图像数据需要130 ms,而DDR2中可以缓冲8幅图像,通过分析,本系统除了可以正常工作外,还可以实现数据重传。而且经过长时间重复测试,在没有上位机引起其他开销的情况下,采集的图像如图8所示。其画面清晰、流畅,且实时性较好,证明了本系统能够实时进行图像数据上传,且稳定可靠。

图8 采集的图像截图

5 结束语

本设计中,采用了低功耗、高分别率、高集成度的MT9P031图像传感器作为图像采集前端,采用传输速度快、而且稳定可靠的千兆以太网作为数据传输接口,设计了一套高性能图像采集系统,显著降低了整个系统的功耗,同时实现了小型化的设计思想,在逻辑设计中增加了重传模块,提高了图像数据的可靠性,确保图像显示的准确率。