基于高速eMMC阵列的视频存储系统设计

丁红晖,马游春,张 衡,顾泽凌,杨明远,吴正洋

(1.中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051;2.上海无线电设备研究所,上海 200090)

0 引言

随着视频采集技术的快速发展,视频存储设备已经越来越广泛地应用在各个行业中,它的出现为人们生活提供了许多便利,成为社会发展中必不可缺的一部分。根据人们对大容量存储、高带宽传输的需求,文章提出了一种基于高速eMMC(embedded multi media card,嵌入式多媒体卡)阵列的视频存储系统设计,由于eMMC存储芯片具有高集成度、高速读写传输、低功耗、高性能等特点,使得视频数据读写速度翻倍递增,存储容量扩大[1]。同时由于内部集成控制芯片可以自我管理坏块及错误检测与纠正,使得通过FPGA操作起来更加简单方便,仅需控制数据的读写操作过程即可,很好地节约了系统的资源[2]。

1 视频存储系统的硬件设计

视频存储系统主要由FPGA(field programmable gate array,现场可编程门阵列)主控模块、eMMC阵列存储模块、DDR3(double date rate 3,双倍数据速率的同步动态随机存储器)缓存模块、网口读数模块、电源模块及相机接口电路组成。FPGA主控模块实现对外设缓存、存储阵列和网口传输的控制;eMMC存储模块实现对视频数据的存储与读取;DDR3模块完成FPGA对eMMC阵列进行写操作时的数据缓存;网口读数模块实现上位机与存储系统的命令控制与数据通信;电源模块负责为整个系统供电,并通过电源管理芯片为每个模块提供所需的电压;相机接口电路完成视频图像数据的接收和信号的转换[3]。总体设计框图如图1所示。

图1 总体设计框图

1.1 相机模块设计

系统选用基于CMOS传感的工业相机,与传统摄像机相对比而言,具有很高的图像稳定性和抗干扰能力。型号选定为STC-CMC200PCL,可实现2 048×1 088最高分辨率,333 帧/s的最高帧频率,配备标准的Camera-Link接口。在Camera-Link总线上,选择对分辨率为1 280×720、帧速率为200 帧/s的视频图像进行采集,则1 s的数据量为1 280×720×200 B,即176 MB/s。像素数据信号以串行差分的形式进行传输,输出的信号需要通过串转并芯片DS90CR288A进行转换,将1路差分时钟信号和4路串行差分数据信号转换成1路TTL时钟信号和1个28位的并行TTL信号,通过PLL来统一时钟与数据信号,输出稳定的TTL信号[4]。

1.2 存储模块设计

系统采用10片eMMC并行的方式进行同步读写。选用MTFC16GJVED-4M IT作为数据存储芯片,单片容量为16 GB,可支持最大的时钟速率为52 MHz,连续写数据20 MB/s,连续读数为44 MB/s。单块eMMC芯片共有10根信号控制线,8根数据线DAT7-DAT0,1根时钟线CLK和1根命令线CMD。系统采用10片eMMC阵列并行的方式进行同步读写,写入速度达到200 MB/s,读出速度为440 MB/s,存储容量共计160 GB。并行传输方式将80根数据线、10根命令线CMD并行连接到FPGA上,通过片选信号选择读取每片eMMC的数据,在硬件实现上这个架构是切实可行的[5]。eMMC并行传输架构如图2所示。

图2 多片eMMC并行框架

2 视频存储系统的软件设计

2.1 系统软件设计

FPGA程序在开发环境Vivado中通过VHDL语言编写,图3为整个系统工作的流程图。

图3 系统工作流程图

2.2 视频数据接收模块逻辑设计

2.2.1 相机数据输出格式

系统图像数据通过Camera-Link接口的Base模式进行传输,每个像素时钟PixelClock以3×8 bits的方式输出,相机输出的数据含有帧有效信号FVAL、行有效信号LVAL、图像数据、数据有效信号DVAL和保留信号SPARE。

在相机的CMOS感光器件曝光1帧画面后,等待8 s左右,帧有效信号FVAL升为高电平,经过1个像素时钟PixelClock,数据有效信号DVAL和行有效信号LVAL同时都被相机拉高,再待时钟像素PixelClock的上升沿来临时,输出像素数据。此刻相机输出的像素信号为真实有效信号[6]。

2.2.2 视频数据接收

视频数据接收模块是对图像有效信号的采集,并为视频数据输入给FPGA提前做好准备。主要包括帧标志的写入和每帧画面的数据接收。帧标志的插入是为了在上位机读数时可以方便截取有效信号[7]。其逻辑流程图如图4所示。

图4 视频数据接收流程图

首先系统对数据接收模块进行初始化,待初始化结束后开始判断帧有效信号,帧有效信号正确的变化方式是从低电平升为高电平,若过程中帧有效信号持续为低则一直等待。帧有效信号升高后开始判断行有效信号,因为行有效信号的变化与帧有效信号的变化是同步的,故此时也为高电平,若不是则等待直到为高。接下来在时钟上升沿到来时便可以取数,帧行有效信号皆为低,取数结束,写入帧标志,开始下一帧的采集[7]。

2.3 eMMC阵列逻辑设计

系统采用10片容量共为160 GB的eMMC阵列进行数据存储,通过高速SDR模式进行数据传输,时钟速率选用40 MHz,4位的传输位宽,即1个字节分2次传输,先传高4位,再传低4位。经计算理论峰值速度为40 MHz×4 bits×10,即200 MB/s。在每条数据线上都具有CRC校验,保证数据传输的正确性和完整性[8]。

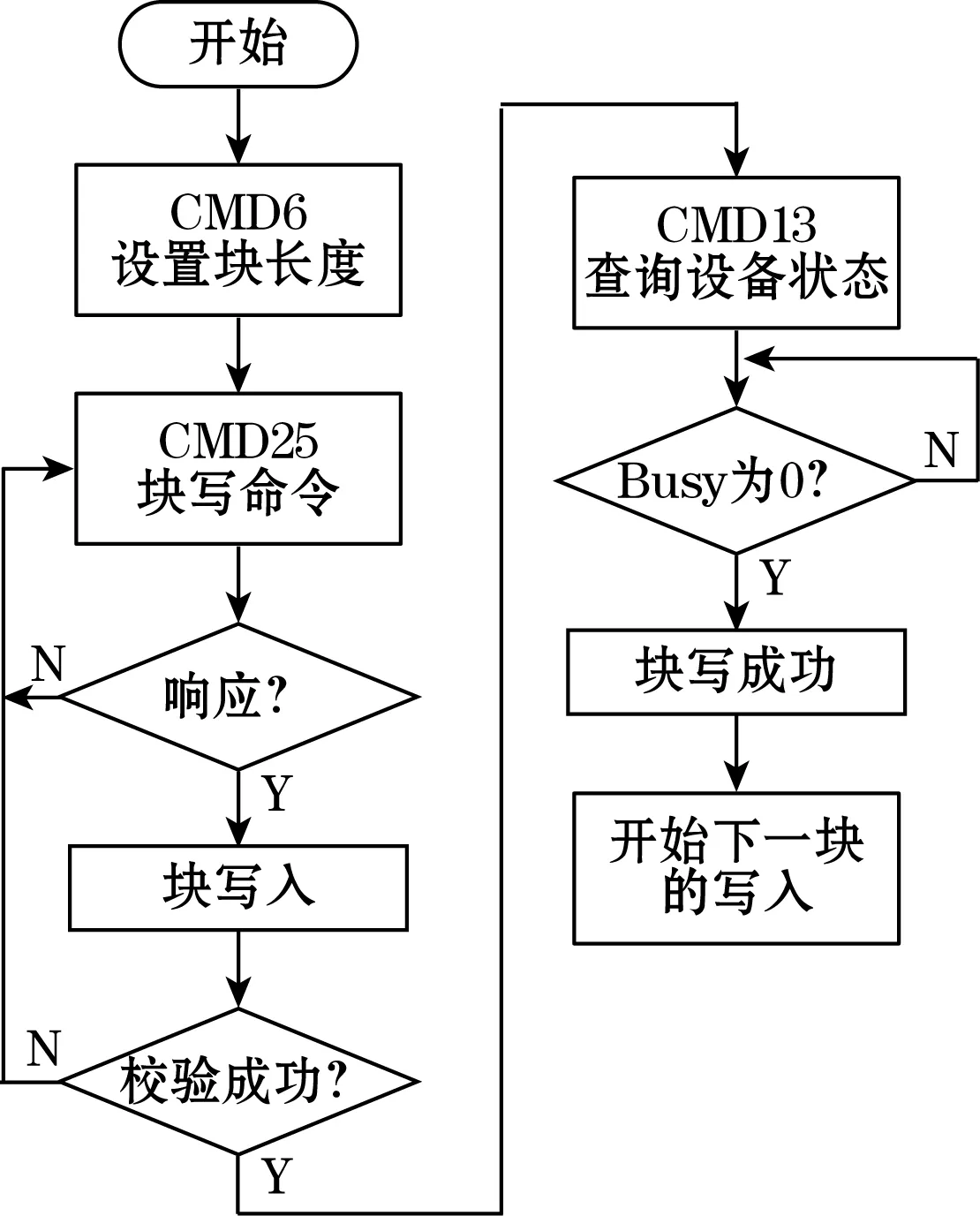

2.3.1 eMMC阵列写数据流程

在写操作开始之前,首先需要设置eMMC块长度,FPGA向eMMC阵列发送指令CMD6(0x5000-0000-09BB),令块长度设置为512 B。然后FPGA发送多块的写命令CMD25(0x5800-0000-006F),包含起始地址,若阵列块收到指令且不响应错误,则开始数据写操作,但只要命令CMD25响应错误或超时就需要再次发送。在每个块传输完毕后,eMMC会向FPGA发送回复检测CRC,如果CRC校验正确且eMMC

处于不忙状态,FPGA就会发送下一块的数据,若BUSY标志位为高,则一直等待直到为低,完成当前的写操作。在发送数据时,FPGA也可以查询eMMC的状态寄存器,对设备存在的任何新的状态信息进行检测[9]。当FPGA发送停止指令,写操作结束。eMMC阵列写流程如图5所示。

图5 eMMC阵列数据写流程图

2.3.2 eMMC阵列读数据流程

在阵列读操作开始时,同数据写操作流程一致,首先发送CMD16(0x5000-0000-09BB)命令设置块的长度,待块长度设置结束后,开始发送eMMC阵列读命令CMD17(0x5100-0000-0055),包含读起始地址参数,等待读命令是否响应,若未响应待2 s后再次发送写命令CMD25,响应成功则进行阵列写入,写入结束后会有CRC校验,若校验成功,就完成阵列数据有效的读出,若失败,则返回阵列读命令CMD17重新开始读取数据。接下来发送命令CMD13查询设备状态,同数据写流程,直到BUSY位为低,读数据流程结束[10]。图6为eMMC数据读过程的信号捕捉图,data_out显示的是读出的64位递增数据。

图6 eMMC数据读过程的信号捕捉图

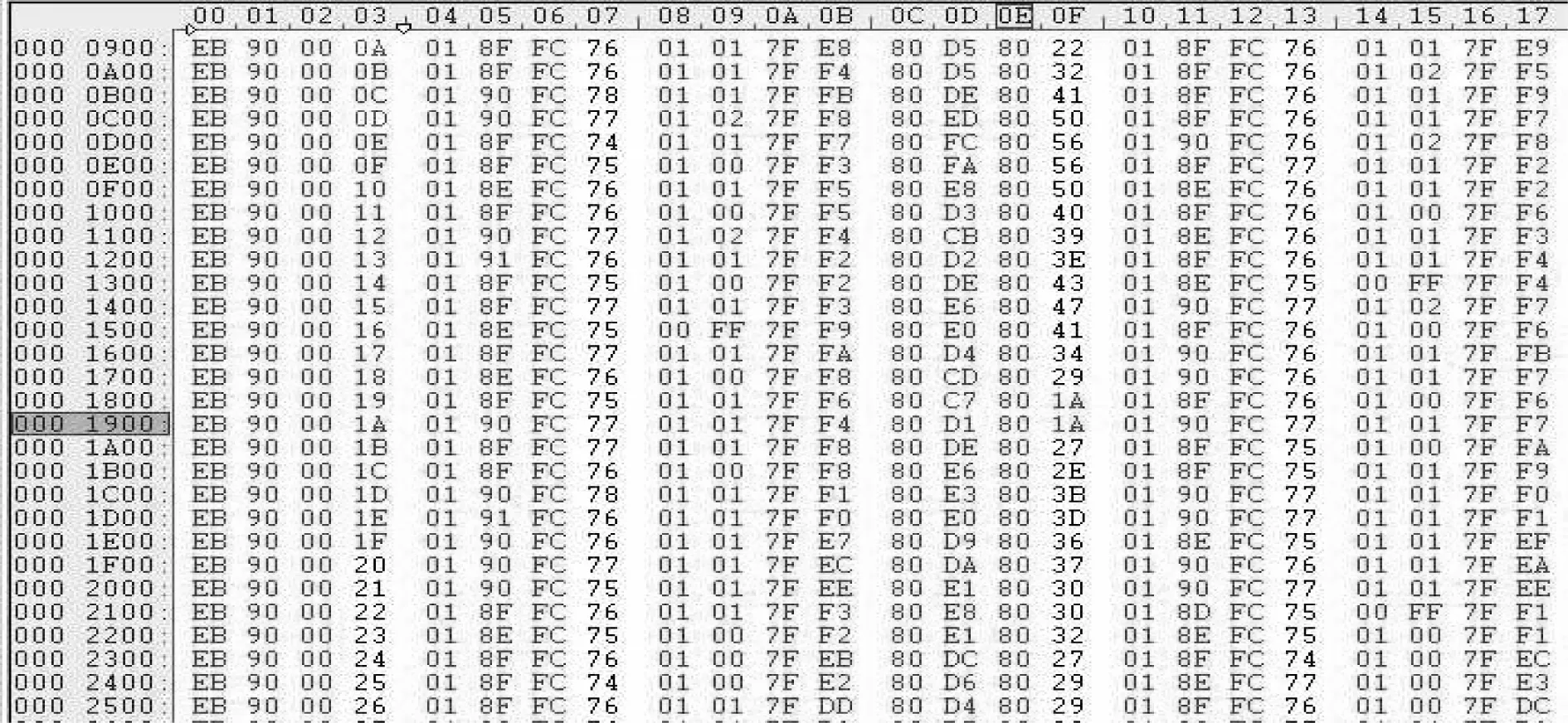

3 图像显示测试

为验证相机采集数据的准确性,采集后将视频图像数据读出保存为.dat文件。回读的原始数据如图7所示,第一和第二列为数据的帧头,第三和第四列为数据的帧计数,第五到第十六列为采集到相机的数据[11]。在采集过程中,没有出现丢帧和错帧的现象,为检验相机采集数据的准确性,需要将数据转化为直观的图像以便于验证。通过使用上位机软件生成.bmp图像,对螺钉落入水中溅起水花的某一帧画面进行显示,如图8所示,表明相机采集到的图像数据是准确的。

图7 采集的data文件

图8 通过上位机还原的一帧图像

4 结束语

文章提出的视频存储系统以FPGA作为主控制器,采用Camera-link视频总线接口,以多块eMMC阵列作为存储介质,通过硬件设计和软件逻辑控制完成视频存储系统的设计。系统在40 MHz的时钟下,实现了对分辨率为1 280×720、帧频为200 帧/s的视频数据进行采集和存储,存储容量高达160 GB,写速度为200 MB/s。文章的创新点是采用eMMC阵列存储的形式,通过并行传输方式进行同步读写。经过实际试验,验证了系统设计能够采集到准确的图像画面进行显示。