RISC-V架构开源CPU的设计与实现

郭 勇 罗 乐 刘森态 付 强 马 超 刘娟秀 赖祥军

1.成都工业学院电子工程学院 四川 成都 611730

2.重庆邮电大学光电工程学院 重庆 400065

一、引言

集成电路是一个国家安全大门的钥匙,是整个电子信息产业皇冠上的宝石[1-2]。中央处理器(CPU)代表了集成电路的核心技术,我国在集成电路上的进口总金额已超过石油进口的总金额,近年我国已将发展集成电路产业,尤其是发展拥有自主知识产权的通用CPU芯片产业上升到国家战略高度,促使庞大的资本和人力涌入到集成电路设计领域。国内缺乏通用处理器的根本原因主要是指令集架构(ISA)的缺乏,目前广泛使用的x86架构、ARM架构、MIPS架构和PowerPC架构都被国外公司所垄断,需要支付高昂的授权使用费,而RISC-V架构对指令集完全开源,RISC-V基金会仅收取少量的授权费,使得RISC-V处理器越来越受到研究机构、学者和芯片设计领域的重视[3-6]。

二、RISC-V指令集架构的基本构成

本论文使用Verilog HDL语言实现了一个常用的47条指令二级可变流水线RV32I、重点分析了取值模块IFU、执行模块EXU,简要分析了异常和中断以及调试模块的E203 CPU系统。

RV32I指令集是RISC-V指令集架构下的基本的32位指令集,它规定了47条基本指令,包括了32位地址空间与整数指令,定义了32个32位通用整数寄存器。RV32I支持4种基本类型指令,格式非常规范,所有的指令都是固定32位,并且在存储器中以4字节对齐[7-8]。

三、基于RISC-V指令集的蜂鸟E203 CPU设计

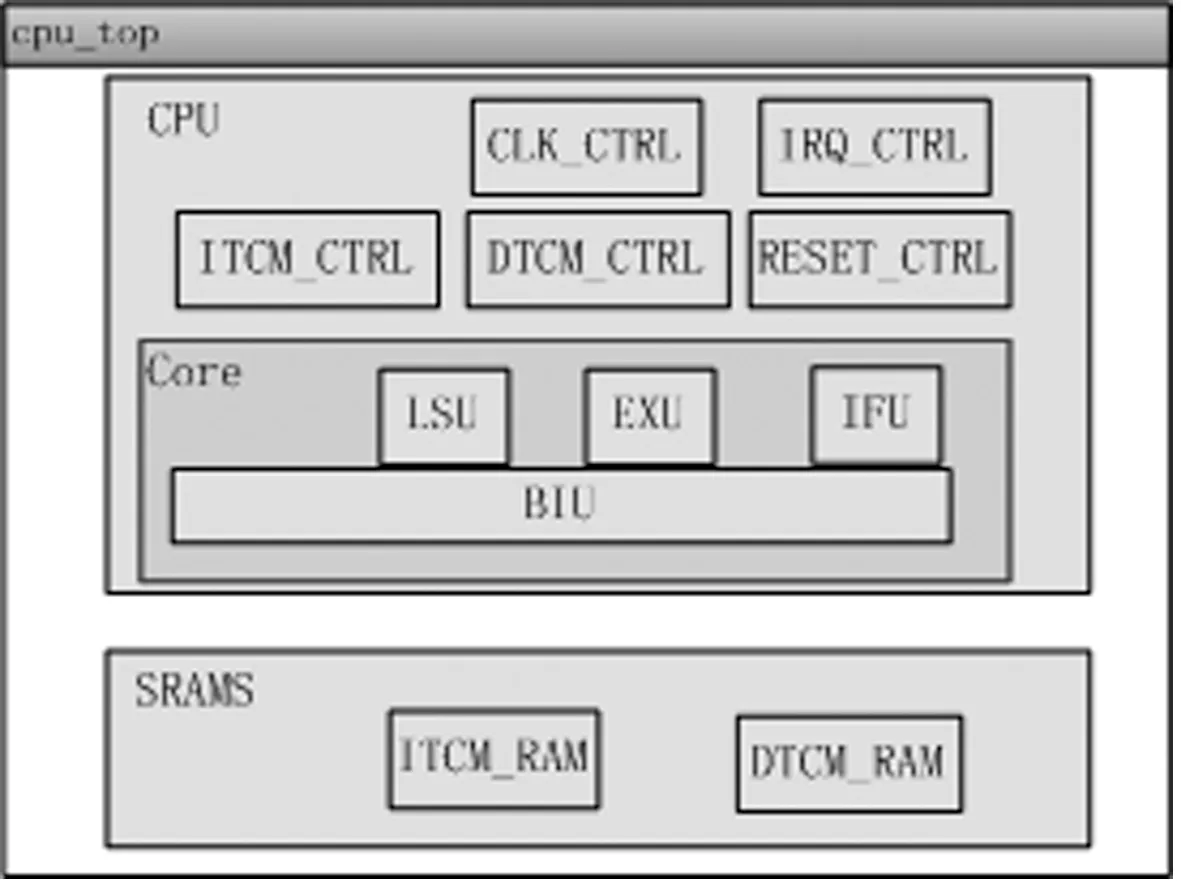

本课题基于RISC-V指令集设计了蜂鸟E203 CPU,其具体设计内容主要包括:(1)E203顶层设计。采用典型的Top-Down设计方法将CPU划分成多个模块,包括时钟门控(CLK_CTRL)、中断控制(IRQ_CTRL)、复位控制(RESET_CTRL)、ITCM访问控制(ITCM_CTRL)、DTCM访问控制(DTCR_CTRL)、取指单元(IFU)、执行单元(EXU)、存储器访问(LSU)、总线接口(BIU)。其顶层结构如图1所示。

图1 模块顶层设计结构图

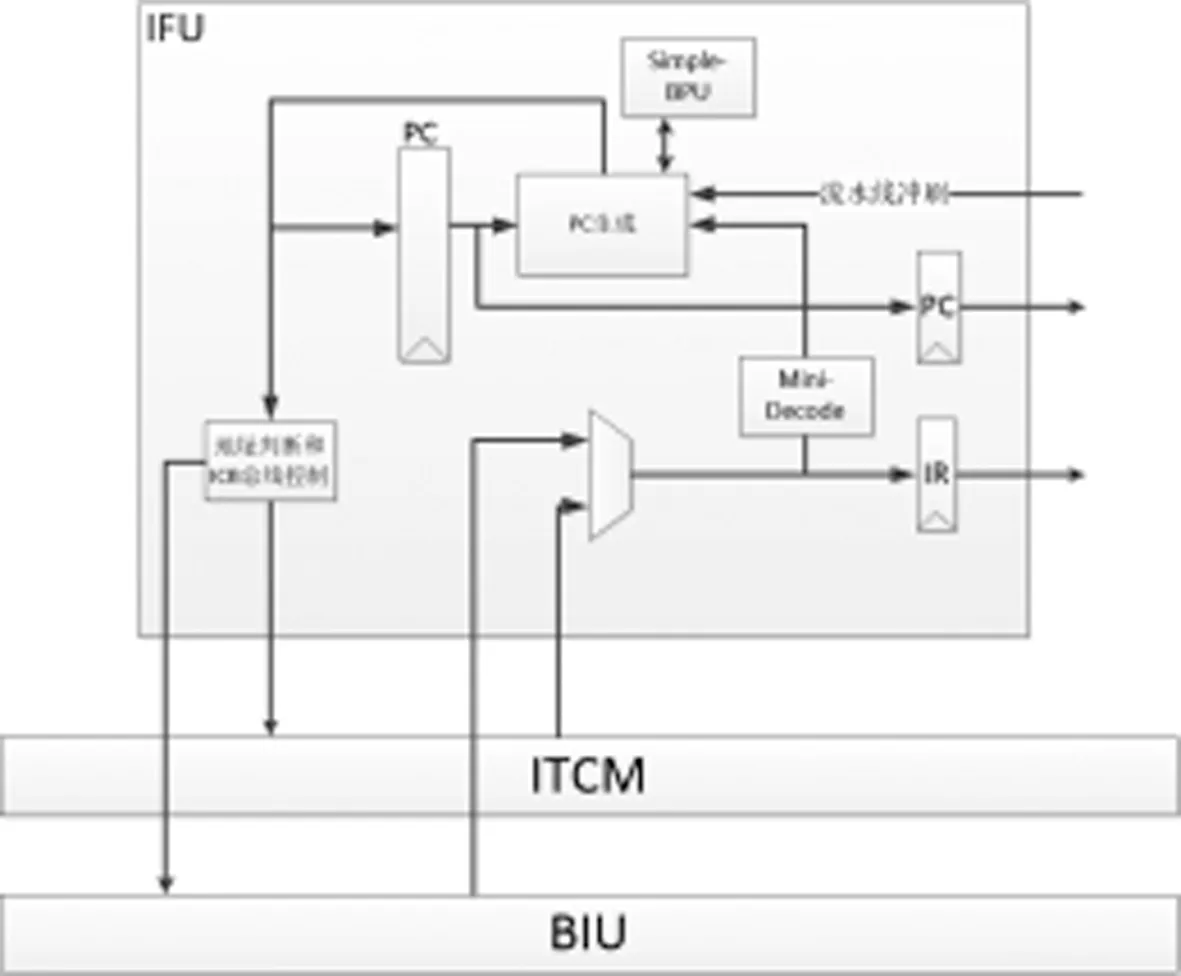

图2 IFU微架构图

(2)取值单元微架构。取指是流水线第一步,它要求以最快的速度且连续不断地从存储器取出指令供处理器核执行。在E203 CPU中利用Mini-Decode模块对取回的地址进行简单译码,使用Simple-BPU进行简单的分支预测,利用PC生成模块产生新取值PC地址,借助地址判断和ICB总线控制模块来访问PC地址所对应的ITCM或BIU。其微架构如图2所示。

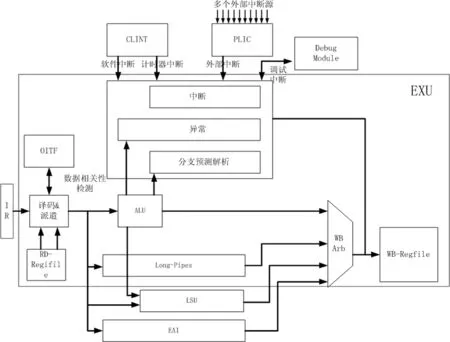

(3)执行单元微架构。蜂鸟E203 CPU的译码、执行、交付和写回均在EXU模块中运行。从IFU模块取出指令后,执行单元首先通过译码和派遣模块完成指令译码和派遣,接着将译码出的操作数,借助RD-Regfile模块读取Regfile,同时将指令派遣给不同的运算单元,例如算术模块ALU、长指令模块Long-Pipes、寄存器访问模块LSU、以及扩展协处理器EAI。如果在程序执行过程中有中断、异常以及带条件跳转指令,则通过交付模块判断是否进行流水线冲刷。在长指令执行过程中,使用OITF模块维护长指令的数据相关性。最后,通过WB-Regfile模块完成指令运算结果的写回。EXU微架构如图3所示。

图3 EXU微架构图

(4)总线接口单元微架构。BIU使用标准的ICB总线接口,主要负责接收IFU和LSU单元的存储器访问请求并判断出访问地址区间从而访问不同的外部接口。BIU有两组输入ICB总线接口,两组输入ICB总线经过ICB汇合模块仲裁优先级汇合成一组。通过使用Ping-Pong Buffer模块解决流水线反压时序问题。接着通过地址判断模块来产生分发信息,访问不同的模块,例如私有外设、系统存储等。BIU微架构如图4所示。

图4 SoC总线微架构图

四、RISC-VE203CPU的设计验证

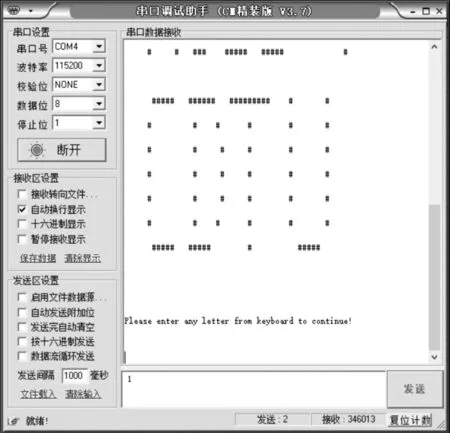

图5 串口打印“CDTU”字符串

图6 流水灯程序控制

本课题最终设计的蜂鸟E203 CPU在Xilinx XC7A100T芯 片FPGA开发平台上完成了验证工作,验证的结果分别如图5和图6所示。图5是将E203内核配置在FPGA上,利用编译器完成串口的调试,打印出成都工业学院简称“CDTU”;图6是在E203片上系统中烧写流水灯程序,每个0.5秒循环点亮一个LED;上述实验结果验证了设计的正确性。

五、结论

本论文设计实现了RISC-V32位流水线架构E203 CPU,限于文章篇幅还是尽可能完整地展现了该CPU的整体结构和模块功能,着重分析了顶层架构、IFU微架构、EXU微架构以及BIU微架构,编写了可运行于RISCV架构CPU的应用程序,并最终在Xilinx Artix-7FPGA开发板上验证了设计的正确性。