数字预失真器OP6180在宏基站中的应用*

谭大伦,张 海

(杰创智能科技股份有限公司,广东 广州 510663)

0 引 言

随着无线通信技术的飞速发展,3G/4G系统传输的信号具有宽频带、高峰均比的特点。这对射频功率放大器(Power Amplifier,PA)计提出了更高的要求。由于射频功率放大器固有的非线性和记忆效应[1],信号经过放大后,不仅会产生严重的带内失真和带外频谱扩展,还会增大通信系统误码率,干扰邻近信道。作为宽带无线移动通信系统[2]中不可缺少的关键器件,线性化技术的实现既能保证功率放大器的高效率,又能满足宽带无线通信系统对其线性度的高要求。数字预失真作为最有效的射频功率放大器线性化技术之一,凭借对消效果明显、性能稳定、处理信号频带宽、生产成本较低等优势,广泛应用于无线通信系统基站中。

1 DPD系统硬件设计

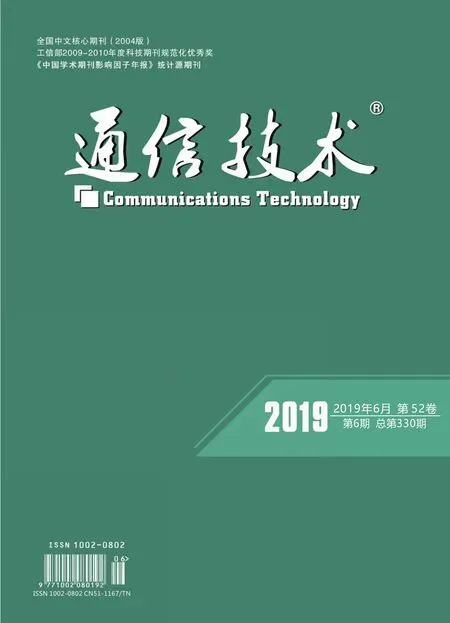

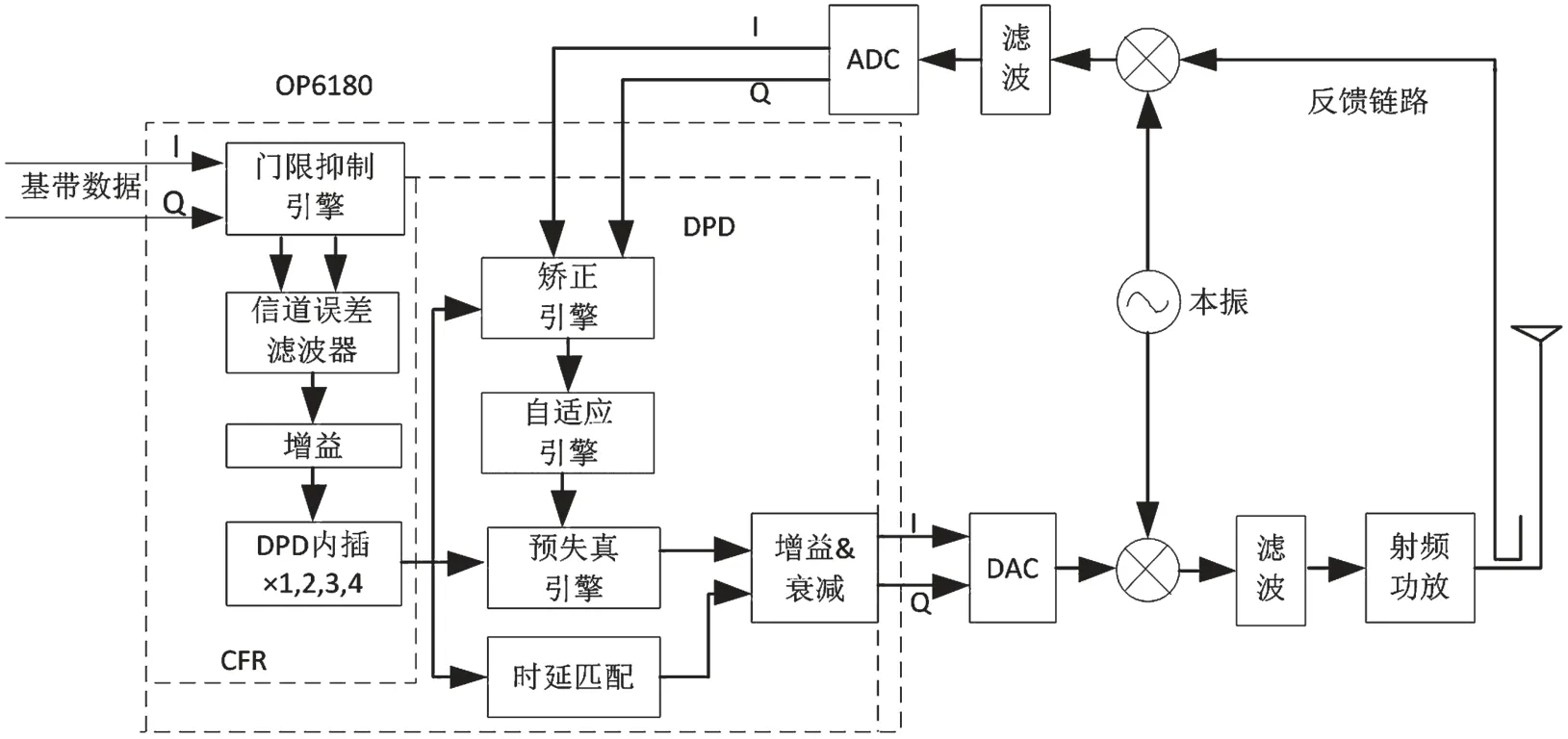

整个数字预失真(Digital Pre-Distortion,DPD)信道单元采用模块化的设计思想,硬件框图如图1所示,主要包括Doherty功放板[3]、DPD发射板(射频部分和数字部分)、基带处理板三个部分组成,

整个信道单元的关键就是DPD系统。DPD发射板采用博通公司OP6180芯片作为整个系统的核心芯片,射频部分主要完成混频、放大、滤波、反馈衰减等功能,数字部分主要完成模数转换器(Analogto-Digital Converter,ADC)、数模转换器(Digitalto-Analog Converter,DAC)、时钟系统、基带控制处理、波峰因子消减(Crest Factor Reduction,CFR)、DPD等。本文围绕DPD芯片OP6180进行硬件设计和软件设计重点描述,首先进行芯片介绍、芯片推荐中频方案比较、对DPD的指标进行描述,其次讲解OP6180芯片的软件设计实现,最后对整个DPD发射指标进行比较。

图1 信道单元功能示意图

1.1 发射方案介绍

Optichron公司推出的OP6180系列是首款具有8路、6路和4路多载波的商用数字预矫正处理器,为CFR和DPD处理提供了一种单芯片解决方案,该器件无需算法,无需外部处理器或支持电路,可降低系统设计的难度和成本。OP6180系列可以同时支持2G、3G和4G通信,多标准基站可利用该器件以低本高效的方式完成升级。

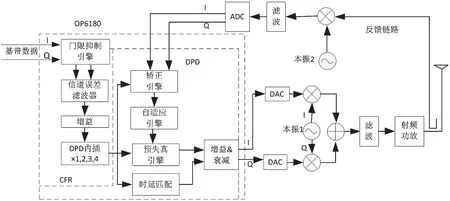

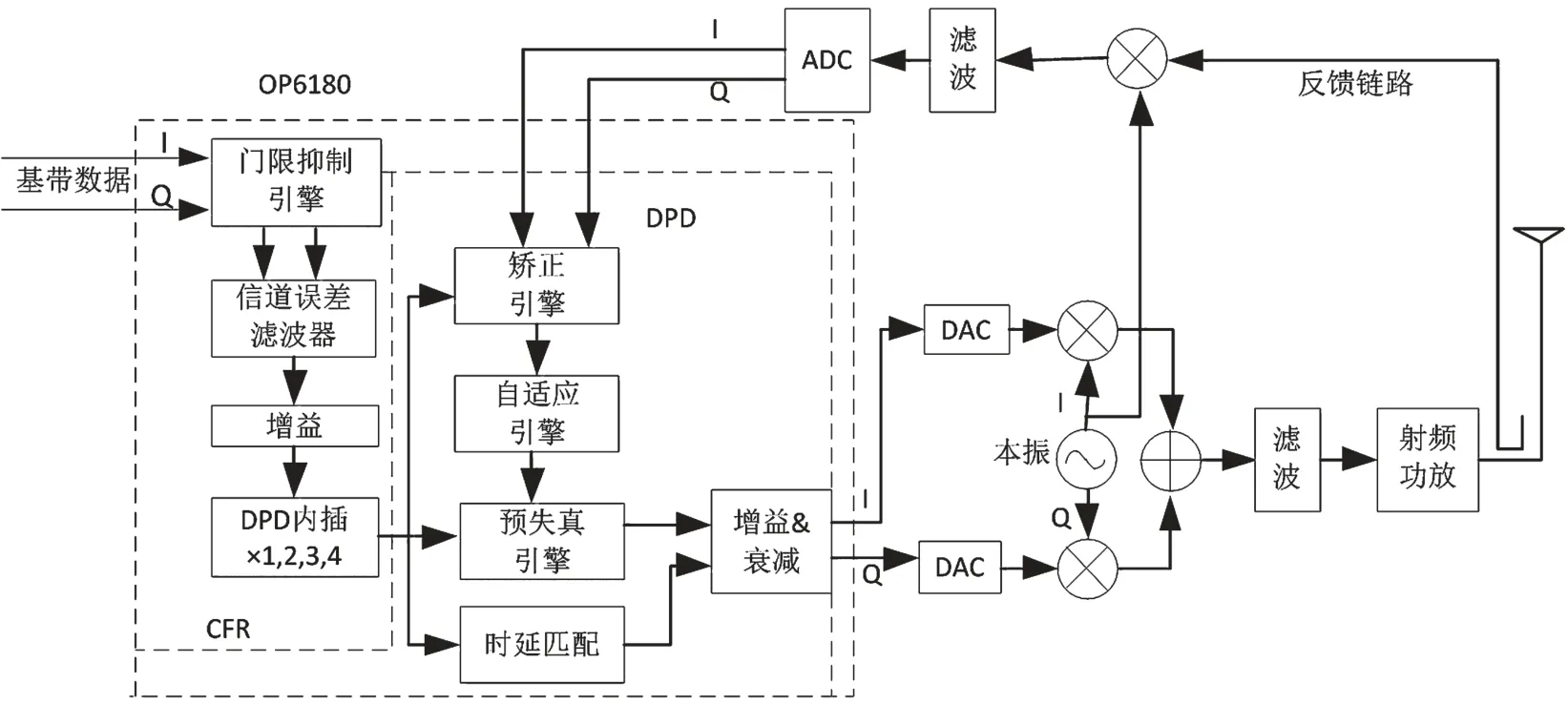

OP6180-1芯片具有20MHz的2G信号带宽以及35 MHz的3G/4G信号带宽,OP6180具有30 MHz的2G信号带宽以及50 MHz的3G/4G信号带宽。可处理700 MHz到3.7 GHz范围内的光谱频率,数据 速 率 125 MS/s、185 MS/s、208 MS/s、250 MS/s可选,数据接口支持LVCMOS和LVDS标准接口;预失真处理跟信号调制方式无关,可与多种功率放大器结构(包括AB和Doherty类)以及任何调制方案联合使用,OP6180在满足频谱屏蔽和EVM要求的同时,通过增加效率和最小退避实现更高的功率。支持零中频(Zero Intermediate Frequency,ZIF)、单边带(Single Side Band,SSB)和实中频(Real Intermediate Frequency,realIF)架构[4]。如图2~图4所示:

OP6180支持零中频输出,数字基带I/Q信号从DPD预失真引擎输出经过两路D/A转换变为模拟I/Q信号,模拟I/Q信号经模拟低通滤波器滤波后,分别与正交的两路射频载频信号混频后进行叠加,转变为模拟射频调制信号,经由功放PA的放大后,通过双工器发射出去,零中频省去了模拟中频级的处理。ZIF主要优点:降低带通滤波器(Band Pass Filter,BPF)设计要求,降低了ADC的采样率要求,由于解调制的输出频点为零,所以系统没有和中频有关的各种杂散信号,大大减少各种滤波器的需求。缺点:本振泄露和不必要镜像在带内并且不能被滤除,需要较高的算法来进行校准,因此要求I/Q非常均衡。但是零中频架构反馈链路不能与发射链路共用本振,需要两个本振信号,增加了电路复杂度。因为反馈链路采用实中频信号,中心频点一般设置为0.75Fs。

图2 零中频系统框图

图3 单边带系统框图

图4 实中频系统框图

单边带(SSB)架构与零中频架构相似,只是SSB架构反射通路和反馈通路可用同一个本振,而且其中频信号由DAC产生。SSB主要优点:在混频器输出端,本振泄露和不必要镜像会得到30 dB以上的抑制,可以降低后端带通滤波器(BPF)设计要求。SSB同样需要双路DAC,发射链路和反馈链路可以共用本振。

实数中频输出简称实中频,基带数据输入在,首先在OP6180进行增益和内插,在进行波峰因子消减(CFR)、数字预失真(DPD)后输出I/Q信号,I/Q信号就可通过数字低通滤波器(LPF)进行滤波后输出给DAC芯片,发射链路和反馈链路可以共用本振。实中频结构的优点为:本振泄露和镜像信号都可以通过简单的滤波器滤除,无需做任何校准,只需要一路反馈 ADC;缺点在于:对反馈通道的ADC采样率要求高,尤其是高带宽信号。但是实中频架构允许处理预失真信号带宽达到102.5 MHz,实信号频率可达150 MHz,一个本振减少了电路的复杂性,只需要调整同一个本振就可调整发射和反馈通路。

综上所述,3种架构各有优缺点,考虑到系统的实现、难度及复杂度,本方案采用实中频架构。

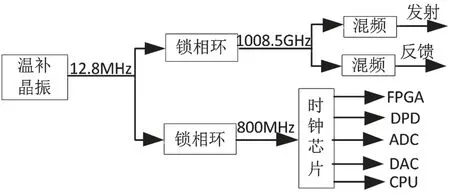

1.2 时钟系统设计

时钟系统再高速印制板中处于非常重要的角色,整个时钟系统需要考虑拓扑图、走线以及频率合理分配,主要用于为AD/DA、DPD、现场可编程门阵列(Field Programmable Gate Array,FPGA)芯片提供运行时钟,同时给发射数据、反馈数据和DPD接收数据提供差分跟随时钟,时钟频率为12.8 MHz,要求精度在1E-9以上。

由于系统时钟路数较多,同时ADC芯片对时钟抖动要求比较严格,选用HMC832锁相环芯片提供高速时钟频率,选用时钟芯片AD9516通过内部分频器分出各路时钟,DPD发射板时钟模块如图5所示。

图5 时钟系统框图

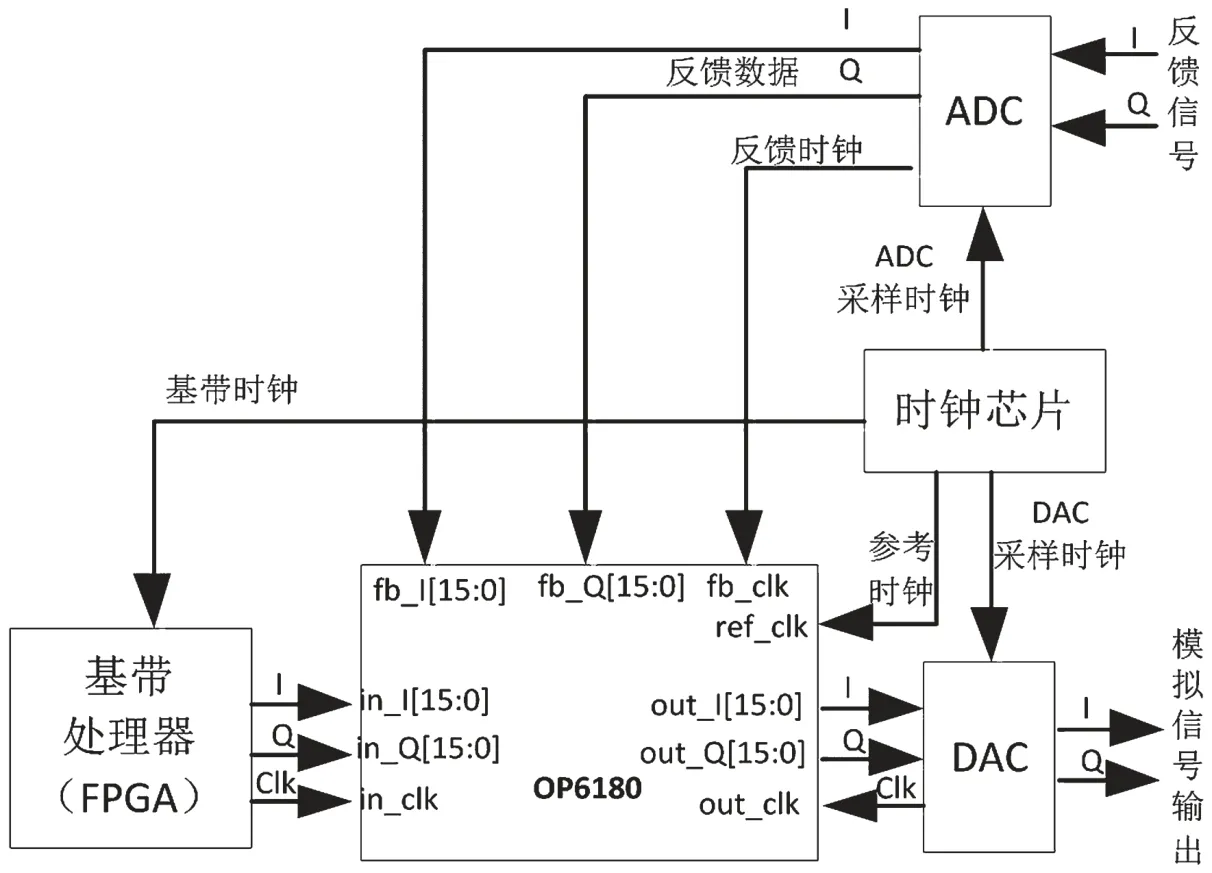

图6 是一个典型的OP6180时钟系统参考设计。ADC、DAC的采样时钟,OP6180的参考时钟,基带时钟由时钟芯片提供,基带数据随路时钟由基带处理器(FPGA)提供,反馈输入接口时钟由反馈ADC提供。输出接口随路时钟由OP6180内部产生,作为外部DAC数据同步时钟。

图6 OP6180时钟分布图

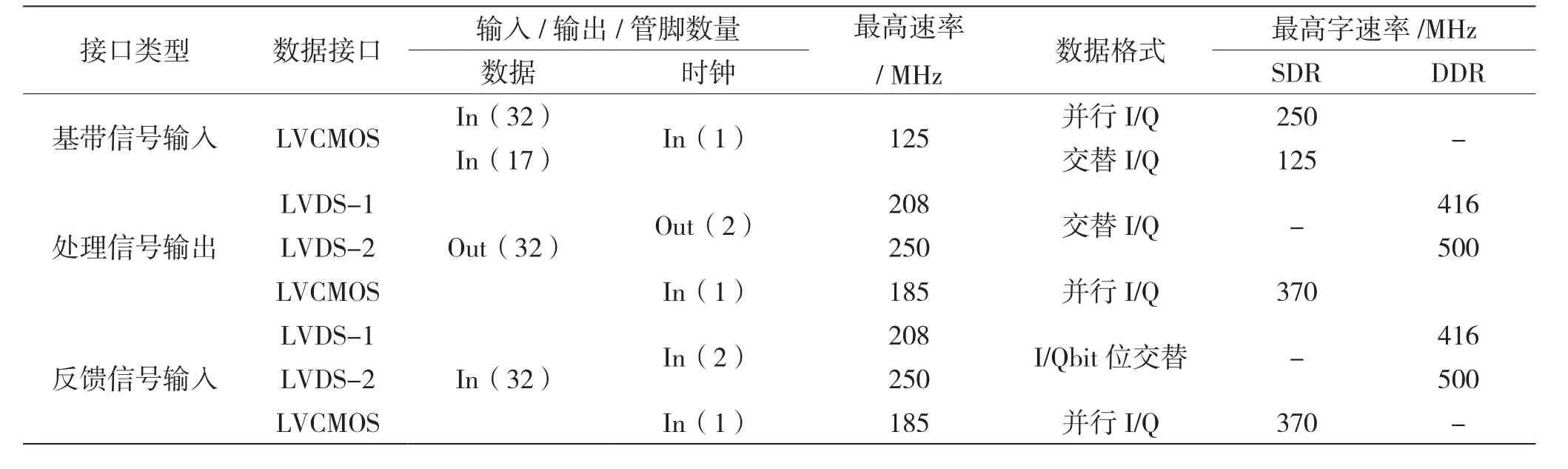

1.3 OP6180的数据接口

OP6180配备了三个信号输入/输出端口,每个端口的配置都很灵活,因此可以适应整个系统的数据速率和工作频率。一个端口用于基带信号数据输入,一个端口用于处理信号数据输出,另一个端口用于接收反馈数据输入。基带信号数据输入由I/Q 2路16bit LVCMOS标准接口,最大时钟速率为125MHz。处理信号数据输出由LVDS和LVCMOS两种标准接口,OP6180-2最高时钟可达250 MHz,反馈数据与处理信号数据输出的指标一样。数据接口采用高端对齐,假设输入数据位宽只有14 bit,则数据总线最低2位拉低。另外,输入接口的数据速率可以是系统核时钟的分数分频比,对应内插因子1x、1.5x、2x、2.5x、3x或者4x。整个OP6180系列的数据接口如表1所示,其中-1代表OP6180-1,-2代表OP6180-2。

设计中我们基带信号数据输入时钟是100 MHz,处理信号数据输出是200 MHz,反馈数据时钟是200 MHz。

表1 数据I/O接口

2 DPD训练流程

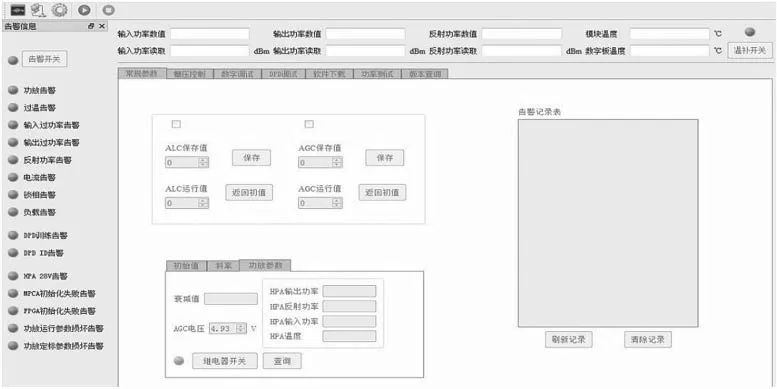

OP6180为了帮助用户节约开发时间,方便开发人员测试,因而提供丰富的接口函数及相关的状态寄存器。根据OP6180提供的内部控制器为参考,结合实际运用环境,我们自己开发了一个上位机调测软件,调测软件的主页面如图7所示,可通过串口或者网口把信道单元和调测上位机链接,总线发送相关命令对其状态进行查询及切换。

图7 DPD系统训练上位机

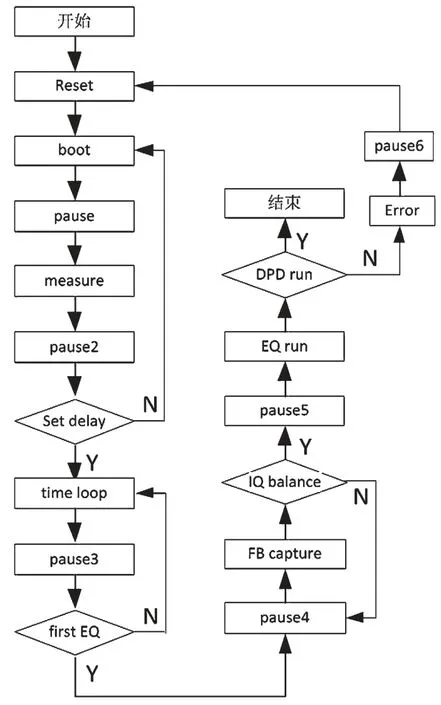

在正常工作模式下,我们先把整个DPD系统的功放参数设置好,就可进入DPD调试界面,提前训练好OP6180芯片,找到此功放模块与DPD芯片匹配参数,使得产品安装好后就DPD芯片就能运行在最契合的状态。通过发送复位信号,OP6180内部控制器从外挂SPIROM启动,加载相关的寄存器配置,完成初始化操作。状态机进入命令等待模式,整个DPD调试的状态控制流程如图8所示。

图8 状态控制流程

(1)Reset:复位,整个系统参数为0;

(2)boot:配置相关寄存器为初始状态;

(3)pause:暂停;

(4)measure:测量通路,OP6180输出数据,反馈链路把数据输入OP6180;

(5)set delay:建立整个链路的整数延时时间;

(6)time loop:测量整个链路的小数延时时间;

(7)first EQ:FPGA比较信号相关功率值;

(8)FB capture:捕获反馈信号的信息;

(9)IQ balance:校正I路、Q路信号的不平衡[5];

(10)EQ run:线性均衡器,校正幅度失真;

(11)DPD run:校正PA非线性失真;

3 结 语

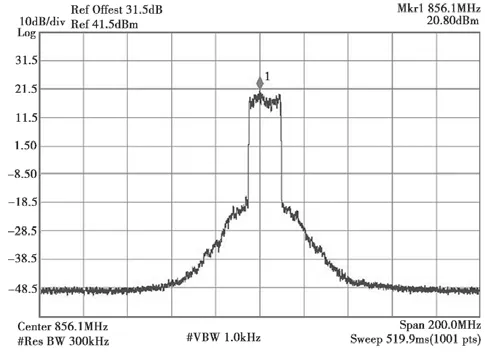

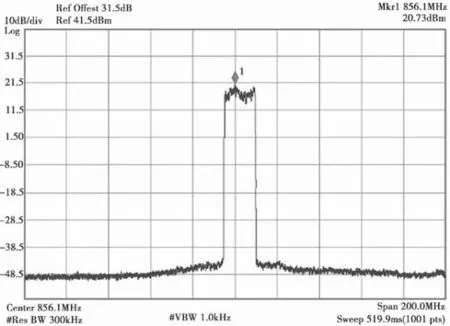

产品在基站中的测试数据如下,主要测试仪器:信号源选择Agilent EC4438,频谱仪为Agilent N9020A,外加射频电缆线、衰减器、电脑等。训练信号采用15 MHz的宽带信号,频点设置为856.1 MHz,输出总功率为20.8 dBm,RBW设置为300 kHz,VBW设置为1.0 kHz。

图9所示为对消前测试结果,图10所示为对消后测试结果。

图9 对消前的测试结果

图10 对消后的测试结果

可以看出,在PAPR为20 dBm,带宽15 MHz的条件下,对消前输出信号的ACLR为-18.5 dBc,数字预失真与PA级联对消后的输出信号ACLR为-45.5 dBc,OP6180有效的改善了PA的非线性失真,IMD3≤-65 dBc,改善效果≥25 dB。

通过对DPD方案的对比,充分研究了数字预失真DPD系统,对DPD芯片OP6180的内部结构及工作原理进行重点介绍,并给出了相关的软硬件设计、调测。从实测结果中可以看出,OP6180芯片对15 MHz宽带信号对消效果明显,实际使用过程中性能稳定,很好的解决了功放线性化问题,这种技术在3G/4G基站设计中有非常广阔的应用前景。对于功放的记忆效应引起的产品稳定性和适应性等方面还需要进一步完善。