基于边界扫描的可测试性硬件电路设计

陈建

【摘 要】本文对基于边界扫描的电路板硬件设计给出参考准则,通过介绍设计过程中的关键点达到提升可测试性的目的。

【关键词】边界扫描;硬件设计;可测试性

1、研究背景

随着边界扫描技术的成熟,国际上很多IC生产厂商制造的IC芯片都遵循该标准,如Xilinx、ARM、Altera、Intel等在其公司的产品中已大量的采用边界扫描标准。在板级测试中使用该标准需要一定的设计准则以提高可测试性。

2、可测试性设计

2.1器件选型

电子元器件选型时应考虑是否有同等功能的边界扫描器件可以替代,如果有应优先选用边界扫描器件。当前复杂的大规模集成电路通常都为边界扫描器件。

2.2 JTAG接口设计

a)电路板上所有的边界扫描器件都应该将TMS、TCK、TDI、TDO、TRST信号引出到JTAG插座上;

b)所选边界扫描器件的JTAG端口如果具有双功能引脚,应保留JTAG测试的功能性;

c)所选边界扫描器件的JTAG功能如果具有使能端,应该预留测试控制点;

d)对芯片JTAG的五个引脚禁止与电源或地直接相连;

e)对可编程器件的JTAG测试口以及其它多功能器件的JTAG测试口,在设计时,原则上只作测试用,不要复用为一般的I/O,不得已采用的特殊情况下应保留测试的功能。

2.3扫描链路设计

扫描链路配置是边界扫描测试的基础,电路板中所选用的边界扫描器件应按照串行方式或者独立多路径方式连接,且所有的边界扫描器件都应可控。

在连接扫描链路时,应注意电压兼容问题。对于不同工作电压系列的芯片,不能将芯片的JTAG信号直接相连,应进行电压转换以使电压兼容。

JTAG信号线在设计时应优先考虑稳定性和各自功能的实现。TCK和TMS信号作为公用信号,在进行测试时典型扇出不要多于8个,为保证电路的可靠性,一般在扇出大于4个时应该进行缓冲驱动处理。

2.4非边界扫描器件的可测试性设计

非边界扫描器件的测试的基本原则是尽量使非边界扫描器件被边界扫描单元完全包围,可以是直接包围也可以是间接包围,连接示意图如图1和图2所示。

3、测试系统实例硬件设计

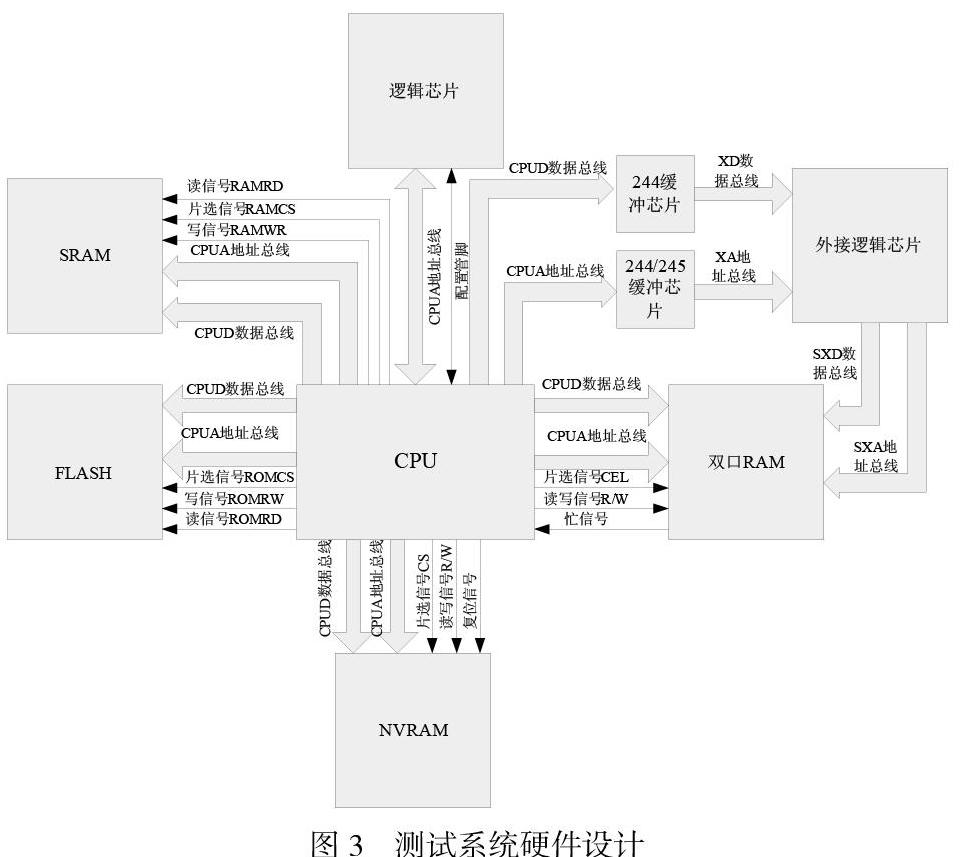

以下基于某型电路板构建了一套完整的边界扫描测试系统,系统的总体结构如图所示。

利用CPU芯片、板上逻辑芯片和1片外接的逻辑芯片完成整板的覆盖及测试。主要测试内容包括:

a)CPU芯片与板内逻辑器件之间收和发数据线以及相应配置管脚的互联测试;

b)CPU芯片与外接逻辑之间通过244/245等驱动的地址线、数据线、控制线的互联测试;

c)CPU芯片与SRAM之间的地址、数据和控制线的功能性测试;

d)CPU芯片与FLASH之间的地址、数据和控制线的功能性测试;

e)CPU芯片与NVRAM之间的地址、数据和控制线的功能性测试;

f)CPU芯片与双口RAM之间的地址、数据和控制线的功能性测试;

g)外接逻辑芯片与双口RAM之间的地址、数据和控制线的功能性测试。

在电路设计过程中对使用到的非边界扫描器件应尽量将信号线都接入边界扫描器件中,对于通过板上连接器上去往板外的信号,在底板母板上设计一块接插板,将连接器上的信号引进底板的逻辑器件上,从而可对该部分信号进行互联测試。

4、结论

本文基于边界扫描测试技术,介绍了硬件电路设计时需符合边界扫描测试的准则,包括了器件选型、JTAG接口设计、扫描链路设计以及关于非边界扫描器件的设计,并通过具体实例阐述了具体的设计方法,从而达到提升硬件电路板可测试性的目的。

(作者单位:中国航空工业集团公司洛阳电光设备研究所)