高效2 n 并行快速FIR 算法及其实现方法

胡剑浩,曾维棋,费 超,陈杰男

(电子科技大学通信抗干扰技术国家级重点实验室 成都 611731)

FIR 又称为非递归型滤波器,是数字信号处理系统中最基本的模块之一。FIR 滤波器在通信、雷达、图像、模式识别等领域都有着广泛的应用[1-3]。某些应用领域如光通信、5G 通信系统、高速遥感卫星接收机等,对滤波器的速率要求越来越高,而移动设备、手持终端等领域对设备的功耗有着严格的要求[3]。

文献[3]的研究表明,并行技术可以提高滤波器的信息吞吐率,同时降低设备功耗。然而传统的并行处理方式会使硬件复杂度随并行度线性增加,并行滤波器的硬件效率并没有得到改善,难以支持高并行度的应用。FFA 能打破传统并行方式的这种局限性[3-6],可仅用约2L−1 个N/L 抽头的子滤波器实现L 并行N 抽头的FIR 滤波器[3]。文献[7]提出了基于FFA 的2 和4 并行FIR 滤波器的理论形式与结构,文献[8]介绍了基于FFA 的8 并行FIR 滤波器,文献[9]改进了基于FFA 的3 并行FIR 滤波器,文献[10]给出了基于FFA 的16 并行FIR 滤波器的ASIC 实现方式。然而,目前的研究工作没有给出基于FFA 的2n并行FIR 滤波器的通用算法。

此外,在高速FIR 滤波器或滤波器组滤波等应用场合[11-12],对FIR 滤波器并行度的要求达到了160 并行甚至更高。目前基于FFA 的算法没有提出针对高并行滤波器的设计架构,很多工程实践仍然采用传统并行FIR 滤波器的实现方式,造成了很大的硬件资源浪费。

对此,本文根据已有的基于FFA 的2、4、8 并行FIR 滤波器的理论形式,提出了通用的2n并行FFA,并给出了其相应结构,进一步给出了160 并行FFA 的实现架构。通过硬件复杂度评估和算法分析,本文提出的算法和实现架构,可以满足高并行度FIR 的设计要求,并且算法复杂度和硬件效率较传统方法有显著改善。

1 基于FFA 的2、4 与8 并行FIR 滤波器

文献[8]已经推导出了基于FFA 的2、4 与8 并行FIR 滤波器的理论形式。本节主要对上述理论形式进行整理,方便后面进行推导和分析。

1.1 基于FFA 的2 并行FIR 滤波器

式中的滤波器输入为:

式中,X0和X1分别是输入序列{x(2k)}与{x(2k+1)}的z 变换,对于更高并行度情况亦类似。滤波器输出为:

同样,Y0和Y1分别是输出序列{y(2k)}与{y(2k+1)}的z 变换。预加矩阵为:

2.税收可以促进企业盈利。一方面,企业为了增加双赢,一方面是强大企业的生产能力,一方面为企业增加收入,另一方面,减少费用支出和税收,如果他能够完成税收策划和削减税收,这将有助于保证企业盈利。

但由于算例4增加了电动汽车的数量,意味着可移动的储能容量增加,电动汽车的可调功率也会增大,如图14所示。由图14可以看出,电动汽车的调制功率在-1 500~2 000 kW之间,比算例2的可调功率要大。

滤波器系数矩阵为:

H0和H1分别是滤波器系数序列{h(2k)}与{h(2k+1)}的z 变换。后级加法及延时矩阵为:

1.2 基于快速FIR 算法的4 并行FIR 滤波器

基于FFA 的4 并行FIR 滤波器的算法形式为:

我的画院:画院坐落在美丽的地方,有很多美丽的故事。如果想到其与宋代有着各种联系,立刻让人感到渺小,又让人振奋,力争创作出美丽的画,以不负各方。

式中的滤波器输入为:

输出为:

预加矩阵:

本文采用市售橡木桶对实验室制备的猕猴桃果酒进行了贮藏研究,随着贮藏时间的延长,电导率、色度和色调等指标呈现上升趋势,而溶解氧、游离二氧化硫、总酚和高级醇等物质均呈现下降趋势,经过橡木桶贮藏后的猕猴桃果酒其感官得分明显提高。在猕猴桃果酒贮藏过程中,物理、化学和感官的变化与样品初始溶解氧含量及橡木桶质量有关,后续将对不同贮藏装置及不同贮藏条件对猕猴桃果酒的影响做进一步研究。

后级加法及延时矩阵:

滤波系数矩阵:

1.3 基于FFA 的8 并行FIR 滤波器

基于FFA 的8 并行FIR 滤波器的算法形式为:

式中的滤波器输入为:

输出为:

预加矩阵:

在坚持党的领导这个重大原则问题上,很重要的是要引导人们正确认识和把握党的领导、依法治国、人民当家作主这三者之间的关系。在这个问题上,还存在一定的错误认识。有的把坚持党的领导同人民当家作主、依法治国对立起来,甚至用人民当家作主、依法治国来动摇和否定党的领导。这些在思想上是错误的、在政治上是十分危险的。

滤波系数矩阵:

后级加法及延时矩阵:

本文简单对钢混凝土叠合梁模板支架的施工技术进行了考察。经过实践证明,采用自承式悬挑支架体系来开展混凝土模板的搭建最为契合钢结构本身的特性,因此其结构安全性最好,施工效率较高且外部感观亦相对完整,是实现钢混凝土叠合梁模板支架施工的良好途径。

式中,

试验结果表明,经过浮选金精矿粗磨浸出—铅硫浮选分离—硫精矿再磨浸出工艺,可获得合格铅精矿,铅回收率73.00%,铅精矿中含金、银分别为97.40 g/t、467 g/t,作业回收率分别是8.03%、13.47%,可随铅精矿计价销售。该方案金、银总回收率为92.74%、86.92%,相较于方案一,金、银总回收率稍高,且铅精矿中金银的回收率大幅降低,可减少计价系数导致的产值降低。该方案在技术上也是可行的。

2 基于FFA 的2 n 并行FIR 滤波器算法

基于FFA 的2、4、8 并行FIR 滤波器的算法形式,推导出2n并行算法,并设计了基于FFA的2n并行与非2n并行的FIR 滤波器整体结构。

2.1 算法设计

2.2.1 基于FFA 的2n并行FIR 实现结构

由式(2)→式(9)→式(17)可归纳其输入:

根据2.1 节中的算法形式,对基于FFA 的2n并行FIR 滤波器架构进行设计。

对于预加矩阵,由式(4) →式(11)→式(19)推知:

对于滤波系数矩阵,由式(5)→式(12)→式(20)推知:

由式(6)→式(13)→式(21)推知:

对于后级加法及延时矩阵,由式(7)→式(14)→式(22)推知:

由式(7)→式(15)→式(23)可归纳得:

他用手上的刀丝挂住崖边的树木山石缓冲,因为下落的速度太快,第一次挂住东西的时候,拉断了一条手臂,然后刀丝太过锋利,斩断了树枝,第二次出手的时候,拉断了他另外一条手臂,最后能看到崖底了,只有一条腿还是完整的,可掉下去的时候还是摔断了……

式中,Ak满足:

所归纳的式(24)~式(32)即为基于FFA 的通用2n并行FIR 滤波器的算法形式。分析式(24)~式(32)可以看出,2n并行FIR 算法保持了原FIR 滤波器的传递函数,因此该算法具有与原FIR 滤波器的信号处理性能。

2.2 基于FFA 的2 n 并行FIR 滤波结构设计

由式(1)→式(8)→式(16),可归纳得到2n并行的理论形式为:

由式(3)→式(10)→式(18),归纳得输出为:

基于FFA 的2 并行FIR 滤波器的算法形式:

2.2.2 基于FFA 的非2n并行FIR 实现结构

对于非2n并行的FFA,可以用较低并行度的基于FFA 的并行FIR 滤波器组设计高并行度滤波器,本文设计并实现了基于FFA 的160 并行FIR滤波器。由于1 60 =20×8,因此可以用20 个基于FFA的8 并行FIR 滤波器组构建基于FFA 的160 并行FIR 滤波器。其设计结构如图2 所示。

3 硬件复杂度及算法性能分析

3.1 硬件复杂度分析

设计一个L 并行N−1 阶的FIR 滤波器,若多相滤波方式,需要NL 个乘法器及 (N−1)L 个加法器。

2012年12月,习近平总书记在广东考察时指出:“要尊重人民首创精神,尊重实践、尊重创造、鼓励大胆探索、勇于开拓,聚合各项相关改革协调推进的正能量。”这里,他所谈的正能量,与毛泽东同志所说的“调动一切积极因素,团结一切可以团结的力量”的基本精神是一致的。

若基于FFA 实现,当L=2 时,需要3N/2 个乘法器实现;当L=4 时,需要9N/4 个乘法器;当L=8 时,需要27N/8 个乘法器;L=16 时,需要81N/16个乘法器。那么,可以归纳出基于FFA 的2n并行N−1 阶FIR 滤波器所需乘法器的个数为3nN/2n,所需加法器数量需要具体计算。

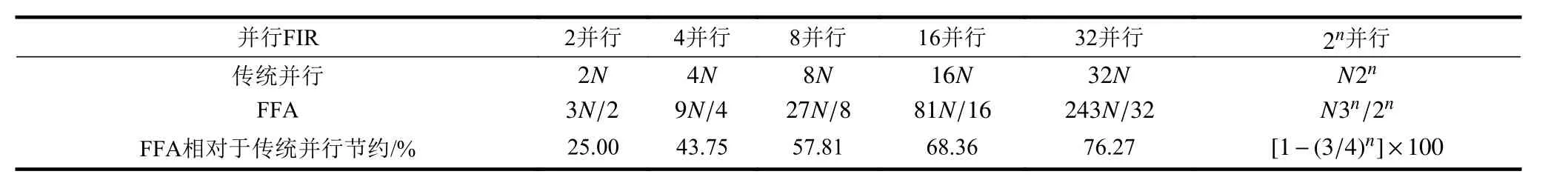

由此,可以统计出N−1 阶不同并行度下,传统方式与基于FFA 方式并行FIR 滤波器的乘法器数量的对比情况,如表1 所示。

由表1 可知,基于FFA 的并行FIR 滤波器所需乘法器个数少于传统方式。且随着并行度的增加,FFA 相对于传统方式将节省更多的乘法器资源。

表1 设计N−1 阶FIR 在不同方案下乘法器数目统计表

3.2 算法性能分析

在硬件实现过程中,在计算单元层面,假设传统并行FIR 结构中加法器的整数位宽为m bit,小数位宽为n bit。由于FFA 架构在前级有预加运算,如16 并行FFA 在前级最多会有16 个数的预加,若仍然采用m bit 的整数位宽,会存在运算溢出的情况。此时,需要拓宽预加16 个数的加法器的整数位宽至m+4 bit。这样,会使FFA加法器及乘法器的复杂度高于传统FIR 滤波器。并且相同并行度下FFA 的加法器个数也多于传统方式。由于FFA 相比传统方式能节约大量的乘法器,所以高效2n并行FFA 还是有显著增益。

(1) 随着支管关闭数量增加,流量改变量越大,造成的水锤升压越严重,因此,设计人员在设计时,应尽量的延缓末端阀门的关闭时间,并且要求尽量避免多条支管同时关闭。

我的画院:画院是我的绘画道路得以前行的一个保障,它为我提供了展示的机会,专研的动力,交流的平台。杭州画院是一个团结的集体,每位成员都有自己的追求目标,用“美美与共,和而不同”来形容最合适不过。

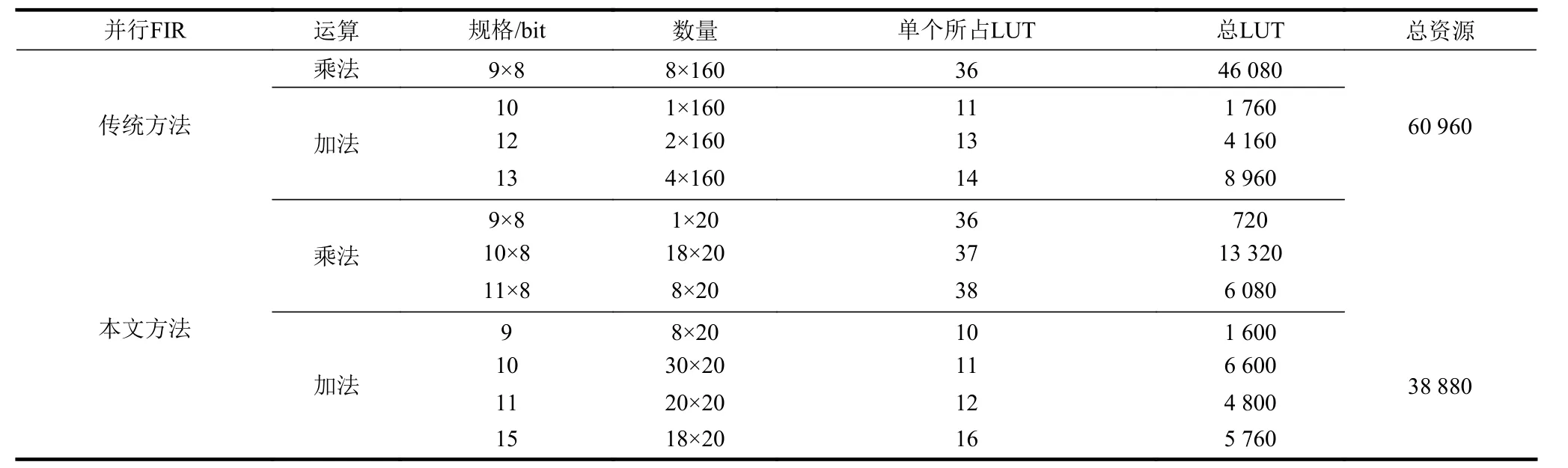

为了评估硬件资源总体的收益情况,针对高速光纤通信系统需要的7 阶160 并行FIR 滤波器进行设计实现。其架构如图2 所示。根据前文所述算法性能的分析,在计算单元层面,传统方式与本文提出的方式的加法器和乘法器的复杂度不尽相同。为了对比分析,采用本文提出的设计方法和传统的设计方法对该滤波器在FGPA 上进行资源评估。资源评估按FPGA 上对应IPCORE 所占用的查找表LUTs等效折算,所使用FPGA 为Xilinx XC7K325T,乘法器IPCORE 使用Multiplier 11.2 中的常系数乘法器。最终,基于FFA 的方法比传统方法的乘法器资源 缩减了56.3%,总资源缩减了36.2%,如表2 所示。

当前,实践中的课程整合可分为两大类:学科本位的课程整合与儿童本位的课程整合。学科本位的课程整合又可以分为两类:一类是超越不同的知识体系,以关注共同要素的方式安排学习的课程开发活动。这里的共同要素指的是相似目标、类似内容和大致实施方式。还有一种是学校常常容易忽略的,即以儿童现实的直接经验、需要和动机为出发点的课程整合。这种整合实际上是对现有课程的拓展和创新,是将游离在原课程体系之外的儿童经验和需求融入新的课程,故可称之为“儿童本位的课程整合”。

表2 7 阶160 并行FIR 滤波器FPGA 资源评估

4 结 束 语

本文根据已有的基于FFA 的2、4、8 并行FIR 滤波器的理论形式,推导了2n并行FFA,然后设计了2n并行FFA 及非2n并行FFA 的架构。接着,对比了在不同并行度下,高效2n并行FFA与传统并行算法实现的乘法器数目,发现随着并行度的增加前者的优势越发明显。最后,从计算性能以及计算单元层次上分析了该算法,得出结论:虽然高效2n并行FFA 相对于传统并行算法会增加若干加法器与乘法器的复杂度,但是由于前者对乘法器资源增益明显,所以其硬件效率较传统并行算法仍有显著改善,且随着并行度增加,这种优势会更加明显。