一种基于PCI接口的1394B总线的设计与实现

周勇 索晓杰 白晨

摘 要:1394B是一种高带宽、低延迟、高可靠特性高速串行总线,已经广泛应用于工业控制、汽车和航空航天等领域。文章设计了一种基于OHCI协议的1394B总线,主机通过PCI接口与1394B控制器之间通过DMA操作,实现数据的高速传输。

关键词:1394B;开放式主机控制器接口;外围组件互连

1 1394OHCI

IEEE1394俗称火线接口,主要用于视频的采集,最初由Apple公司提出,由IEEE正式制定,支持100 Mbps,200 Mbps,400 Mbps通信速率,其目的是简化计算机的外部连线,并且为实时数据传输提供一个高速接口。1394B是对IEEE1394增强或者扩展,主要是对总线效率进行改进,输速率将分别达到800 Mbps,1 600 Mbps和3 200 Mbps,支持即插即用热插拔功能[1]。

1394开放式主机控制器接口(1394Open Host Controller Interface,1394OHCI)是1394串行总线链路层协议的一种实现,附带一些支持事物层和总线管理层的特性[2]。1394OHCI包含了用于高性能数据传输的直接内存存取(Direct Memory Access,DMA)引擎和一个主机接口。1394OHCI主机接口既可作为主设备,又可作为从设备。

2 硬件设计

处理器选用TI公司的SM32C6415高性能定点数字信号处理(Digital Signal Processing,DSP),该芯片集成外围组件互连(Peripheral Component Interconnect,PCI)接口,最高工作频率为600 MHz。DSP的EMIF接口挂接FLASH和SRAM,其中FLASH用于存储DSP的固化程序;SRAM用于DSP片内SRAM的补充,可用于程序的运行;当DSP作为PCI从设备时,外接SRAM可作为从设备的memory空间。1394B总线挂接在DSP的PCI接口,DSP通过PCI接口对遵循OHCI规范的1394B链路层设备进行访问,通过DMA操作发送和接收1394B数据。

本设计中PCI接口挂接4路1394B总线,传输速率400 Mb/s。PCI总线为33 MHz的32 bit数据传输。1394B接口包括复位电路、时钟电路、电源电路、链路层电路、物理层电路、变压器。1394B总线的硬件组成如图1所示。

2.1 CCDL芯片选择

1394B总线链路层协议芯片选用TI的TSB82AA2B,该芯片支持S100,S200,S400,S800等传输速率模式,本设计根据需求配置为S400模式使用,可以通过软件设置其相关的寄存器来选择1394B信号传输速率。该芯片带有独立的PCI控制器,内部带有多个DMA发送通道和接收通道。可按照PCI规范连接在主处理器的PCI接口上,通过PCI总线进行对链路层的控制[3]。

1394B物理层芯片选用TSB41BA3D,是一款兼容IEEE1394a-2000和IEEE1394B-2002的、具有3个端口的物理层芯片,支持100/200/400 Mbps传输速率,实现1394的物理层功能。通过使用上下拉电阻对上电配置管脚进行配置,本设计物理层芯片配置成1394B的S400模式。

物理层与线缆间选用1394B总线三端口变压器TM1062TX3DUA进行耦合和隔离,可有效保护物理层芯片。

2.2 1394B链路层收发数据流

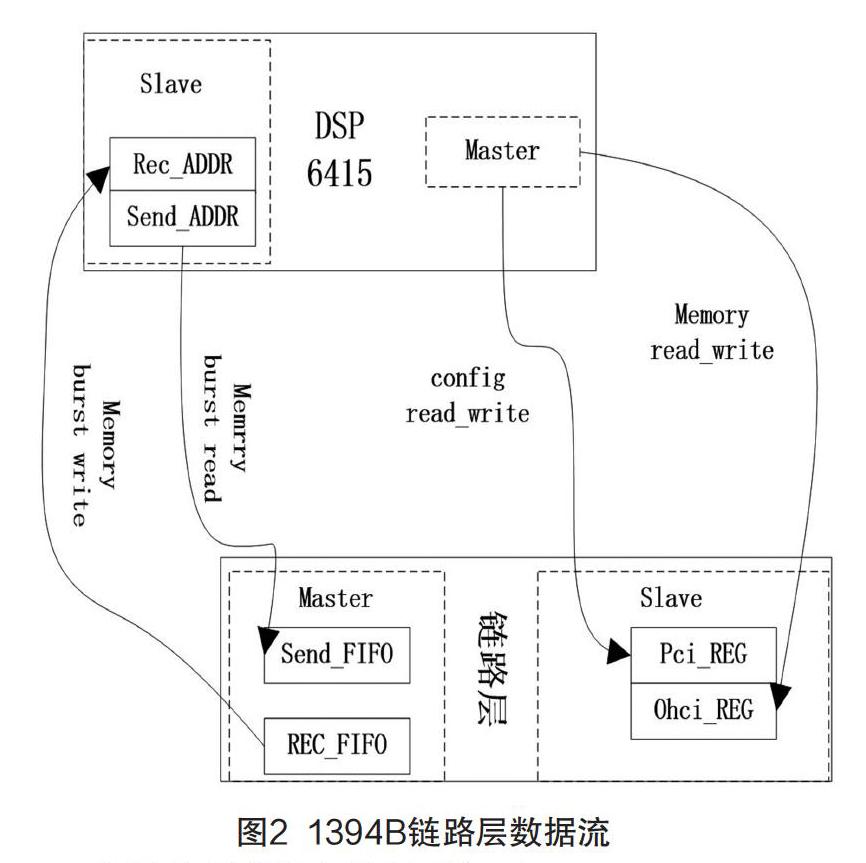

本设计中DSP SM32C6415处理器集成PCI接口,处理器和4个PCI接口的链路层芯片共同挂接在PCI总线上。DSP通过IDSEL对不同的设备进行配置访问。PCI总线上的5个设备都需要作为PCI的Master和Slave。1394B链路层数据流如图2所示。

DSP和链路层芯片主从关系如下:

首先,DSP作为主设备,在配置周期对4个基于PCI接口的链路层进行配置,配置从设备的访问空间,同时配置自己作为从设备的访问空间。

其次,在存储器读写周期,通过访问链路层的OHCI寄存器控制链路层的操作。DSP作为从设备时需要为每个作为主设备的链路层芯片分配内部访问空間,包括发送数据地址和接收数据地址,地址位于DSP的片内SRAM或片外SRAM.DSP把发送的余度信息放置到DSP的发送地址。

再次,作为Master操作链路层的OHCI寄存器来使链路层作为Master发起burst读操作,而后链路层作为Master通过Burst操作把DSP上的发送地址数据传送到链路层的发送FIFO中,通过物理层芯片发送出去。

最后,DSP作为Master通过存储器读写操作访问链路层芯片OHCI寄存器使能芯片接收,链路层接收FIFO中值超过阈值会自动作为Master发起burst写操作,把接收FIFO中的数据放置到DSP的接收数据地址中。

2.3 PCI仲裁

PCI总线是一种共享式总线,可以连接多个主设备,但由于数据传输的独占性,每一时刻只能由一个主设备占用总线。为了有效利用PCI总线带宽,必须设置一个总线仲裁器,按照一定的算法协调系统中各个主设备的操作。DSP 6415的集成的PCI接口没有仲裁器功能,且本设计PCI总线上的5个设备都需要作为主设备,因此,PCI仲裁器需要片外实现。本设计通过FPGA实现PCI仲裁功能。每个具备主设备功能的PCI设备的REQ#和GNT#均连接到FPGA的IO管脚上。其中,REQ#为请求总线信号,由发起PCI传输事务的设备发起。GNT#为总线授权信号,由PCI仲裁器裁决后给出。

目前应用于PCI总线仲裁的算法主要有固定优先级算法及动态优先级算法。在固定优先级算法中各个设备的优先级是确定的,仲裁器按照事先设定的优先级为每个设备分配使用权。该算法的缺点是一旦PCI总线事务繁忙或高优先级设备出错REQ#常低,优先级高的设备会占有总线不放权,导致低优先级设备一直无法申请到总线而饿死,不符合本设计中高容错性要求。本模块设计采用动态优先级算法。动态优先级算法是在每次仲裁授权后的设备优先级加1,下次仲裁时优先选择优先级数低的设备。保证所有的设备都有均等机会占有总线,放置一个总线故障,整个CCDL总线均不能正常运行,导致故障蔓延。

3 結语

本文从硬件设计、器件选型、收发数据流、PCI接口仲裁等方面详细介绍了一种基于PCI接口的1394B总线的设计与实现,本设计支持S100,S200,S400等多种传输速率模式,具有高带宽高、低成本、高可靠性等特点。

[参考文献]

[1]SOCIETY OF AUTOMOTIVE ENGINEERS.IEEE 1394B interface requirements for military and aerospace vehicle applications [EB/OL].(2020-03-13)[2020-04-10].http://std79.infoeach.com/view-Nzl8NTc0NjA3.html.

[2]PROMOTERS OF THE 1394 OPEN HCI.1394 Open host controller interface specification[EB/OL].(2000-01-06)[2020-04-10].1394Open Host Controller Interface Specification

[3]TEXAS INSTRUMENTS.TSB82AA2B 1394B OHCI-Lynx controller data manual,10/2011[EB/OL].(2011-10-20)[2020-04-10].http://www.ti.com.cn/product/cn/TSB82AA2B

Design and implementation of 1394B bus based on PCI interface

Zhou Yong, Suo Xiaojie, Bai Chen

(Xian Aeronautics Computing Technique Research Institute, AVIC, Xian 710065, China)

Abstract:1394B is a high-speed serial bus with high bandwidth, low latency and high reliability. It has been widely used in industrial control, car, aeronautics, astronautics and other fields. In this paper, a 1394B bus based on OHCI protocol is designed, which realizes the high-speed transmission of data through DMA operation between the PCI interface of the host computer and the 1394B controller.

Key words:1394B; open host controller interface; peripheral component interconnect