基于IP核的数字下变频设计与实现

王福红?王晓亮

摘 要 数字下变频是当前软件无线电的核心技术之一。本文在Xilinx公司提供的IP核的基础上,给出了一种数字下变频的设计方法,并对该种设计进行了仿真、验证,最终得到了预期结果。

关键词 数字下变频;IP核;直接数字频率合成;FIR

引言

数字下变频(DDC:Digital Down Convert)是通过混频将中频信号数字下变频至零中频信号的一种技术。实现这种功能的数字下变频器是软件无线电的核心部分,下变频器一般工作在A/D之后,是软件无线电中信号处理的关键环节之一[1]。一般来说,数字下变频实现了两部分功能:一是将接收到的信号频率降至零中频,便于后续处理;二是降低经高速A/D之后的信号速率,减轻信号处理对硬件资源的高要求。所以说,经过数字下变频处理,中频信号被下变频至软件可以处理的“零”中频信号,数字下变频是实现数字信号处理的关键。

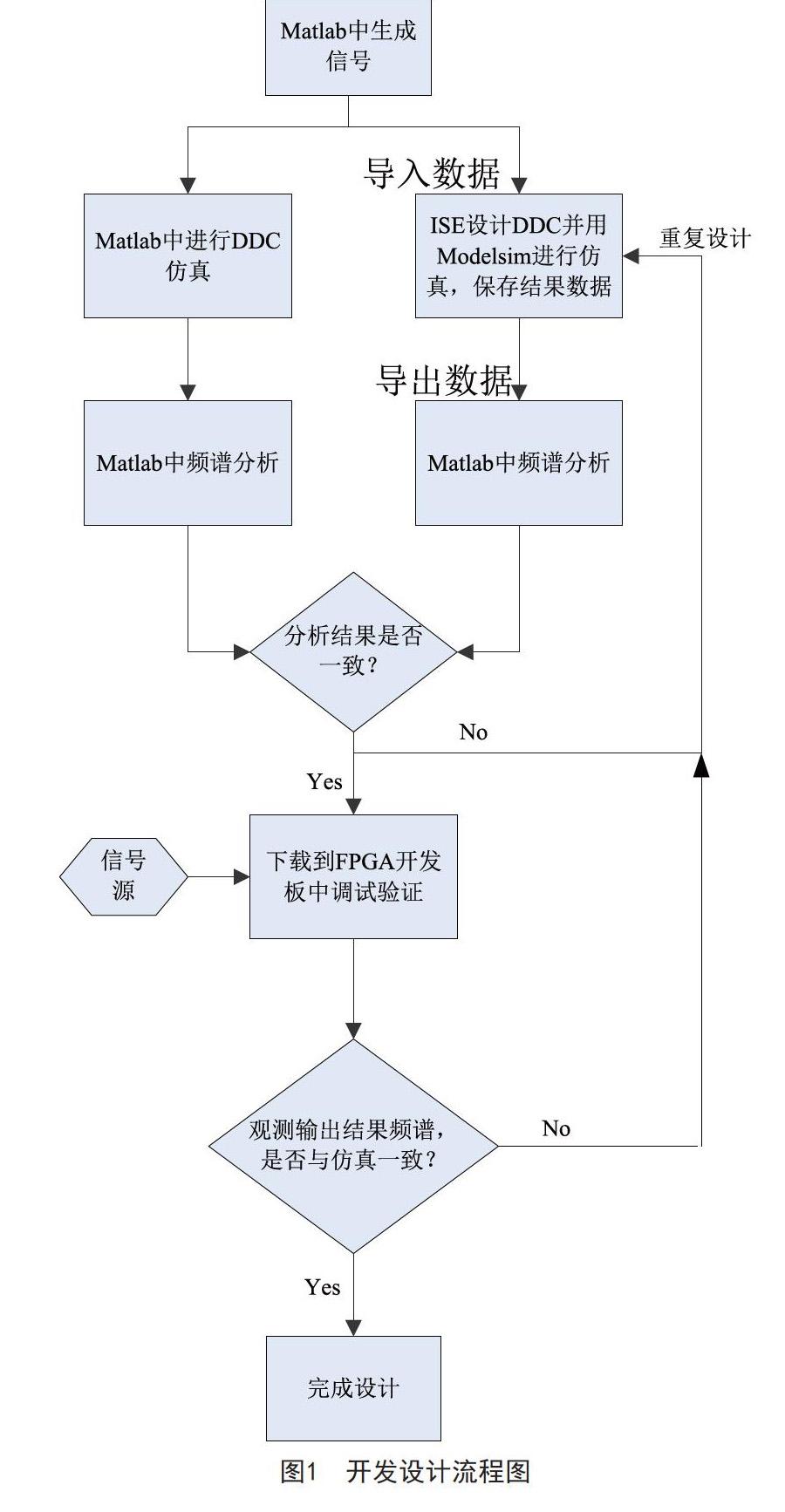

本设计包括两个部分:仿真和验证。仿真是在Matlab,Modelsim,ISE(Xilinx公司推出的FPGA开发工具)等软件的基础上验证设计的算法和理论功能的正确性。验证是通过JTAG下载电缆将设计下载到开发板的FPGA芯片中,然后通过开发板自带的软件观测FPGA输出信号以验证FPGA设计实际应用的正确性。

1DDC原理简介

1.1 数字下变频原理[2]

对AD采样信号进行混频,低通和抽取,可得到和信号带宽匹配的基带采样信号。该中频信号与两个数字正交信号进行混频,再经过低通滤波器滤除高频部分,就可以得到低频的I、Q两路信号。

1.2 DDS和低通滤波器FIR来实现下变频功能

(1)直接数字频率合成器(Direct Digital Synthesizer)原理简介

直接数字频率合成器(Direct Digital Synthesizer)是从相位概念出发直接合成所需波形的一种频率合成技术,众所周知,频率和相位的关系为:φ =2 *π* f * t,所以通过控制相位的变化速度,可以直接产生各种不同频率、不同波形的信号。一个直接数字频率合成器有相位累加器、加法器、波形存储器ROM、D/A转换器和低通滤波器(LPF)构成。

(2) 低通滤波器FIR

经过DDS之后的信号是零中频带通信号(只考虑正频率部分),此时信号的采样率仍然是ADC 采样频率(即中频信号的采样频率),数据率很高,信号的带宽远小于采样频率,设计一个低通滤波器就能从DDS输出信号中得到该信号,数字下变频中的低通数字滤波器通常采用积分梳状滤波器(CIC)、半带滤波器和FIR滤波器的多级结构。

2系统设计与实现

2.1 参数选取

(1)带通信号60±7M,作为A/D变换器的输入;

(2)A/D芯片采用LTC2262,采样率为100M,采样精度14bit;

(3)DDC系统工作时钟是100M;

(4)DDC输入数据速率为100M,输入数据位宽14bit;

(5)DDC输出数据位宽30bit。

2.2 系统的设计

IP(Intellectual Property)核生成工具是Xilinx设计工具中的一个重要设计输入工具,它提供了了大量成熟、高效的IP核为用户所用。由于IP核是根据Xilinx的FPGA器件特点和结构而设计的,直接用Xilinx FPGA底层硬件原语进行描述[3],可充分地将FPGA的性能发挥出来,其实现结果在资源和速度上都能达到令人满意的效果。

此次设计的DDC就是由Xilinx公司提供的DDC IP核实现。DDC中包含了DDS和低通滤波器FIR两部分[4]。经过A/D变换后信号(100M,14bit)作为DDC的输入,经过DDC之后变为I/Q两路信号数据位宽为30bit,速率为100M的零中频信号。经过DDC之后信号数据位宽输出理论应该保持不变,但是如果将输出数据位宽设置为14bit,DDC核会自动截取最大数据位宽中的高14bit作为输出(最大数据位宽由DDC模块自动计算,主要由DDS中混频器mixer输出数据位宽决定,同时考虑到资源占用情况,该设计mixer输出数据位宽为18bit,对应DDC输出的最大数据位宽为35bit),经实验验证,这样截取高位得到的14bit输出信号性能远远达不到要求(输出信号的幅度太小),所以该设计中采取的方式是:先将DDC输出的数据位宽加宽,再对其输出进行截取,考虑到实际的资源占用情况,将DDC的输出设置为30bit。在设计中,对两路(I/Q路)数据位宽为30bit的信号进行13bit~26bit截位效果最为理想,信号的质量也能得到保证。

经过DDS之后的信号是带宽为14MHz的零中频信号,只考虑正频率范围[0,7]MHz。在MATLAB中设计一个通带截止频率为7MHz的FIR,将系数量化为二进制数存入系数文件,将其导入FIR中即可。

整个开发设计流程如上图 1所示。

2.3 系统的仿真

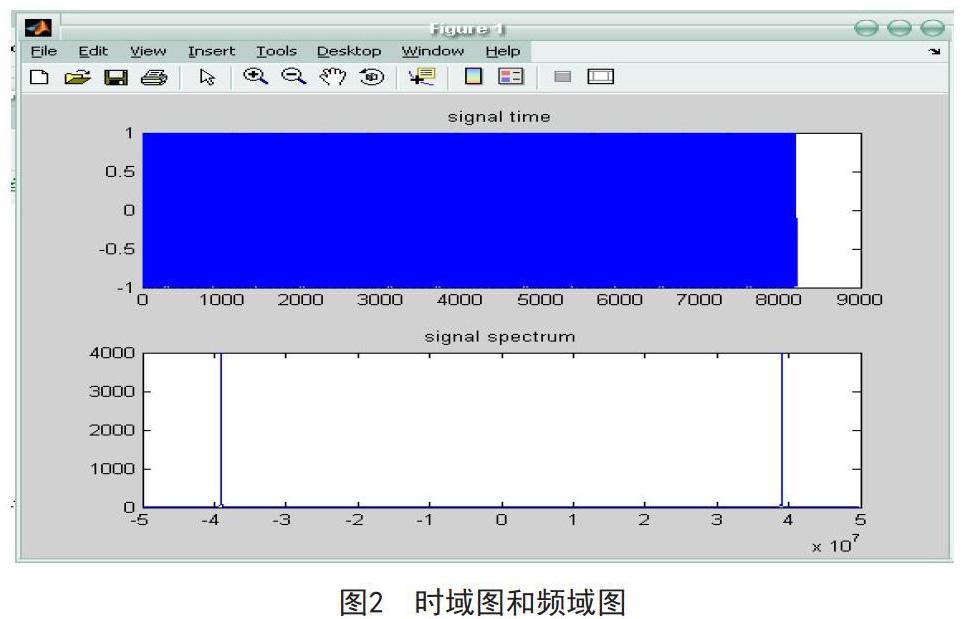

(1)输入信号的时域图与频域图如图 2所示。

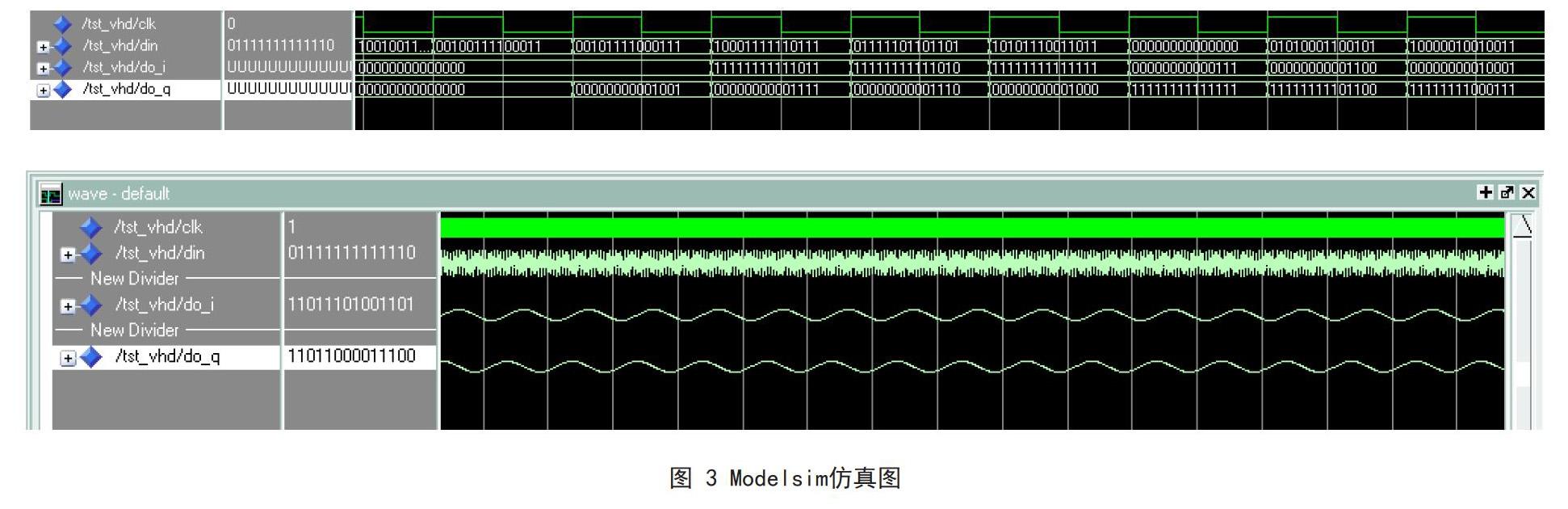

(2)经过Modelsim仿真以后得到的输出信号:

(3)对比信号

对比信号后可知本设计中DDC输出信号与理论分析相同,后经下载到FPGA开发板中输出结果与仿真结果一致,验证了本设计的正确性。

3结束语

本文以Xilinx的开发板为载体,对基于IP核的DDC(数字下变频)提出了一种设计方案,并通过实际项目的操作对该方案的可行性进行了验证。经过验证,该设计方法提高了资源利用率,实时性好,性能稳定。

参考文献

[1] 杨小牛,楼才义.软件无线电原理与应用[M].北京:电子工业出版社,2004:217.

[2] 吴芝路,贾长辉,任广辉.数字下变频的原理与实现方法[J].哈尔濱商业大学学报,2007,23(3):343-345.

[3] 谢白玉,数字下变频技术的研究及FPGA实现[D].重庆:重庆大学,2009.

[4] Heuberger A,Gamm E. Digital Downconverter[M].Software Defined Radio-Systeme für die Telemetrie. Springer Berlin Heidelberg,2017:109.