基于乘法器复用的信道化接收机的设计与应用

罗立宇 龚晓峰 雒瑞森

摘 要: 针对广播频段信道数量较多、信道带宽较窄的场景,给出一种基于乘法器复用的信道化接收机的高效FPGA实现方案,并详细说明了信道化处理模块。方案采用流水线结构,复用较少的乘法器,完成所有信道的信道化处理,解决了信道数量众多时乘法器使用过多的问题。不仅能够保证处理的实时性,还大大减少了信道化接收算法硬件实现中的关键资源。最后通过硬件仿真,验证了该信道化处理模块仅需要复用8个复数乘法器IP核即可完成128个信道的多相滤波。例化并使用2个信道化处理模块即可完成广播频段的信道化处理,并运行在102.4 MHz的系统时钟频率下。

关键词: 信道化接收机; 乘法器复用; 广播频段; 流水线结构; 多相滤波; 数据验证

中图分类号: TN914.3?34 文献标识码: A 文章编号: 1004?373X(2020)09?0010?04

Design and application of channelized receiver based on multiplier reuse

LUO Liyu, GONG Xiaofeng, LUO Ruisen

(College of Electrical Engineering, Sichuan University, Chengdu 610000, China)

Abstract: For the fact that the broadcasting band has more channels and narrow channel bandwidth, an efficient FPGA implementation scheme of channelized receiver based on multiplier reuse is proposed. The channelized processing module is elaborated. In the scheme, pipeline architecture is adopted and fewer multipliers are reused to complete the channelization of all channels, which solves the problem of requiring too many multipliers when there are a large number of channels. The scheme can not only guarantee real?time processing, but also greatly reduces application of the key resources during the hardware implementation when using the channelized receiving algorithm. It is verified by hardware simulation that the channelized processing module only needs to reuse 8 complex multiplier IP cores to complete polyphase filtering of 128 channels. The channelization of broadcasting band can be achieved by instantiating and using two channelized processing modules, and the channelized processing module can operate at the system clock frequency of 102.4 MHz.

Keywords: channelized receiver; multiplier reuse; broadcasting band; pipeline architecture; polyphase filtering; data verification

0 引 言

随着社会科技的进步,频谱资源也越来越紧张。传统的单通道和并行多通道接收机无法胜任同时对整个取样带宽内的信道进行分析、接收及解调。因此,信道化接收機的重要性就逐渐体现出来。这种接收机是一种能够完成全概率截获的接收机,能够通过信道化的方式同时对整个瞬时处理带宽内的信号进行检测、处理和接收解调[1]。在现代的电子战以及移动通信领域,信道化接收机都有着广泛的应用。在未来,对于频谱空穴[2]的检测,信道化接收机也是最佳之选。

近年来,关于信道化接收机的研究有很多。文献[3]提出了一种改进的信道化结构和相应的信道检测方法,文献[4]通过对信道的二次划分处理,降低了算法的复杂度。文献[5]在传统的多项滤波抽取算法基础上,对卷积公式进行多相推导,得到一种不降低数据采样率的多相滤波方法。文献[6]在推导任意个采样因子信道化模型的基础上,对各多相支路进行了优化,提高支路的吞吐率。文献[7]得到了基于IDFT数字信道化算法。研究算法的论文较多,但少有针对具体实现时信道数较多将占用大量乘法器问题的研究。

现主要针对广播频段信道数量较多、带宽较窄的场景,提出了一种基于乘法器复用的信道化接收算法的FPGA高效实现方案。

1 信道化接收算法的基本原理

信道化接收算法基于多相滤波[8]和快速傅里叶变换[9],该算法通过在低速率时钟下的并行实时处理,可高效实现多通道的并行处理,并大大缓解高速信号实时处理的速度瓶颈。若要求采样带宽内所有信号都能同时正确地被信道化处理,则各个信道的带宽必须是相同的,且等间隔排列,如图1所示(假设信道个数为128)。

假定整个带宽的取样信号为[S(n)],需要得到某个信道的信号[yk(n)],传统的方式为:先将该信号移频到基带,然后利用低通滤波器滤除其他通道的信号。式(1)可以表明该过程:

[yk(n)=S(n)ejωkn?h(n)] (1)

式中:[ωk]为搬移频率;[h(n)]为低通滤波器单位抽样响应。

以偶数倍抽取倍数、复数型输入信号为例,信道化处理推导如下:

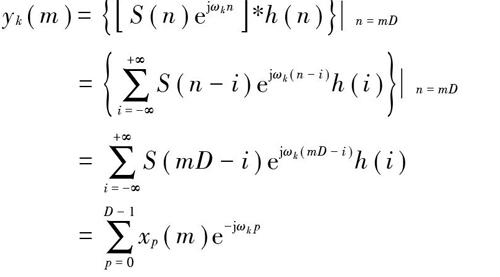

[yk(m)=S(n)ejωkn*h(n)n=mD=i=-∞+∞S(n-i)ejωk(n-i)h(i)n=mD=i=-∞+∞S(mD-i)ejωk(mD-i)h(i)=p=0D-1xp(m)e-jωkp] (2)

其中:

[xp(m)=i=-∞+∞S(mD-iD-p)h(iD+p)ejωk(mD-iD)] (3)

将[ωk=k-D-122πD]代入式(2),得:

[yk(m)=p=0D-1xp(m)(-1)pe-jπDpe-j2πDkp=p=0D-1x′p(m)e-j2πDkp=DFT[x′p(m)]] (4)

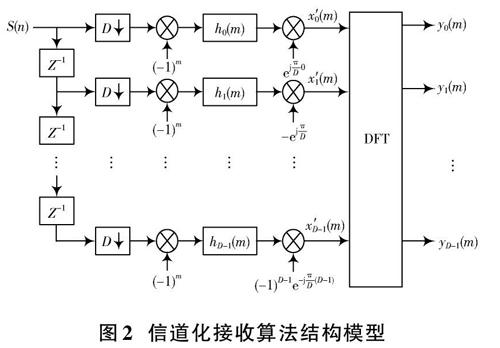

于是可以得到偶数信道的复信号信道化接收机结构模型,如图2所示。

2 FPGA硬件实现

2.1 应用场景

国内调频广播(除校园广播外)频段为87.5~108.0 MHz,且包含一位小数,信号带宽小于200 kHz。单一区域,如某市内,为了防止频道间互相干扰,频道的间隔一般大于0.1 MHz。

本文给出的信道化接收机模型能够针对87.7~107.8 MHz的所有广播信号进行接收与处理。

2.2 总体设计框图

将87.7~107.8 MHz的广播信号分为两类:第一类的小数位为奇数,第二类的小数位为偶数,分别简称为奇类和偶类。系统的时钟频率为102.4 MHz。

信道化接收机总体设计框图如图3所示。

ADC模块以97.7 MHz和97.8 MHz的中心频点,20.0 MHz的中频带宽进行实时采样,并将复信号串行输入到后端信道化处理模块,数据速率为25.6 MHz。中心频点97.7 MHz采样到的信号用来对偶类信号做信道化处理,97.8 MHz采样到的信号用来对奇类信号做处理。信道带宽200 kHz,可以得到奇类与偶类信号的信道化分布,如图4所示。

虽然两类信号信道之间存在混叠,但是一般情况下,广播信号的频点间隔大多大于0.1 MHz,即两个广播信号不会存在于相邻的两个奇偶频点之上。且奇类信号在偶类信道化处理模块中会进入两个相邻偶类信道,成为“误”信号,但进入的部分处于低通滤波器的过渡带,甚至是阻带,因而功率会降低,对于偶类信号也是如此,只需要在功率检测模块中设置合适的门限,就可以排除这样的信号。

2.3 信道化处理模块

该模块是信道化接收机中的关键模块之一。由信道化接收算法模型,硬件实现的关键在于信号的延时、抽取、系数的相乘及滤波。后端的DFT可以使用FFT的IP核实现。信道个数较多的情况下,复数乘法器将占据较多的资源。因而,要节约资源并尽可能保证信号处理的实时性,关键点在于将结构模型与硬件特点充分结合。为了保证信号处理的实时性,本文采用流水线的设计方法。设计框图如图5所示。

为方便说明设计方案,设有以下场景:系统时钟频率为102.4 MHz;复信号输入速率为25.6 MHz,位宽为32 bit(高16 bit为I信号,低16 bit为Q信号);信道个数为128,信道带宽为200 kHz;原型低通滤波器系数为4 096阶。

值得一提的是,由于后端FFT的IP核计算点数是固定的,为2的幂次倍。为了包含87.7~107.8 MHz所有200 kHz信道,并满足FFT的IP核设置,故将抽取倍数定为128,也即128个信道(两侧若干信道没有信号)。

2.4 乘法器复用子模块

此模块是本设计的主体部分,主要包括:8个双口RAM核及其地址控制块,8个ROM及其地址控制块,8个复数乘法器IP核。乘法器复用子模块的细节示意图如图6所示。

8个双口RAM的深度均为512,宽度为32 bit,每个单元存储一个IQ样点,A口作为输入,B口作为输出。它们的寫地址(A口)均为0~511的循环,控制好A口的写使能,使得写满双口RAM1后,再对双口RAM2进行写操作,……,写满双口RAM8后再对RAM1进行写操作,以此类推。系统时钟频率为102.4 MHz,输入信号的速率为25.6 MHz,每个新的数据样点有4个时钟周期用来写入,本文的设计在新数据到来的第一个时钟周期,A口写使能信号wren_a置1,以完成写入(其余时候置0),保证后续不会产生读写冲突。同时,写入一个新数据样点的4个时钟周期可以从一个双口RAM中读取4个旧的数据,8个双口RAM共可读出32个旧的数据。

写入地址是顺序的,但读取顺序是跳变的,且8个双口RAM使用相同的读地址,同时,读出相应地址的数据。读取规则为:当针对某RAM的某地址[n]作写入操作时,按照[n]+128,[n]+256,[n]+384,[n]的地址顺序读取8个RAM中的旧数据,若计算后地址大于511,则减去511。4个时钟内,第一个时钟已完成对[n]地址写入,第4个时钟才对[n]地址读取,故不会产生读写冲突。

按照上述方式并行读取的32个数据还需要按照时间顺序重新排列,以正确地完成滤波操作。排序的方式有举例说明,当针对第2个RAM中的128地址进行写操作时,读取并排序的方式如图7所示。图7中,8个双口RAM下方的数字代表顺序,其中,1表示时间上最旧,32表示时间上最新,重新排列后即可形成有序的时间序列。

重新排列的方式是固定的,可以将排列的方式枚举,于是只需要一个时钟周期,排序模块可以将8个并行输入数据重新排序后并行输出,部分仿真结果细节如图8所示。

根据多相滤波原理,4 096阶原型滤波器对于128信道来说,每一相有32个系数。根据复信号的信道化接收机结构模型,每个信道的信号需要先后与±1,[(-1)D-1e-jπD(D-1)]相乘,并由[hD-1(m)]完成滤波。可预先将每个信道的[hD-1(m)]与[(-1)D-1e-jπD(D-1)]相乘,合并成8组,每组512个32 bit位宽的复数系数(高16位为实部,低16位为虚部),存入8个512深度32 bit位宽的ROM中。如图9所示,每组系数存入其对应行的8个ROM的32个地址中。存入前,使用Matlab对系数预处理,每个时钟从第[n]个ROM中读取的系数能够与从第[n]个RAM中读取的样本数据对应上,接着由一复数乘法器IP核实现复数相乘。串行数据流与±1的操作可以置于FFT模块后。

复数乘法器IP核的输入位宽为16 bit,根据复数相乘原理,16 bit有符号数与16 bit有符号数相乘至多为32 bit,32 bit有符号数与32 bit有符号数相加至多为33 bit。另外,该复数乘法器后端需完成32个33 bit有符号数的累加,需预留5位以防止溢出,可得该复数乘法器的输出位宽需设置成38 bit。

考虑到FFT的IP核输入位宽有限制,还需要将累加模块的输出截位。截位模块的部分仿真结果细节如图10所示。

由于数据速率低于系统时钟频率,故需要一个FIFO对数据进行缓存,以便后端FFT能够一次性读完128个数据。

3 实测数据验证

本文对信道化处理模块进行基于Verilog HDL语言的编程,并对实际采集到的两段广播频段信号(分别以97.7 MHz,97.8 MHz为中心频点,20.0 MHz为中频带宽)进行基于ModelSim软件的仿真。

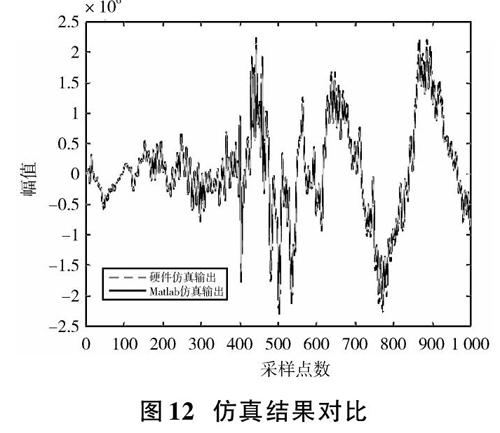

使用Matlab对奇、偶信道化处理模块得到的各128个信道做平均幅值图,如图11所示。

使用Matlab同样对20 MHz的宽带信号做信道化处理,得到某广播信号软硬件仿真结果的时域对比,如图12所示,并使用Matlab对未经信道化处理的数据作FFT,根据频谱图得到各广播信号所在频点,对比奇、偶类信道各信号中心频点,能够完全对应,并且没有信号遗漏。

从图12可以看出,硬件仿真结果与Matlab基本一致,收听效果相当,由此可见,本文设计基本达到预期,误差是定点运算的量化误差导致的。

4 结 论

本文对信道化算法结构模型进行研究,并结合實际工程应用,将信号的偶数倍抽取及延时与双口RAM结构相结合,提出了一种复用复数乘法器的信道化处理模型。该复用乘法器的模型需要系统时钟频率与数据速率存在整数倍的关系,以实现高时钟频率、低数据速率情景下的资源复用。

参考文献

[1] 楼才义,徐建良,杨小牛.软件无线电原理与应用[M].2版.北京:电子工业出版社,2014:95?96.

[2] 曾莉.认知无线电关键频谱感知技术及应用分析[J].通信与信息技术,2017(1):59?62.

[3] 吕卫祥,徐鹏,曹元将.一种改进的数字信道化结构设计及检测方法[J].现代防御技术,2018,46(3):73?79.

[4] 聂慧锋,翟羽佳.一种高效多级信道化数字接收机的设计与实现[J].雷达与对抗,2018,38(3):47?52.

[5] 孙健,韩文俊,凌元.基于多相滤波的高速滤波器FPGA设计[J].遥测遥控,2018,39(5):27?32.

[6] 周新星,谢祖刚,邱耀明,等.电子战宽带数字信道化的优化设计方法[J].航天电子对抗,2018(5):46?48.

[7] 眭超亚,唐毅谦,罗正华,等.基于IDFT结构的多通道信道化算法研究[J].成都大学学报(自然科学版),2018,37(4):387?390.

[8] 李婉婉.多相滤波技术研究及在多信道接收机中的应用[D].北京:北京邮电大学,2018:20?21.

[9] 周秀珍,肖雷.基于快速傅里叶变换的实时频谱分析方法研究[J].信息通信,2018(8):21?22.