基于FPGA的DDS跳频系统设计

郭明昊

摘 要:跳频通信具有良好的抗干扰、抗多径衰落、抗截获等能力和同步迅速等特点,广泛应用于军事、交通、商业等各个领域。跳频系统通过伪随机码对待传输信号进行频谱扩展。频率合成器是跳频系统的关键,直接影响到产生频率的准确度和跳频信号的稳定性,在跳频频率合成器中,直接数字式频率合成器(Direct Digital Synthesizer DDS)使用最为广泛。DDS具有简单可靠、控制方便、高分辨率和高转换速度的特点,非常适合跳频通信的要求。

关键词:FPGA;DDS;跳频

1、引言

最初的无线电通信采用单频通信方式,即载波为固定频率的信号源,只能在特定频率下进行通信。军事上常用的电子侦察手段、无线电干扰和反辐射攻击等方式可以很容易对信号进行干扰,严重影响通信质量。因此,目前迫切需要一种新的通信方式来对抗干扰或跟踪,跳频技术凭借其强大的抗干扰能力引起广泛重视,跳频通信在通信时使频率进行不间断的、随机的跳变,增强抗干扰、防跟踪能力,这也是现代军事无线通信抗干扰常用的方式之一。

2、直接数字式频率合成器设计

2.1、DDS概述

DDS是一种把一系列数字信号通过DAC转换成模拟信号的合成技术。利用硬件电路代替计算机软件运算过程,即利用高速存储器做查询表,这是目前使用最广泛的一种直接数字频率合成方法。

2.2、DDS基本原理

首先,为了统一表述,本文设系统频率(FPGA系统时钟速率)为fclk ,DDS期望输出频率为fd ,DDS实际输出频率为fout 。设DDS的相位累加器位宽为n,频率控制字为k,相位控制字为POFF,相位累加器输出值为P。由于相位累加器为2进制数,将其代表的归一化弧度制角度设为θ(p) ,单位为rad。设相位增量为△θ ,频率分辨率为△f 。它们所代表的含义,将会逐一在本节中介绍。

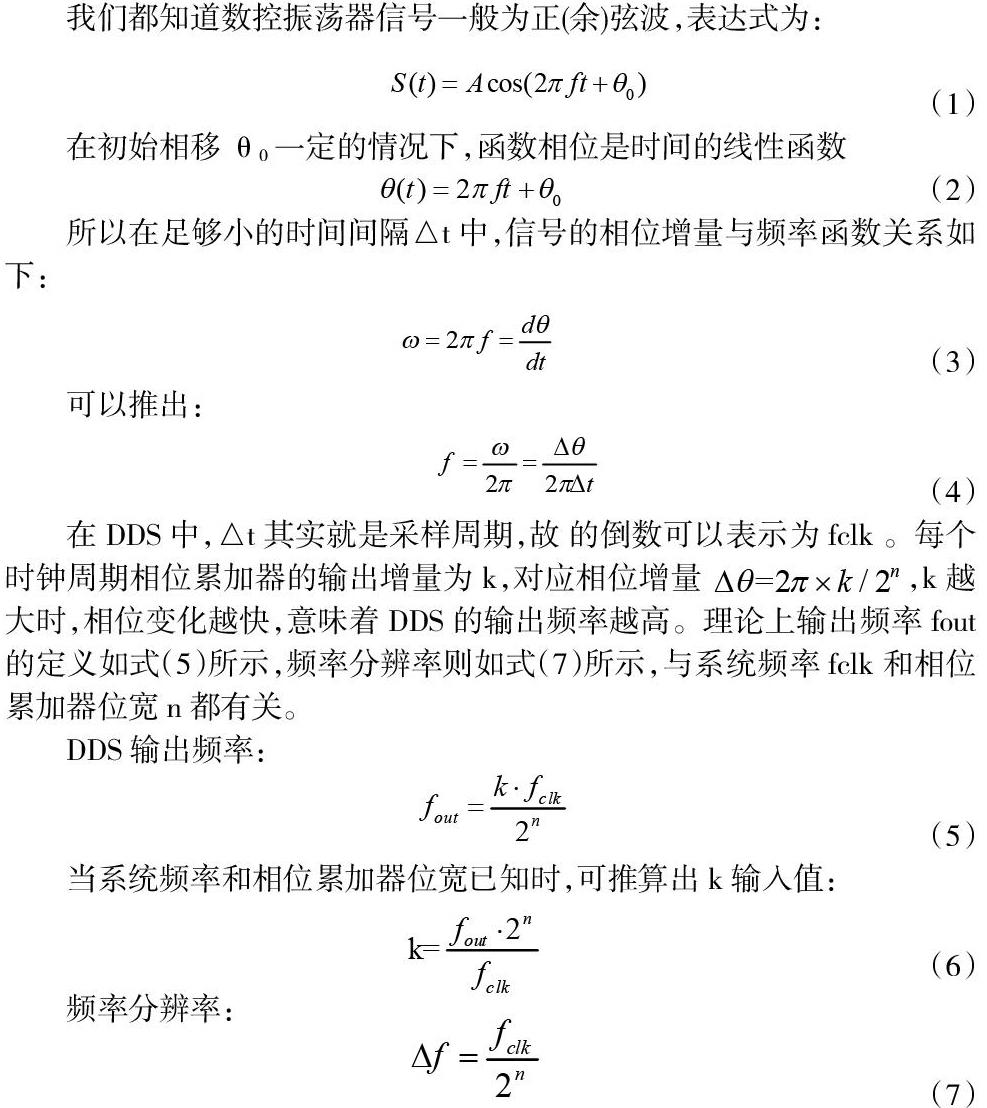

我们都知道数控振荡器信号一般为正(余)弦波,表达式为:

在初始相移θ0 一定的情况下,函数相位是时间的线性函数

所以在足够小的时间间隔△t 中,信号的相位增量与频率函数关系如下:

可以推出:

在DDS中,△t 其实就是采样周期,故 的倒数可以表示为fclk 。每个时钟周期相位累加器的输出增量为k,对应相位增量 ,k越大时,相位变化越快,意味着DDS的输出频率越高。理论上输出频率fout 的定义如式(5)所示,频率分辨率则如式(7)所示,与系统频率fclk 和相位累加器位宽n都有关。

DDS输出频率:

当系统频率和相位累加器位宽已知时,可推算出k输入值:

频率分辨率:

3、基于DDS的跳频系统设计

整个系统由两个部分组成,逻辑地址控制模块和 DDS 模块。逻辑地址控制单元用来产生不同的频率控制字,改变相位累加器的累加值。DDS 单元包括相位累加器和 ROM 查询表。

3.1逻辑控制模块

在本设计中,逻辑地址控制模块由一个6级移位寄存器和6位存储器构成。系统时钟clk 经过分频后得到时钟clk_out ,作为逻辑地址控制模块的驱动时钟。当时钟clk_out 上升沿到来时,r(1:5)=r(0:4) 。这样移位寄存器中的状态将改变,并存入存储器中,得到频率控制字k。

3.2基于LUT的DDS設计

一个典型的基于查找表(Look Up Table LUT)的DDS系统主要由相位累加器和查找表组成,相位累加器位宽为n bit,对应的LUT深度为2n ,相位步进值即频率控制字为k,累加器输出经过截位后作为地址传送给查找表,在FPGA中,查找表由Block RAM资源实现,存储一个周期的波形幅度值。

因此通过LUT实现DDS的方法是最为直接、快速的,因为不涉及乘法运算,所以DDS的系统频率可以达到很高,但如果想得到高频率分辨率,就需要更大的相位累加器位宽,这也意味着LUT存储的数据量更大。FPGA的Block RAM通常是有限的,有时甚至需要外接ROM来存储波形,这也给稳定性带了挑战。

为了解决上述问题,在保证输出信号具有良好频率分辨率的前提下,由于 DDS 产生的正弦波具有周期性,因此本设计的 ROM 中只存储 1/4 周期正弦波,利用正弦信号的对称性,通过改变 ROM 存储器地址以及对输出端进行控制,便可得到完整周期的正弦信号。

4、仿真结果及分析

本次仿真的目的是为了验证DDS信号发生器的性能,包括信号发生器能否生成波形,频率能否跳变,跳变后波形是否正常。

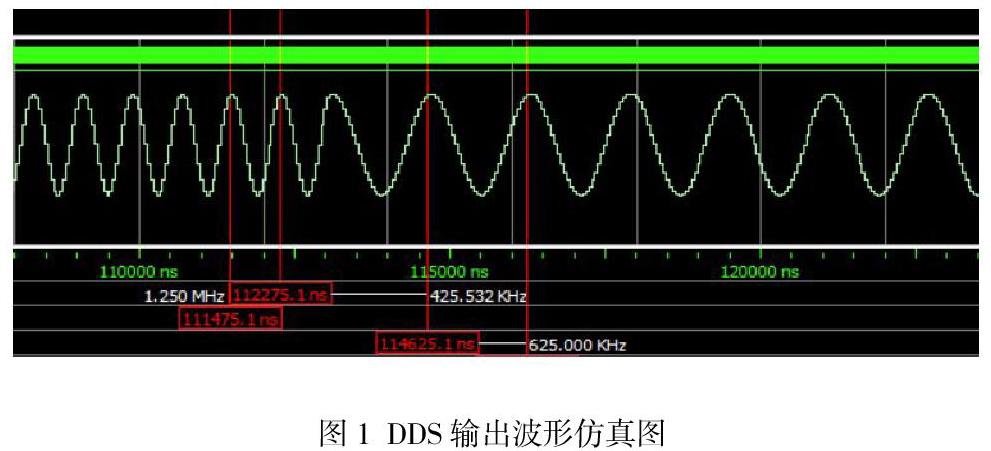

由图1可知,正弦波可以正常输出。为了测试输出波形频率的准确性,频率控制字k分别给定128和256,进行仿真测试。如图1即为频率控制字分别为128和256的正弦波的输出波形图。

由式(5)可以计算出:当频率控制字k=128时,fout =625KHz;

当频率控制字k=256时,fout =1250KHz;

由图1所示,通过仿真测得的频率分别为625KHz和1250KHz,与由公式计算得到的结果625KHz和1250KHz相吻合。由此可得:(1)更改频率控制字时,可以更改波形的频率。(2)输出波形光滑连续,仿真测试所得频率与理论计算值的误差较小。(3)正弦波两个不同频率间波形切换自然,转换速度较快。

5结语

本设计中基于FPGA的DDS 跳频系统输出信号稳定,而且输出信号频率转换速度快。除此之外,本系统可移植性高,符合软件无线电的宗旨。且满足各种体制雷达、电子测量系统和通信系统的指标要求,已经成功应用于某雷达系统中。

参考文献:

[1]何奕汕.相干快跳频系统关键技术研究[D].成都:电子科技大学,2015.

[2]黄志林.基于FPGA的并行DDS技术研究[J].现代电子技术,2013(7):54-56.

[3]邓钦耀.半实物直扩/跳频通信系统设计与实现[D].成都:电子科技大学,2012.