基于FPGA的倒立摆模糊PID控制器设计实现

郑浩 汪正祥 张凤登

摘要:在FPGA上设计部署模糊自适应PID算法,并针对典型的自动控制对象——直线倒立摆完成稳摆控制,以验证该算法的硬件可实现性。在直线倒立摆模型基础上,运用模糊控制理论对PID参数进行自适应整定,再根据模糊PID处理过程,结合离散PID算法,采用半查表加半计算方式,在Quartus II及Modelsim平台上完成Verilog HDL的硬件编程设计与仿真。通过Simulink仿真比较可知,模糊自适应PID相对于经典PID控制的响应性能指标更优,最后基于EP4CE6E22C8N芯片,以较少的资源开销实现了控制器设计。基于FPGA的模糊自适应PID控制器能够充分利用该器件特性,凸显模糊自适应PID算法優势,实现对倒立摆的实时控制。

关键词:FPGA;模糊PID控制;直线倒立摆

DOI:10.11907//rjdk.192050 开放科学(资源服务)标识码(OSID):

中图分类号:TP319文献标识码:A 文章编号:1672-7800(2020)006-0130-06

0 引言

倒立摆装置是控制理论研究中一种可靠的实验验证对象,直线型倒立摆一般由摆杆、电机以及角度传感器等组成,被广泛应用于科研及教学中,同时其系统模型与许多工业产品具有很大相似性。如今,智能控制理论快速发展,而倒立摆系统的不稳定、非线性、强耦合、多变量特点,使其成为新控制方法或理论的理想验证对象。李悟早等,充分讨论各种控制系统与模糊控制相结合的优点、缺点和适用范围,指出不同控制理论结合程度尚浅,因而各种控制理论深度融合是控制理论的发展方向之一。模糊PID(Proportion-Integral-DiffCrential)控制是复合控制理论的代表之一,即将模糊理论应用于PID参数整定。将其它智能控制理论,如粒子群优化算法等与PID控制相结合展开探究,文献实现了基于粒子群算法的倒立摆分数阶PID参数优化,PID传统整定方法有试凑法、齐格勒一尼科尔斯经验法等;传统PID控制已经得到广泛应用,佟远等使用MCU(Micro-Control Unit)完成PID双闭环旋转倒立摆设计,但对于一些复杂系统难以做到实时有效控制;卢雍卿等等也针对传统PID控制,在FPGA上实现了在液浮陀螺回路中的应用;白瑞林等总结出智能控制策略实现有两个显著特点:一是实时信息处理量远大于控制量,二是信息流往往具有实时并行性要求。而现场可编程逻辑门阵列(Field-Programmable Gate Array,FPGA)本质上屆于硬件数字逻辑电路,其一大设计特点就是“面积换取速度”,能够以硬件的大量并行工作替代软件的顺序指令执行。王利等分析指出,以往模糊逻辑控制应用基本依靠数字计算机或微处理器的软件计算模糊逻辑量,并通过查表完成逻辑推理。综合得出,FPGA相对于MCU等冯.诺依曼一哈佛体系的串行时序指令处理器而言,更适合部署智能控制策略。刘刚等在运用FPGA完成模糊自整定PID设计时,采用联合Matlab的离线计算在线查表设计方法;黄霞等同样使用该方法,对误差e和误差变化率ec在论域中的所有可能组合,按照模糊规则离线计算得出修正参数并存储到ROM中,再由查表方式进行解模糊化并输出修正参数,但这种方法需要较大的存储单元消耗。Boukhalfa等实现了模糊PID控制器在双星电磁电机直接转矩控制中的应用;Arulmozhiyal设计实现了基于FPGA的直流电动机模糊PID控制器。本文将模糊PID整定过程划分成不同模块,改进半查表加半计算使用策略,采用Verilog语言分别进行设计验证,消耗的硬件资源较少,并进行了整体时序验证仿真,最后基于EP4CE6E22C8N芯片搭配外围电路,完成了硬件模糊PID控制板设计。

1 模糊自适应PID控制器设计

1.1 模糊自适应PID控制原理

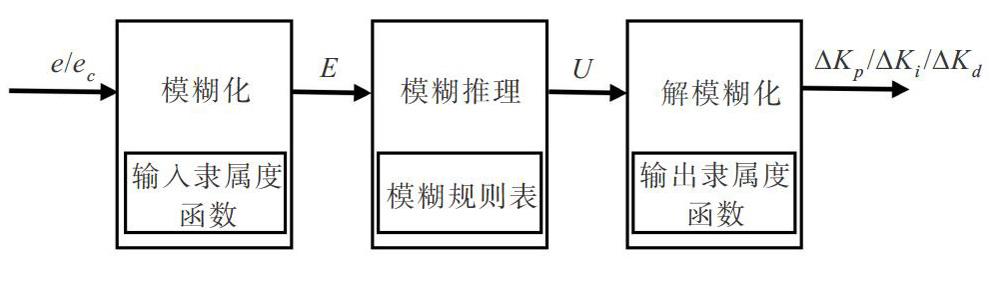

模糊自适应PID控制即将模糊理论与PID控制相结合,融合二者的原因主要是基于PID控制应用的广泛性,使一些原本经典PID控制无法胜任的场合也能得以应用。PID参数模糊自适应方法,可以很好地弥补经典PID控制的不足。本质还是PID控制,只是使用了模糊化方法对PID参数作实时优化。单纯的智能控制理论往往不具有确定性,经典或现代控制理论方法都须依靠精确的数学模型设计控制器,是确定的、收敛的设计方法。而模糊控制则是一种基于现实及经验策略的控制方法,属于智能控制理论,但需要在一定资源条件下才能够获得更出色的动态、静态性能。模糊控制过程可按处理过程分为模糊量化处理,按模糊控制规则作模糊决策、非模糊化处理等环节。模糊PID控制中的关键就是PID参数的模糊控制输出,因此将其分为输入变量模糊化、隶属值模糊推理、PID参数解模糊化3个阶段,如图l所示。

结合实际系统,首先将摆杆角度偏差及偏差变换率作为模糊输入,对其模糊化得到输入量的模糊子集,并计算其隶属度,再利用模糊规则表进行模糊推理,即对模糊矩阵表作查表处理,得出输出量的隶属值,最后解模糊计算得到PID参数的修正值。利用Verilog进行硬件逻辑设计也是按照这一过程进行功能模块划分。

1.2 倒立摆系统控制结构

整个控制器仍是基于PID控制,控制器可以看作由模糊PID推理和PID控制器两部分组成。控制器控制的对象就是直线一阶倒立摆,倒立摆系统控制结构如图2所示。

图2中模糊PID控制器的设定参考输入为θd,摆杆竖直为理想状态,考虑到角度传感器安装位置,θd大小为270°。反馈输入由倒立摆控制对象引出,即实时摆杆角度值θ。将二者之差作为系统误差e,并得到误差变化率ec(在离散情况下ec即当前误差与上次误差的差),最后将二者同时作为控制器的两个输入,根据离散PID公式得到控制输出,以直流电机的PWM占空比为输出,其中△Kp、△Ki、△Kd为模糊PID推理的输出。

1.3 模糊自适应PID控制器设计

控制器为双输入单输出,其中以摆杆角度与摆杆倾斜速度为输入,以电机控制参数(直流电机转速)为输出。根据工程实践,在此采用针对角度的闭环离散PID控制,为了平衡系统超调与响应速度,将初始PID值设为250、150、40,初始PID值选取对于倒立摆的最终性能有很大影响,也须通过反复实验确定。最终PID参数为Kp=Kp0+△Kp、ki=Ki0+△Ki、Kd=Kd0+AKd。位置式离散PID如式(1)所示。

u(k)=kp·e(k)+ki·∑e(k)+Kd·ec(k) (1)

首先需要确定各输人输出量论域,文献为了避免额外乘法操作消耗逻辑单元,将量化因子全部乘进论域中,在本文也是如此。其中,摆杆偏移角度范围为[-20°,+20°],选定输入范围既是下文系统模型线性化的要求,也是系统机械特性的实际要求,偏角过大时电机响应速度无法跟上。经过A/D转换后e范围为[-240,+240],并设摆角偏差变化率ec的范围为[-100,+100]、△Kp∈[-100,+100]、△Ki∈[-50,+50]、△Kd∈[-20,+20]。输入输出量均选择同样的模糊集{NB、NM、NS、ZO、PS、PM、PB},分别代表负大、负中、负小、零、正小、正中、正大,将原始量按论域划分后,分别对应到不同模糊子集,以少代多,就是模糊化的本质。对于计算隶属度的隶属函数,论域边缘采用Z型和S型,其余采用线性的三角形隶属函数。以输入e为例,隶属函数形式如图3所示。

在模糊控制过程中模糊推理是核心,模糊推理规则表是基于PID的整定经验而制定,PID各参数的作用可以简单总结为:以比例控制为PID控制的基础,即一般P是必需的,其与响应速度、超调均有关;积分控制I有助于减小稳态误差,提高稳定性,但可能增加超调量;微分控制D可加大惯性系统响应速度并减弱超调趋势,但与系统响应振荡关系密切。据此制定△Kp、△Ki、△Kd的模糊规则表,以△Kp为例,其模糊推理规则如表1所示。

2 单级倒立摆系统建模仿真

2.1 倒立摆系统数学建模

将倒立摆系统抽象为小车、摆杆组成的系统。在不考虑摩擦阻力情况下,分析受力并将其线性化,系统状态方程如下:

对式(3)进行拉氏变换并代人参数设定值,如表2所示,得到关于输入量u和输出角度量φ的传递函数。

2.2 控制系统Matlab仿真

首先在APP工具箱中找到Fuzzy Logic Designer,然后根据输入输出模糊子集新建模糊变量,再根据模糊规则表新建Rules,最后设置模糊推理采用Mamdani型,解模糊采用重心法。之后在Simulink中搭建系统模型,如图4所示。模糊自适应PID控制与常规PID控制阶跃响应曲线如图5所示,比较分析可以看出前者在超调量、响应时间等方面性能更优。

3 控制器在FPGA上的设计与实现

从FPGA应用顶层模块设计角度切人,即Top_Down设计概念。按照PID参数的模糊控制输出过程,使用Verilog HDL进行设计,同时利用Altera提供的免费IP核进行辅助设计。整个控制器内有误差处理模块、模糊处理模块(内部例化8个ROM模块)、PID运算控制模块(内部例化1个电机信号转换模块)共3个大模块。此外,还用了一个分频模块,用于提供全局需要的分频时钟,可以使用内部PLL完成。所有模块设计都是在RTL级别。

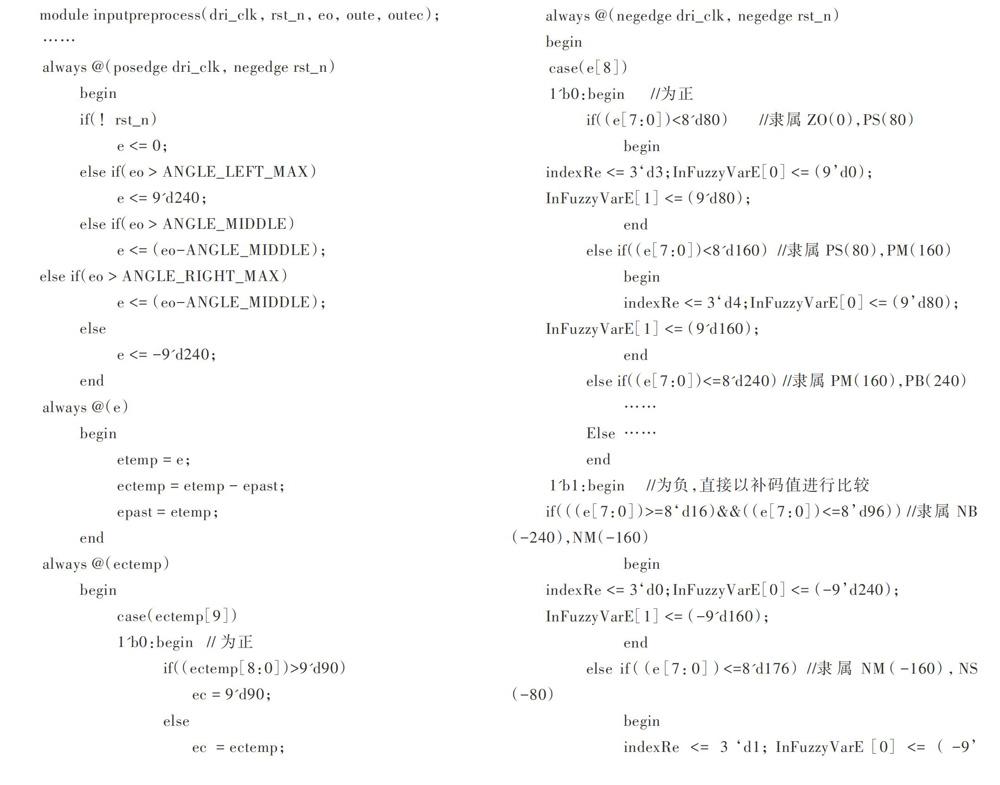

3.1 摆角误差处理模块设计

该模块输入为12位的A/D采样值,已知在竖直位置处A/D值为ANGLE_MIDDLE=12'd3115。经过该模块处理,输出9位有符号的oute和outec,主要代码如下所示。值得注意的是,Verilog中对于负数采取保存其补码形式。通过仿真验证,得到仿真时序图如图6所示。

3.2 模糊处理模块设计

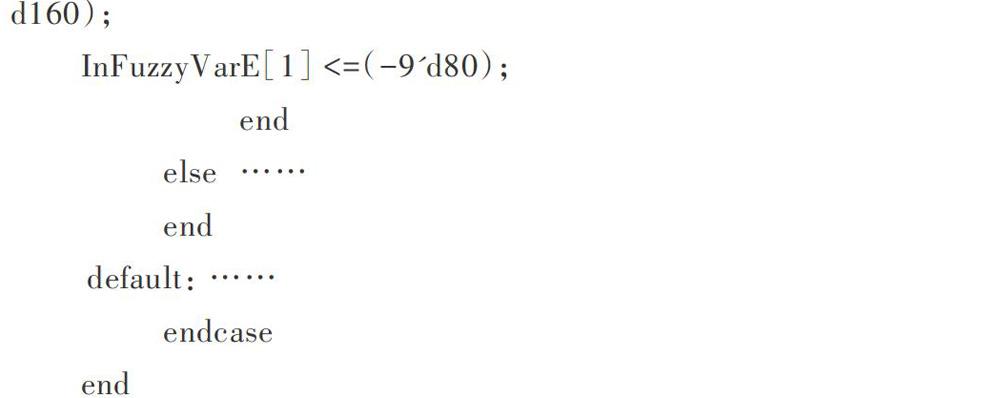

该模块是整个设计的核心,可分成模糊化块语句、模糊推理块、解模糊块语句。在模糊推理块中采用查表方式进行模糊推理,而在解模糊块语句中采用实时计算方式,也即使用半查表加半计算方式。对e模糊化主要代码如下所示,对ec处理类似。

上述代码的作用是对输入的数字量进行模糊化处理,即按照上文中的模糊论域划分,映射到对应的模糊子集。模糊推理块主要语句如下所示,主要作用是先计算关联模糊子集的隶属度。为了避免小数运算的产生,在此过程中均先作整数化处理,再生成查询储存在ROM中模糊规则表的行列坐标,并从ROM块中取出关联的模糊子集值。

进行解模糊计算并输出△Kp、△Ki、△Kd,再与初始设定的PID值相加。通过仿真验证,得到仿真时序图如图7所示。

3.3 PID运算控制模块设计

此目标控制的是直流电机,使用PWM的占空比变化控制电机转速。PID运算控制模块主要有计算电机转速值,以及PWM波发生模块。文献提供了一种根据输入脉冲频率生成特定PWM波的方式;Sabri等提出根据某特定输入量产生修正的输出占空比可调的PWM方法,说明在实际中使用PD控制已足够。通过仿真验证,得到仿真时序图如图8所示。

3.4 控制系统硬件设计

整个系统硬件以Ahera的EP4CE6E22C8N芯片为核心,其最小工作电路一般包括调试口、外围FLASH等,该FPGA芯片完全满足此次设计要求。外围电路包括电源电路、A/D转换电路、电机隔离驱动电路等。系统硬件设计如图9所示。

4 结语

本文采用一种半查表加半计算方式,基于Verilog语言进行倒立摆模糊PID控制器设计。对内部逻辑单位仅使用893/12060(7%),对内存bits的使用仅为3616/239616(2%),说明该设计具有经济性。不足之处在于,系统初始参数选择缺少方法总结,给运用带来一定不便,并且未针对更高阶倒立摆進行硬件设计,系统控制变量较少,无法完全突出模糊PID的优势。因此,未来可以结合模糊自适应PID控制,仍以FPGA为控制核心,运用于其它更复杂高阶倒立摆系统中。同时,该设计方法具有通用性,未来可方便用于其它控制场合。