基于FPGA的随机衰落及硬件实时统计实现

戴政 陈小敏 廖志忠 杨志强 朱秋明

摘要: 针对传统信道模型仅对多径衰落进行统计建模的问题, 建立了路径损耗、 阴影衰落、 莱斯(Rice)衰落和瑞利(Rayleigh)衰落等多种信道衰落模型, 提出并实现了一种基于现场可编程逻辑门阵列(Field-Programmable Gate Array, FPGA)的无线信道衰落实时模拟方法, 该方法可精确复现瑞利、 莱斯和阴影衰落等随机衰落。 在此基础上, 设计实现了一种硬件实时统计随机信号幅值分布的辅助方法。 硬件实测结果表明, 基于本文方法输出的信道衰落幅值分布、 硬件实时统计结果均与理论分布吻合, 有效验证了本文信道衰落模拟和硬件实时统计方法的有效性。 因此, 该方法可用于辅助模拟真实传播环境对无线信号的随机衰落影响。

关键词: 信道模型; FPGA; 幅值分布; 莱斯衰落; 阴影衰落

中图分类号: TN919文献标识码: A文章编号: 1673-5048(2020)02-0071-06

0引言

无线信号传播过程中由于受到各种信道因素影响, 导致无线通信系统传输质量不高。 构建符合实际的无线信道衰落模型, 对评估及测试通信系统具有重要意义[1]。 无线信道衰落硬件模拟可用于模拟无线信号在真实传播环境下的传播过程, 可缩短无线通信系统研究周期、 削减测试成本、 降低研发成本, 已成为评估及测试无线通信系统的重要组成部分[2-4]。

传统信道模型及硬件实现大多仅考虑多径衰落。 文献[5]提出了一种空时相关多天线的多径衰落信道硬件模拟方法; 文献[6]进行了瑞利和莱斯衰落的硬件实现, 但并未提及衰落时域相关性与衰落幅值分布; 文献[7]基于谐波叠加(Sum of Sinusoids, SoS) 原理设计了一种时域相关性可控的多径瑞利衰落信道模拟器。 目前, 信道衰落建模大多针对复合衰落信道。 文献[8]提出了一种复合衰落信道建模方法并进行了信道容量分析; 文献[9]提出了一种非平稳衰落信道仿真模型, 但并未涉及硬件实现。

本文在无线信道衰落理论模型基础上, 提出了一种易于FPGA实现的无线信道衰落硬件模拟方法。 给出信道衰落实现方案与硬件统计实现方案, 建立了阴影衰落、 莱斯和瑞利信道模型, 并进行了硬件实时复现及幅值分布实时统计。 该方法能够高效复现瑞利衰落、 莱斯衰落、 阴影衰落和路径损耗等信道影响因素, 可用于真实无线传播环境的实时模拟。

1系统方案

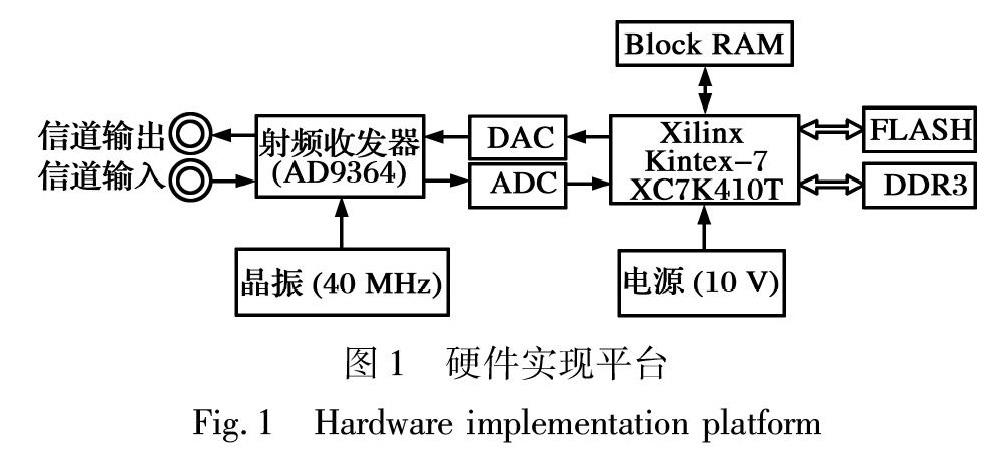

1.1硬件实现平台

本文信道模拟硬件平台如图1所示, 核心器件采用赛灵思公司(Xilinx)FPGA芯片Kintex-7 XC7K410T, 该芯片集成了500个最大单端输入/输出口, 10个时钟管理器模块, 795个块随机存取存储器(Block Random Access Memory, BRAM), 1 540个48位数字信號处理模块(Digital Signal Processing 48, DSP48); 内部集成了信道模块、 时钟模块、 外围接口模块及射频收发器模块。 外围电路包括电源、 晶振、 第三代双倍数据率存储器 (Double-Data-Rate Three, DDR3)、 射频收发器(AD9364)以及FLASH存储器等。

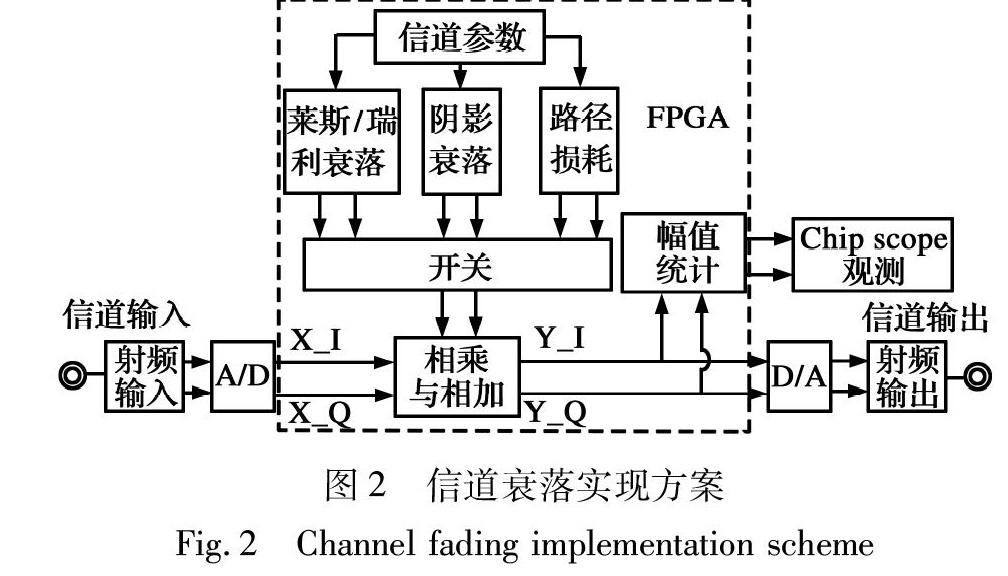

1.2总体实现方案

本文信道衰落模拟及幅值统计实现方案如图2所示。 首先从随机存取存储器(Random Access Memory, RAM)中读取信道参数分别产生莱斯/瑞利衰落、 阴影衰落和路径损耗, 通过拨码开关可选择任一随机衰落。 射频端接收输入信号后经模数转换为数字信号, 通过所选衰落信道, 最后经数模转换为模拟信号后由射频模块输出。 经过信道衰落后的信号可通过在线调试软件实时观测幅值分布情况。

1.3衰落理论分布

根据电磁波信号幅度在不同距离信道上或不同时间间隔内的变化快慢, 信道衰落有大尺度衰落和小尺度衰落之分。 大尺度衰落随距离(时间)变化而缓慢变化, 包含路径损耗和阴影衰落。 小尺度衰落随距离(时间)变化而快速变化, 包含瑞利衰落和莱斯衰落, 也称为多径衰落[10]。

莱斯及瑞利衰落硬件实现如图4所示。 首先, 从RAM中读取M+1个相位和频率值; 随后, 通过M+1个累加和相加运算后经过正弦和余弦查找表输出M+1个结果, 将M+1个结果分别进行累加、 加法及乘法运算后得到视距分量(t)和非视距分量(t), (t)即为瑞利衰落输出; 最后, 将(t)和(t)分别和系数kk+1和1k+1相乘, 并将两路输出结果相加输出即为莱斯衰落。

2.3硬件统计实现方案

硬件实时统计信号幅值分布克服了软件回传硬件数据造成的数据间断和无法统计大量的连续数据的问题, 且无需大量运算内存。 硬件上实现幅度分布的实时统计, 需要考虑幅度区间的合理分段及统计数据量的合理选取。 因此, 需要根据实际情况设定幅度区间数量和统计数据量。 假设随机信号幅度在[-A, A]之间随机变化且数量呈现一定的分布。 针对随机信号的幅度统计, 可将幅度范围[-A, A]分成n个等长的区段, 即[-A, A1),[A1, A2),…,[An-2, An-1), (An-1, A], 接着统计随机信号幅度落在各个区段的数量, 同时计算随机信号幅度的均值和方差, 并通过显示模块实时显示统计分布曲线, 然后将统计分布、 均值和方差等数据导出到Matlab软件进行权值转换处理, 并与理论分布对比, 分析误差。 理论上当n→∞时, 随机信号幅度统计分布与理论分布相同。

本文基于軟件无线电的思想, 将幅度分布实时统计模块化设计, 提供用户设定接口, 用户可以通过模块接口设计区间和统计数量, 增加了使用的灵活性和模块的可重复性, 使其更符合实际应用需要。 所设计的信号幅度分布实时统计方案如图5所示。 由用户接口控制、 实时统计存储和输出控制三部分构成。 用户接口控制部分实现了分布类型的选择和幅度位宽、 幅度分段及统计长度的设置。 用户接口控制部分输出及输入信号通过实时统计存储部分幅度统计和均值方差统计等工作后, 进行数据存储, 最后由输出控制部分显示并输出数据。

3硬件实测及验证

3.1硬件资源消耗

硬件系统中产生信道衰落是最消耗FPGA资源的部分。 以上行数据链路为例, 每一路数据都需要通过正弦/余弦查找表产生多路正弦/余弦信号。 考虑到信号采样率远大于实际场景中的信道衰落采样率, 本文采用时分复用的思想进行设计。 该方案包括查找表模块、 寄存器模块、 参数存储RAM模块、 信道参数模块、 数字信号处理模块、 输入全局缓冲模块和内插模块。 其中, 查找表模块用于生成下行数据链路, 通过映射关系可大大降低存储容量; RAM模块用来存储多张正弦/余弦表; 信道参数模块实现信道参数的线性内插以及积分计算; 数字信号处理模块用于与FPGA之间的实时通信; 全局缓冲模块用于全局时钟输入管脚相连接的首级全局缓冲; 内插模块用于将低速率原始信道衰落内插至系统速率。 同时, 累加计算部分也会消耗大量寄存器资源用于存储中间状态。 本文硬件系统实现的是单径信道衰落输出, 理论上单片芯片可完成4×4多输入多输出 (Multiple-Input Multiple-Output, MIMO)信道实时模拟, 故可满足真实场景中信道衰落的实时模拟。 整个信道衰落系统资源消耗如表1所示。

3.2实测结果及验证

本文基于赛灵思公司Kintex-7 FPGA硬件实现平台对莱斯衰落和阴影衰落信道输出波形及幅值分布进行了设计实现及验证。 首先输入1 MHz单音信号进行测试, 可通过拨码开关设置莱斯衰落和阴影衰落, 利用示波器可观测测试信号通过信道前后波形变化, 通过硬件实时统计幅值分布并通过在线调试软件观测其分布的变化。

图6给出了1 MHz单音测试信号通过莱斯衰落信道和阴影衰落信道后输出波形的变化情况。 由图6(b)~(c)可见, 信号经衰落后包络呈现出明显的起伏变化。 图7给出了对应衰落的理论分布和硬件实测输出幅值分布统计结果。 由图可以看出, 实测结果与理论值吻合, 莱斯因子k越大, 波形的起伏越小, 阴影衰落对波形的起伏影响与σ有关, σ越大, 波形起伏越大。

4结论

本文针对多种不同信道衰落的硬件模拟实现问题, 设计并实现了一种基于FPGA的硬件复现及实时统计的信道衰落模拟器。 硬件实测结果表明, 该方法输出信道衰落幅值分布与理论值吻合, 验证了本文模拟方法的正确性, 可在实验室模拟真实传播环境下无线信号的随机失真影响。

参考文献:

[1] 邵晖.高性能信道模拟器设计与应用浅析[J].国外电子测量技术, 2017, 36(3): 4-9.

Shao Hui.Design and Application of High Performance Channel Simulator[J].Foreign Electronic Measurement Technology, 2017, 36(3): 4-9.(in Chinese)

[2] Gutierrez C A, Patzold M.The Design of SumofCisoids Rayleigh Fading Channel Simulators Assuming NonIsotropic Scattering Conditions[J].IEEE Transactions on Wireless Communications, 2010, 9(4): 1308-1314.

[3] 费丹, 熊磊, 吴建强.基于软件无线电的无线信道仿真仪设计与实现[J].仪器仪表学报, 2013, 34(12): 93-98.

Fei Dan, Xiong Lei, Wu Jianqiang.The Design and Implementation of Radio Channel Emulator Based on Software Defined Radio System[J].Chinese Journal of Scientific Instrument, 2013, 34(12) : 93-98.(in Chinese)

[4] 任海玉, 高翔, 闫毅, 等.基于虚拟仪器的深空信道仿真器的设计与实现[J]. 电子测量技术, 2010, 33(3): 89-92.

Ren Haiyu, Gao Xiang, Yan Yi, et al.Design and Implementation of Deep Space Channel Simulator Based on Virtual Instrument[J].Electronic Measurement Technology, 2010, 33(3): 89-92.(in Chinese)

[5] Alimohammad A, Fard S F.FPGA Implementation of Isotropic and Nonisotropic Fading Channels[J].IEEE Transactions on Circuits and Systems, 2013, 60(11): 796-800.

[6] Alimohammad A, Fard S F, Cockburn B F.Hardware Implementation of Rayleigh and Ricean Variate Generators[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2011, 19(8): 1495-1499.

[7] 陸许明, 戴建强, 谭洪舟.高效的多径衰落信道仿真及其硬件实现[J].系统仿真学报, 2014, 26(1): 197-201.

Lu Xuming, Dai Jianqiang, Tan Hongzhou.Efficient Emulation of Multipath Fading Channels and Its Hardware Implementation[J].Journal of System Simulation, 2014, 26(1): 197-201.(in Chinese)

[8] 朱秋明, 戴秀超, 刘星麟, 等.复合衰落信道建模及模拟方法研究[J].信号处理, 2015, 31(1): 59-65.

Zhu Qiuming, Dai Xiuchao, Liu Xinglin, et al.Modeling and Simulation for Composite Fading Channel[J].Journal of Signal Processing, 2015, 31(1): 59-65.(in Chinese)

[9] Zhu Qiuming, Liu Xinglin, Yin Xuefeng, et al. A Novel Simulator of Nonstationary Random MIMO Channels in Rayleigh Fading Scenarios[J].International Journal of Antennas and Propagation, 2016: 1-9.

[10] Ptzold M.Mobile Radio Channels[M].2nd ed. Beijing: China Machine Press, 2014.

[11] Zhu Qiuming, Li Hao, Fu Yu, et al.A Novel 3D NonStationary Wireless MIMO Channel Simulator and Hardware Emulator[J].IEEE Transactions on Communications, 2018, 66(9): 3865-3878.

[12] 陆戈辉, 李华, 潘明海.射频仿真系统中三元组合成信号幅度特性研究[J].航空兵器, 2018(5): 63-67.

Lu Gehui, Li Hua, Pan Minghai. Research of Synthetic Signal Amplitude Characteristics of the ThreeRadiatingUnit Array in Radio Frequency Simulation System[J].Aero Weaponry, 2018(5): 63-67.(in Chinese)

[13] 周生奎, 朱秋明, 吕卫华, 等.基于FPGA的航空数据链信道模拟器[J].航空兵器, 2014(1): 61-64.

Zhou Shengkui, Zhu Qiuming, Lü Weihua, et al.A New Channel Emulator for Aerospace Data Link Based on FPGA[J].Aero Weaponry, 2014(1): 61-64.(in Chinese)

[14] Fard S F, Alimohammad A, Cockburn B F.An FPGABased Simulator for High Path Count Rayleigh and Rician Fading[J].IEEE Transactions on Vehicular Technology, 2010, 59(6): 2725-2734.

Abstract: Aiming at the problem that the traditional statistical channel models only focus on multipath fading, a composite channel fading model including path loss, shadow fading, Rice fading and Rayleigh fading is established. Meanwhile, a realtime simulation method for wireless channel fading based on the fieldprogrammable gate array (FPGA) is proposed, which can accurately reproduce random channel fading such as Rayleigh, Rice and shadow fading. On this basis, a new method for realtime statistical random signal amplitude distribution is designed and implemented. The hardware measured results show that the output amplitude distribution of channel fading and hardware realtime statistical results are consistent with the theoretical distribution, which validates the effectiveness of the channel fading simulation and the hardware realtime statistical method. Thus, it is very helpful to simulate the random fading effect of real propagation environment on wireless signal.

Key words: channel model; FPGA; amplitude distribution; Rice fading; shadow fading